Module 4

Memory and I/O Interfacing

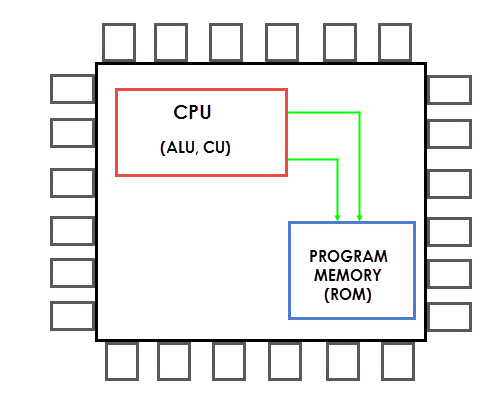

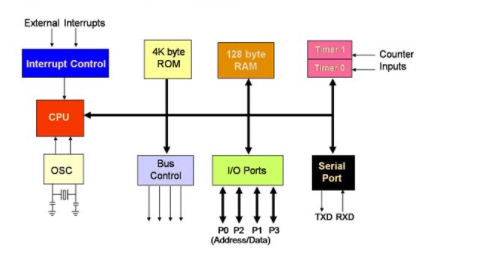

The 8051 Microcontroller Memory is separated into Program Memory (ROM) and Data Memory (RAM). The Program Memory of the 8051 Microcontroller is used for storing the program to be executed, which means instructions. The Data Memory is used for storing temporary variable data and intermediate results.

Program Memory (ROM) of 8051

The code or instructions which are to be executed are stored in the Program Memory, also called as the ROM of the Microcontroller.

Program Memory

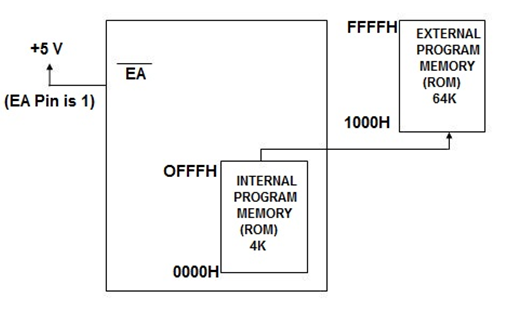

In 4KB Internal ROM, the address space is 0000H to 0FFFH. If the program addresses exceed this value,the CPU will automatically fetch the code from the external Program Memory.

For External Access (EA Pin) must be pulled HIGH at this condition the CPU first fetches instructions from the Internal Program Memory in the address range of 0000H to 0FFFFH .If it exceeds the memory addresses limit, instructions are fetched from external ROM in address range of 1000H to FFFFH.

External access

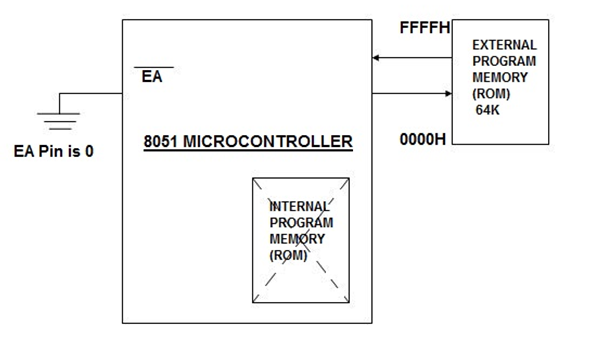

There is also an alternative method to fetch the instructions where the Internal ROM is ignored and instructions are fetched only from External Program Memory(External ROM).

For this purpose, the EA pin must be connected to GND. The memory addresses of external ROM will be from 0000H to FFFFH.

External Program Memory

Data Memory (RAM)

▪ Data Memory or RAM stores temporary data and intermediate results generated during the normal operation of the microcontroller.

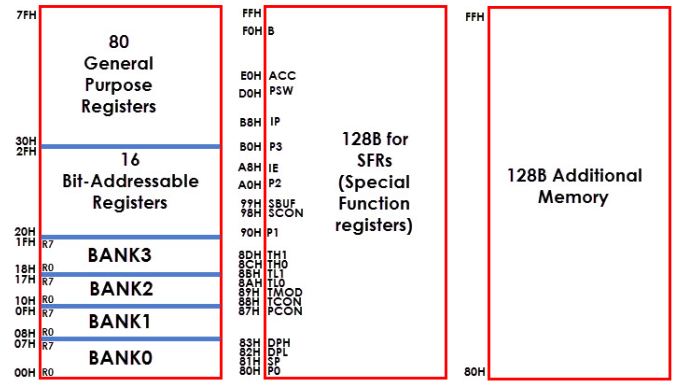

▪ Currently, 8051 Microcontroller has 256B of RAM. The first 128B memory addresses from 00H to 7FH are divided into Working Registers. They are organized as Register Banks, Bit – Addressable Area and General Purpose RAM known as Scratchpad area.

▪ The first 128B of RAM (from 00H to 7FH), the first 32B of memory from addresses 00H to 1FH consists of 32 Working Registers organized into four banks with 8 Registers in each Bank.

Lower 128B(00H to 07H) Upper 128B(80H-FFH)

(Direct and Indirect Addressing) (Direct Addressing) (Indirect Addressing)

▪ The 4 banks are named as Bank0, Bank1, Bank2 and Bank3. Each Bank consists of 8 registers R0 – R7. Each Register can be addressed either by name or by address.

▪ To address the register by name, first the corresponding bank is selected. In order to select the bank, RS0 and RS1 bits of the Program Status Word (PSW) and Register (RS0 and RS1 are 3rd and 4th bits in the PSW Register) are used.

▪ When addressing these Register for example 12H the corresponding bank may or may not be selected. (12H corresponds to R2 in Bank2).

▪ The next 16B of the RAM that is from 20H to 2FH are Bit – Addressable memory locations. A total of 128 bits can be addressed individually using 00H to 7FH or an entire byte can be addressed as 20H to 2FH.

▪ The final 80B of the internal RAM addresses are from 30H to 7FH which is the general-purpose RAM area that is byte addressable.

▪ These lower 128B of RAM can be addressed directly or indirectly.

I/O Expansion buses:

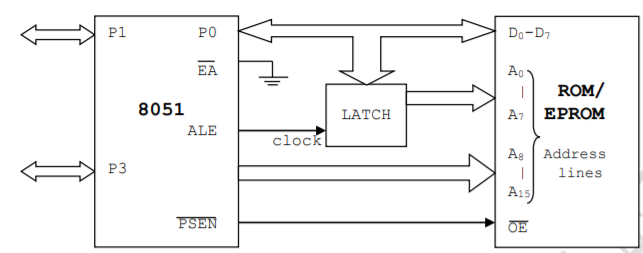

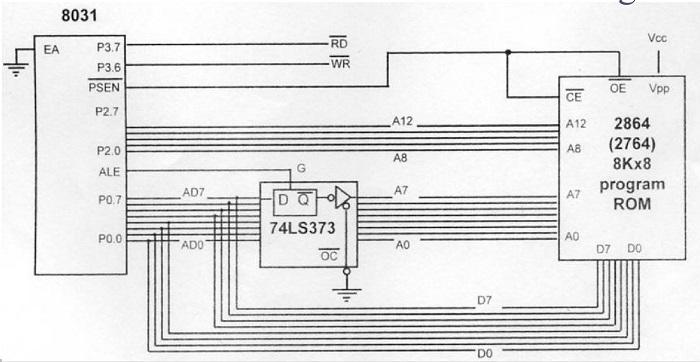

The above figure shows how to access or interface ROM to 8051.

Port 0 is used as multiplexed data & address lines. It gives lower order (A7-A0) 8 bit address in initial T cycle & higher order (A8-A15) used as data bus.

8- bit address is latched using external latch & ALE signal from 8051.

Port 2 provides higher order (A15-A8) 8 bit address.

PSEN is used to activate the output enable signal of external ROM/EPROM.

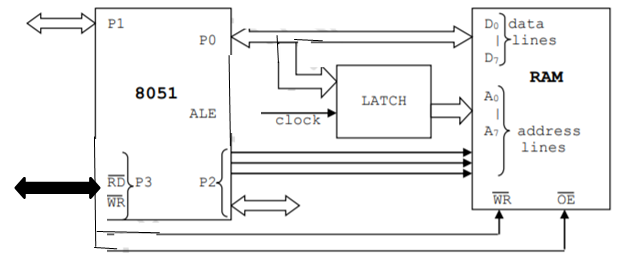

Ii. External RAM (data memory) Interfacing

The above figure shows how to connect or interface external RAM(data memory) to 8051. Port 0 is used as multiplexed data & address lines. Address lines are decoded using external latch & ALE signal from 8051 to provide lower order (A7-A0) address lines. Port 2 gives higher order address lines. RD & WR signals from 8051 select the memory read & memory write operations respectively.

Control Signals

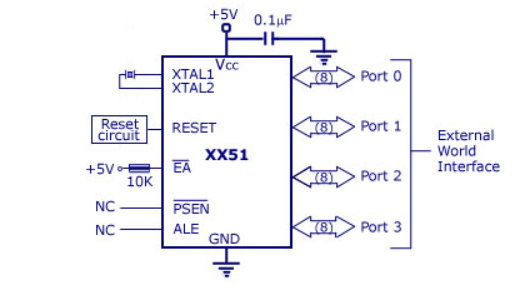

There are 3 control signals, EA, PSEN and ALE. These signals are known as External Access (EA), Program Store Enable (PSEN), and Address Latch Enable (ALE) which is used for external memory interfacing.

The control signals are used for external memory interfacing. If there is no requirement of external memory interfacing then, EA pin is pulled high, that is it is connected to Vcc and two others PSEN and ALE are left alone. To avoid HF oscillations 0.1 micro farad decoupling capacitor connected to Vcc at the input.

There are four ports numbered 0,1,2,3 and called as Port 0, Port 1, Port 2 and Port 3 which are used for external interfacing of devices like DAC, ADC, 7 segment display, LED etc. Each port has 8 I/O lines which are bit programmable.

Memory wait states.

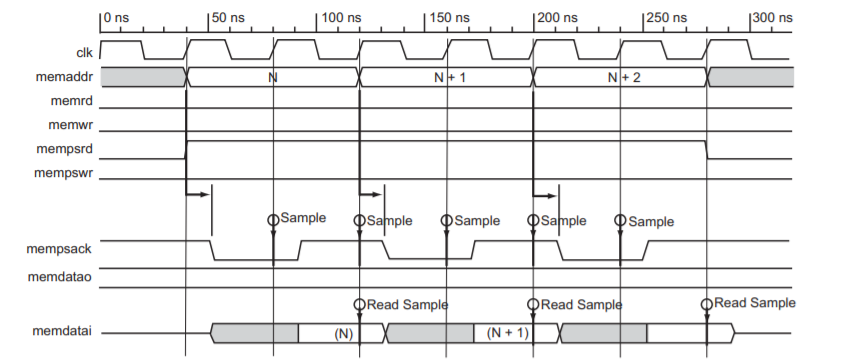

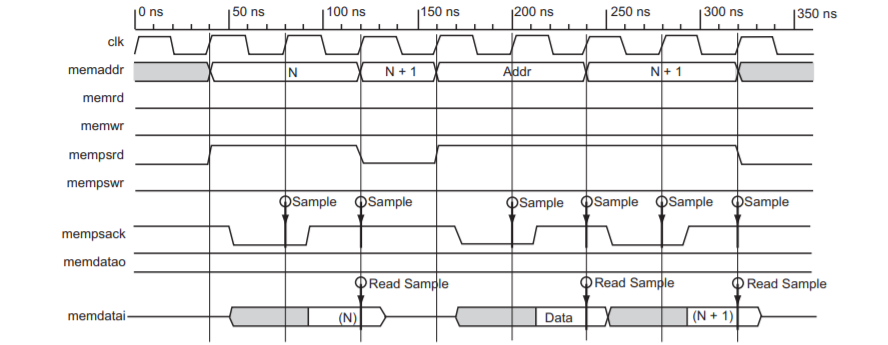

● Program Memory Wait States

Program Fetch Cycle with wait state

Program Memory Read cycle with wait state

Interfacing is one of the important concepts in microcontroller 8051 because a microcontroller is a CPU that can perform some operation on the data and gives the output.

However, to perform the operation we need an input device to enter the data and in turn output device displays the results of the operation.

Microcontroller Peripherals Devices

Interfacing is the process of connecting devices together so that they can exchange the information and that proves to be easier to write the programs.

There are different type of input and output devices for our requirement such as LEDs, LCDs, 7segment, keypad, motors and other devices.

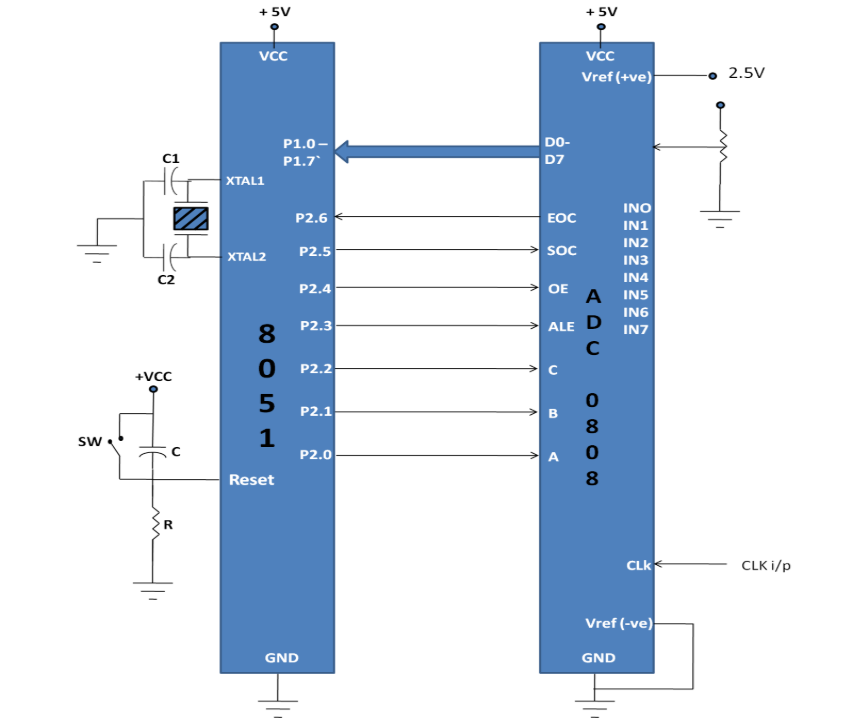

ADC0808/0809:

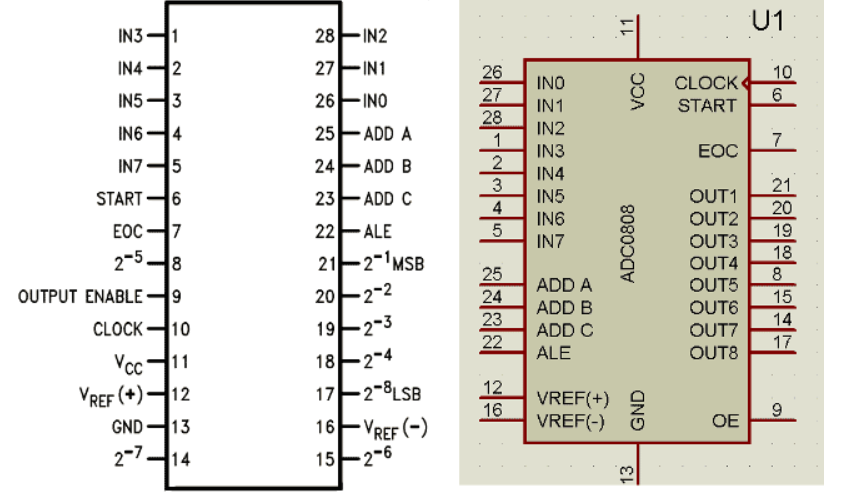

ADC0808/0809 is a monolithic CMOS device which consists of 28 pins and gives 8-bit value in output for 8- channel ADC input pins (IN0-IN7).

It has a resolution of 8 therefore it can encode the analog data into one of the 256 levels (28).

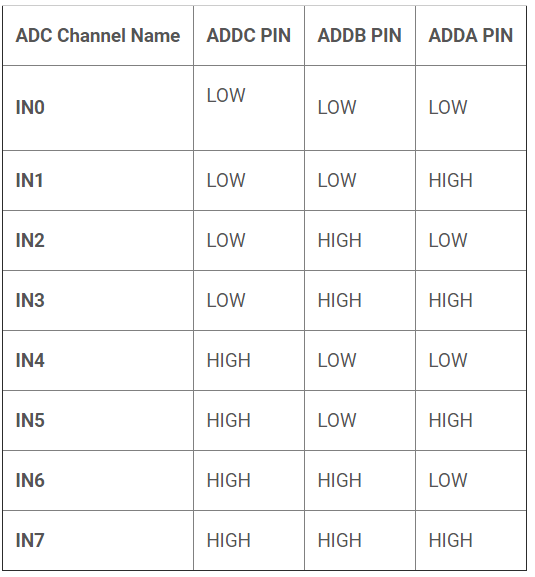

It has three channel address lines namely: ADDA, ADDB and ADDC to select channels.

Pin Diagram for ADC0808

Figure 5. ADC 0808 Pin

ADC0808/0809 needs a clock pulse for conversion which can be provided by using an oscillator or microcontroller.

Select the input channel using address lines, like the input line IN0 by keeping all three address lines (ADDA, ADDB,ADDC) low.

Suppose IN2 is selected to keep ADDA and ADDB low and ADDC high.

Figure 13. Channel selection

SOC [Start of conversion]:

When High to low signal is appears on the pin of ADC, and ADC starts conversion

Figure 6. SOC

EOC [End of conversion]:

To indicate completion of conversion ADC sends a high EOC signal to the microcontroller .

OE [Output Enable]:

When a high signal is applied to this pin, the output latch of ADC is enabled and the converted data is made available to the Microcontroller.

The reference voltage determines the range of analog input voltage.

For example: - If reference voltage is 5V then analog voltage ranges from 0V-5V. If the reference voltage is 2.56V then the range is from 0V-2.56V.

The frequency of the applied clock signal determines conversion speed.

Working:

⮚ Initially, microcontroller provides a 500 KHz clock signal to ADC0808 because the Timer 0 interrupt requires clock signal to operate to operate as ADC.

⮚ Then the microcontroller sends a LOW to HIGH level signal to ALE pin (active-high pin) of ADC0808 to enable the latch in the address.

⮚ By applying HIGH to LOW Level signal to SC (Start Conversion), ADC starts analog to digital conversion. And then wait for the EOC (End of Conversion) pin to go LOW.

⮚ When EOC goes LOW, it means analog to digital conversion has been completed and data is ready to use.

⮚ After this, the microcontroller enables the output line by applying a HIGH to LOW signal to the OE pin of ADC0808.

⮚ ADC0808 gives ratio metric conversion output at its output pins.

Radiometric conversion is given by

Vin/(Vfs – Vz) = Dx / (Dmax – Dmin)

Where:

Vin is input voltage for conversion

Vfs is full scale voltage

Vz is zero voltage

Dx is data point being measured

Dmax is maximum data limit

Dmin is the minimum data limit.

Interfacing Diagram:

Figure 7. Interfacing 8051 with ADC0808

Program:

SOC EQU P2.6

EOC EQU P2.5

OE EQU P2.4

ALE EQU P2.3

ADDR_C EQU P2.2

ADDR_B EQU P2.1

ADDR_A EQU P2.0

ORG 0000H

MOV P1, #0FFH

SETB P2.5

CLR SOC

CLR OE

CLR ALE

AGAIN: CLR ADDR_C

CLR ADDR_B

CLR ADDR_A

SETB SOC

SET ALE

ACALL DELAY

CLR SOC

CLR ALE

BACK: JB EOC BACK

HERE: JNB EOC HERE

SETB OE

MOV A,P1

ACALL CONVERSION

ACALL DISPLAY

AGAIN: SJMP AGAIN

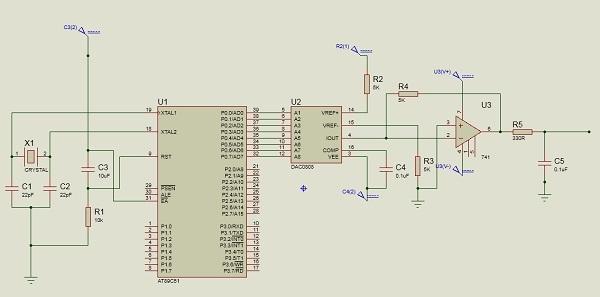

The Digital to Analog converter (DAC) is a device used for converting digital pulses to analog signals.

There are two methods of converting digital signals to analog signals which are inary weighted method and R/2R ladder method.

The MC1408 (DAC0808) Digital to Analog Converter uses the R/2R ladder method. This method can achieve a higher degree of precision. DACs are judged by its resolution., If there are n digital input pins, there are 2n analog levels. So, 8 input DAC has 256 discrete voltage levels.

MC1408 DAC (or DAC0808)

In this chip the digital inputs are converted to current. The output current is known as Iout by connecting a resistor to the output to convert into voltage.

The total current provided by Iout pin is basically a function of binary numbers at the input pins D0 - D7 (D0 is the LSB and D7 is the MSB) of DAC0808 and the reference current Iref.

The following formula is showing the function of Iout

Iout=Iref⟮D7/2+D6/4+D5/8+D4/16+D3/32+D2/64+D1/128+D0/256⟯

The Iref is the input current. This must be provided into the pin 14. Generally 2.0mA is used as Iref

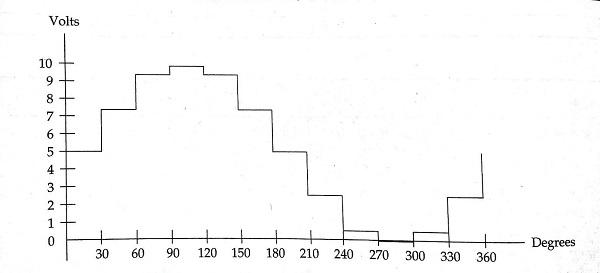

Generating Sinewave using DAC and 8051 Microcontroller

For generating sinewave first we need a look-up table to represent the magnitude of the sine value of angles between 0° to 360°. The sine function varies from -1 to +1.

In the table only integer values are applicable for DAC input. In this example we will consider 30° increments and calculate the values from degree to DAC input. We are assuming a full-scale voltage of 10V for DAC output.

We can follow this formula to get the voltage ranges.

Vout = 5V + (5 x sin θ)

The lookup table according to the angle and other parameters for DAC.

Angle(in θ ) | Sinθ | Vout (Voltage Magnitude) | Values sent to DAC |

0 | 0 | 5 | 128 |

30 | 0.5 | 7.5 | 192 |

60 | 0.866 | 0.866 | 9.33 |

90 | 1.0 | 1.0 | 10 |

120 | 0.866 | 0.866 | 9.33 |

150 | 0.5 | 0.5 | 7.5 |

180 | 0 | 0 | 5 |

210 | -0.5 | -0.5 | 2.5 |

240 | -0.866 | -0.866 | 0.669 |

270 | -1.0 | -1.0 | 0 |

300 | -0.866 | -0.866 | 0.669 |

330 | -0.5 | -0.5 | 2.5 |

360 | 0 | 0 | 5 |

Angle(in θ ) | Sinθ | Vout (Voltage Magnitude) | Values sent to DAC |

0 | 0 | 5 | 128 |

30 | 0.5 | 7.5 | 192 |

60 | 0.866 | 9.33 | 238 |

90 | 1.0 | 10 | 255 |

120 | 0.866 | 9.33 | 238 |

150 | 0.5 | 7.5 | 192 |

180 | 0 | 5 | 128 |

210 | -0.5 | 2.5 | 64 |

240 | -0.866 | 0.669 | 17 |

270 | -1.0 | 0 | 0 |

300 | -0.866 | 0.669 | 17 |

330 | -0.5 | 2.5 | 64 |

360 | 0 | 5 | 128 |

Circuit Diagram −

Source Code

#include <reg51.h>

Sfr DAC = 0x80; // Port P0 address

Void main()

{

Int sin value[12] = {128,192,238,255,238,192,128,64,17,0,17,64};

Int i;

While(1){

// infinite loop for LED blinking

For(i=0;i<12;i++)

{

DAC = sin_value[i];

}

}

}

Output

The output will look like this −

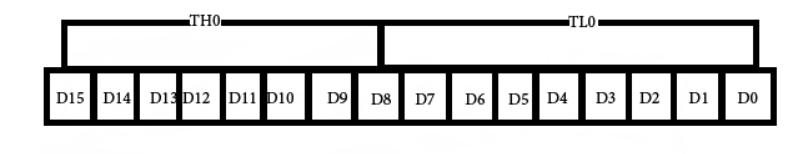

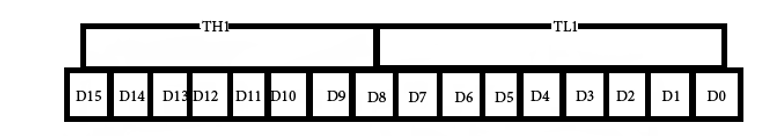

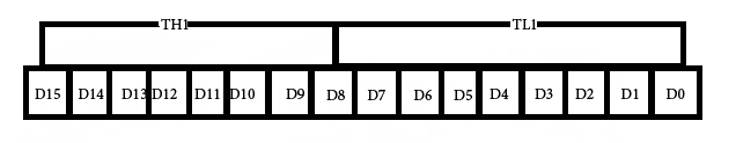

The 8051 has two timers: timer0 and timer1. Both timers are 16 bits wide. Since the 8051 has an 8-bit architecture, each 16-bit is accessed as two separate registers of low byte and high byte.

Timer0 registers is a 16- bits register which is accessed as low byte and high byte. The low byte is TL0 and the high byte is TH0.

These registers are accessed like any other registers where the 16-bits register is accessed as low byte and high byte. The low byte is TL0 and the high byte is TH0.

Timer 0

Timer1 registers is also a 16- bit register and is split into two bytes referred to as TL1 and TH1.

Timer 1

TMOD (timer mode) Register: This is an 8-bit register which is used by both timers 0 and 1 to set the various timer modes. In this TMOD register, lower 4 bits are set aside for timer0 and the upper 4 bits are for timer1. The lower 2 bits are used to set the timer mode and upper 2 bits to specify the operation.

In upper or lower 4 bits, the first bit is a GATE bit. Every timer has a means of starting and stopping. Some timers do this by software, some by hardware, and some have both software and hardware controls. The hardware way of starting and stopping the timer by an external source is achieved by making GATE=1 in the TMOD register. And if we change to GATE=0 then we do not need external hardware to start and stop the timers.

The second bit is the C/T bit which is used to decide whether a timer is used as a time delay generator or an event counter. If this bit is 0 then it is used as a timer and if it is 1 then it is used as a counter.

In upper or lower 4 bits, the last bits third and fourth are known as M1 and M0 respectively. These are used to select the timer mode.

M0 | M1 | Mode | Operating Mode |

0 | 0 | 0 | 13-bit timer mode, 8-bit timer/counter THx and TLx as 5-bit prescalar. |

0 | 1 | 1 | 16-bit timer mode, 16-bit timer/counters THx and TLx are cascaded; There are no prescalar. |

1 | 0 | 2 | 8-bit auto reload mode, 8-bit auto reload timer/counter; THx holds a value which is to be reloaded into TLx each time it overflows.

|

1 | 1 | 3 | Split timer mode.

|

Mode 1- It is a 16-bit timer which allows values from 0000 to FFFFH to be loaded into the timer’s registers TL and TH. After TH and TL are loaded with 16-bit initial value, the timer is started.

“SETB TR0” for timer 0 and “SETB TR1” for timer 1.

After the timer is started. It starts counting up until it reaches its limit of FFFFH. When it rolls over from FFFF to 0000H, it sets a high flag bit called TF (timer flag). This timer flag can be monitored.

When this timer flag is raised, one option is to stop the timer with the instructions “CLR TR0“ or CLR TR1 for timer 0 and timer 1 respectivel .After the timer reaches its limit and rolls over to repeat the process the registers TH and TL must be reloaded with the original value and TF must be reset to 0.

Mode0- Mode 0 is exactly the same as mode 1 except that it is a 13-bit timer instead of 16-bit. The 13-bit counter can hold values between 0000 to 1FFFH in TH-TL. Therefore, when the timer reaches its maximum of 1FFH, it rolls over to 0000, and TF is raised.

Mode 2- It is 8- bit timer that allows only values of 00 to FFH to be loaded into the timer’s register TH. After TH is loaded with 8- bit value 8051 gives a copy of it to TL. Then the timer must be started.

The instruction “SETB TR0” for timer 0 and “SETB TR1” for timer1.

This is like mode 1. After the timer is started it starts to count up by incrementing the TL register. It counts till it reaches the limit of FFH.

When it rolls over from FFH to 00. It sets high the TF (timer flag).

If we are using timer 0, TF0 goes high;

If using TF1 then TF1 is raised.

When Tl register rolls from FFH to 00 and TF is set to 1, TL is reloaded automatically with the original value kept by the TH register. To repeat the process, clear TF .This makes mode 2 auto reload, in contrast to mode 1 in which the programmer has to reload TH and TL.

Mode3- Mode 3 is also known as a split timer mode. Timer 0 and 1 may be programmed to be in mode 0, 1 and 2 independently of similar mode for other timer. This is not true for mode 3; timers do not operate independently if mode 3 is chosen for timer 0. Placing timer 1 in mode 3 causes it to stop counting; the control bit TR1 and the timer 1 flag TF1 are then used by timer0.

Internal Program Memory (4KB) 0000H to 0FFFH

External Program Memory (60KB) from 1000H to FFFFH.

We can select this mode by making EA = 1.

Total External Program Memory (64KB) that is over the entire range of 0000H to FFFFH. We can select this mode by making EA = 0.

The external storage is addressed and accessed via I/O ports P0 and P2. In 8051, the PSEN = 1 (is active) when reading a byte from external program memory (ROM).

The command used to access external ROM is,

MOVC A, @A+DPTR

When we connect PSEN to the ground, then 8051 microcontroller fetches the opcode from the external ROM.

But, when we connect PSEN to VCC, the status of the PSEN is ‘not activated’ since it is an active low pin. Hence, the program memory is saved in the internal ROM of 8051 itself.

Circuit diagram to interface external program ROM with 8051

Step 1: Connect EA pin to ground

Step 2: Connect the PSEN to the CE and OE.

Step 3: Then, Port 2 (P2.0 – P2.7) to A8 – A12 pins of ext. ROM.

Step 4: Connect ALE to G of 74LS373 latch to enable it.

Step 5: Next, connect the OC of 74LS373 to GND.

Step 6: Connect Port 0 (P0.0 – P0.7), which consists of both address and data multiplexed into Port 0 to 1D – 8D pins of 74LS373 latch to demultiplex it and 1Q – 8Q of the latch to A0 – A7 of ext. ROM.

Step 7: Connect Port 0 (P0.0 – P0.7) to D0 – D7 of the ext. ROM.

Step 8: VPP of ext. ROM to VCC.

Here, 8Kx8 means that program ROM is organized in a structure that has an 8K word space and the x8 means that each word is 8 bits. This means that 32Kx8 would be a ROM which has a 32K word space, at 8-bits per word. In other words, this means that there are 32,000 locations that are 8-bit wide.

The Program and Data Memory can be of the size 1Kx8, 2Kx8, 4Kx8, 8Kx8, 16Kx8, 32Kx8, and 64Kx8. Also, multiple chips of smaller sizes cascade together to form a chip of larger size hence we can connect two 16Kx8 data RAM chips to form one 32Kx8 data RAM. If we take 32Kx8, then 2^15 = 32K, which implies 15 address lines and x8 implies 8 data lines.

References:

❖ 8051 Microcontroller: An Applications Based Introduction Book by David Calcutt, Frederick J. Cowan, and Hassan Parchizadeh

❖ 8051 Microcontrollers: Internals, Instructions, Programming, and Interfacing Book by Subrata Ghoshal

❖ C and the 8051: Building efficient applications Book by Thomas W. Schultz

❖ MICROCONTROLLER Book by V. Udayashankara

❖ The 8051/8052 Microcontroller: Architecture, Assembly Language, and Hardware Interfacing Book by Craig Steiner