Unit - 2

16-bit Microprocessor Instruction set and Assembly Language Programming

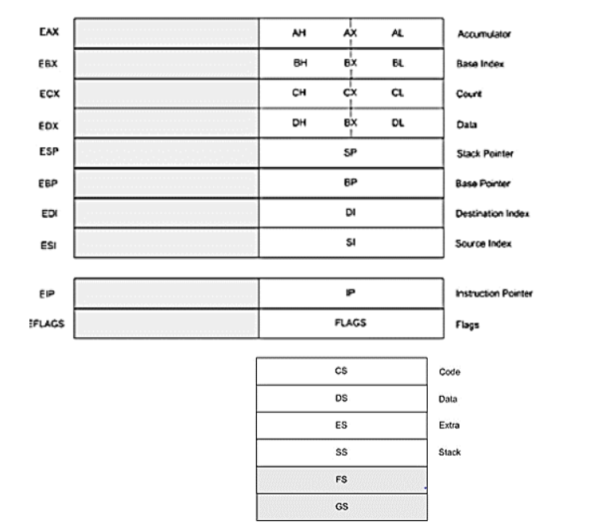

The programming model of the 8086 is considered to be program visible because its registers are used during application programming and are specified by the instructions. Figure below illustrates the programming model of 8086 microprocessor.

Some registers are general-purpose or multipurpose registers, while some have special purposes. The multipurpose registers include EAX, EBX, ECX, EDX, EBP, EDI, and ESI. These registers hold various data sizes (bytes, words, or double words) and are used for almost any purpose, as dictated by a program.

The programming model of the microprocessor

Multipurpose Registers

EAX (accumulator)

EBX (base index)

ECX (count)

EBP (base pointer)

EDI (destination index)

ESI (source index)

Special-purpose Registers.

The special-purpose registers include EIP, ESP, EFLAGS; and the segment registers CS, DS, ES, SS, FS, and GS.

EIP (instruction pointer)

ESP (stack pointer)

EFLAGS

C (carry)

P (parity)

A (auxiliary carry)

Z (zero)

S (sign)

T (trap)

I (interrupt)

D (direction)

O (overflow)

IOPL (I/0 privilege level)

NT (nested task)

RF (resume)

VM (virtual mode)

AC (alignment check)

VIF (virtual interrupt flag)

VIP (virtual interrupt pending)

ID (identification)

Segment Registers

Additional registers, called segment registers, generate memory addresses when combined with other registers in the microprocessor. Following is a list of each segment register, along with its function in the system:

CS (code)

DS (data)

ES (extra)

SS (stack)

FS and GS

Operand types:

REG: AX, BX, CX, DX, AH, AL, BL, BH, CH, CL, DH, DL, DI, SI, BP, SP.

SREG: DS, ES, SS, and only as second operand: CS.

memory: [BX], [BX+SI+7], variable, etc

REG, memory

AL, DL

DX, AX

m1 DB?

AL, m1

m2 DW?

AX, m2

memory, immediate

REG, immediate

memory, REG

REG, SREG

The various directives are:

1. ASSUME: The ASSUME directive is used to inform the assembler the name of the logical segment it should use for a specified segment.

Ex: ASSUME DS: DATA tells the assembler that for any program instruction which refers to the data segment, it should use the logical segment called DATA.

2.DB -Define byte. It is used to declare a byte variable or set aside one or more storage locations of type byte in memory.

For example, CURRENT_VALUE DB 36H tells the assembler to reserve 1 byte of memory for a variable named CURRENT_ VALUE and to put the value 36 H in that memory location when the program is loaded into RAM.

3. DW -Define word. It tells the assembler to define a variable of type word or to reserve storage locations of type word in memory.

4. DD (define double word): This directive is used to declare a variable of type double word or restore memory locations which can be accessed as type double word.

5.DQ (define quadword): This directive is used to tell the assembler to declare a variable 4 words in length or to reserve 4 words of storage in memory.

6.DT (define ten bytes): It is used to inform the assembler to define a variable which is 10 bytes in length or to reserve 10 bytes of storage in memory.

7. EQU –Equate It is used to give a name to some value or symbol. Every time the assembler finds the given name in the program, it will replace the name with the value or symbol we have equated with that name

8.ORG -Originate: The ORG statement changes the starting offset address of the data.

It allows to set the location counter to a desired value at any point in the program. For example, the statement ORG 3000H tells the assembler to set the location counter to 3000H.

9. PROC- Procedure: It is used to identify the start of a procedure. Or subroutine.

10. END- End program. This directive indicates the assembler that this is the end of the program module. The assembler ignores any statements after an END directive.

11. ENDP- End procedure: It indicates the end of the procedure (subroutine) to the assembler.

12.ENDS-End Segment: This directive is used with the name of the segment to indicate the end of that logical segment.

Ex: CODE SEGMENT: Start of logical segment containing code

CODE ENDS: End of the segment named CODE.

2.5.1 Data transfer group

MOV – MOV Destination, Source

The MOV instruction copies a word or byte of data from a specified source to a specified destination. The destination can be a register or a memory location. The source can be a register, a memory location or an immediate number. The source and destination cannot both be memory locations. They must both be of the same type (bytes or words).

MOV instruction does not affect any flag.

MOV CX, 037AH Put immediate number 037AH to CX

MOV BL, [437AH] Copy byte in DS at offset 437AH to BL

MOV AX, BX Copy content of register BX to AX

MOV DL, [BX] Copy byte from memory at [BX] to DL

MOV DS, BX Copy word from BX to DS register

MOV RESULT [BP], AX

Copy AX to two memory locations; AL to the first location, AH to the second;

EA of the first memory location is sum of the displacement represented by RESULTS and content of BP.

Physical address = EA + SS. MOV ES: RESULTS [BP], AX.

Same as the above instruction, but physical address = EA + ES, because of the segment override prefix ES XCHG – XCHG Destination, Source.

The XCHG instruction exchanges the content of a register with the content of another register or with the content of memory location(s).

It cannot directly exchange the content of two memory locations. The source and destination must both be of the same type (bytes or words). The segment registers cannot be used in this instruction. This instruction does not affect any flag.

XCHG AX, DX Exchange word in AX with word in DX

XCHG BL, CH Exchange byte in BL with byte in CH

XCHG AL, PRICES [BX] Exchange byte in AL with byte in memory at EA = PRICE [BX] in DS.

LEA – LEA Register, Source

This instruction determines the offset of the variable or memory location named as the source and puts this offset in the indicated 16-bit register.

LEA does not affect any flag.

LEA BX, PRICES Load BX with offset of PRICE in DS

LEA BP, SS: STACK_TOP Load BP with offset of STACK_TOP in SS

LEA CX, [BX][DI] Load CX with EA = [BX] + [DI] LDS – LDS

Register, Memory address of the first word This instruction loads new values into the specified register and into the DS register from four successive memory locations. The word from two memory locations is copied into the specified register and the word from the next two memory locations is copied into the DS registers. LDS does not affect any flag.

LDS BX, [4326] Copy content of memory at displacement 4326H in DS to BL, content of 4327H to BH. Copy content at displacement of 4328H and 4329H in DS-to-DS register.

LDS SI, SPTR Copy content of memory at displacement SPTR and SPTR + 1 Page 2 in DS to SI register. Copy content of memory at displacements SPTR + 2 and SPTR + 3 in DS-to-DS register.

DS: SI now points at start of the desired string.

LES – LES Register, Memory address of the first word

This instruction loads new values into the specified register and into the ES register from four successive memory locations. The word from the first two memory locations is copied into the specified register, and the word from the next two memory locations is copied into the ES register. LES does not affect any flag.

LES BX, [789AH] Copy content of memory at displacement 789AH in DS to BL, content of 789BH to BH, content of memory at displacement 789CH and 789DH in DS is copied to ES register.

LES DI, [BX] Copy content of memory at offset [BX] and offset [BX] + 1 in DS to DI register.

Copy content of memory at offset [BX] + 2 and [BX] + 3 to ES register

2.5.2 Arithmetic group

ADD – ADD Destination, Source

ADC – ADC Destination, Source

These instructions add a number from some source to a number in some destination and put the result in the specified destination.

The ADC also adds the status of the carry flag to the result. The source may be an immediate number, a register, or a memory location. The destination may be a register or a memory location. The source and the destination in an instruction cannot both be memory locations. The source and the destination must be of the same type (bytes or words).

If you want to add a byte to a word, you must copy the byte to a word location and fill the upper byte of the word with 0’s before adding.

Flags affected: AF, CF, OF, SF, ZF.

ADD AL, 74H Add immediate number 74H to content of AL. Result in AL

ADC CL, BL Add content of BL plus carry status to content of CL

ADD DX, BX Add content of BX to content of DX ADD DX, [SI] Add word from memory at offset [SI] in DS to content of DX

ADC AL, PRICES [BX] Add byte from effective address PRICES [BX] plus carry status to content of AL ADD AL, PRICES [BX] Add content of memory at effective address PRICES [BX] to AL

SUB – SUB Destination, Source SBB

SBB Destination, Source

These instructions subtract the number in some source from the number in some destination and put the result in the destination. The SBB instruction also subtracts the content of carry flag from the destination. The source may be an immediate number, a register or memory location. The destination can also be a register or a memory location. However, the source and the destination cannot both be memory location.

SUB CX, BX CX – BX; Result in CX

SBB CH, AL Subtract content of AL and content of CF from content of CH.

Result in CH SUB AX, 3427H Subtract immediate number 3427H from AX

SBB BX, [3427H] Subtract word at displacement 3427H in DS and content of CF from BX

SUB PRICES [BX], 04H Subtract 04 from byte at effective address PRICES [BX], if PRICES is declared with DB;

Subtract 04 from word at effective address PRICES [BX], if it is declared with DW.

SBB CX, TABLE [BX] Subtract word from effective address TABLE [BX] and status of CF from CX.

SBB TABLE [BX], CX Subtract CX and status of CF from word in memory at effective address TABLE[BX].

MUL – MUL Source

This instruction multiplies an unsigned byte in some source with an unsigned byte in AL register or an unsigned word in some source with an unsigned word in AX register. The source can be a register or a memory location. When a byte is multiplied by the content of AL, the result (product) is put in AX. When a word is multiplied by the content of AX, the result is put in DX and AX registers. If you want to multiply a byte with a word, you must first move the byte to a word location such as an extended register and fill the upper byte of the word with all 0’s.

You cannot use the CBW instruction for this, because the CBW instruction fills the upper byte with copies of the most significant bit of the lower byte.

MUL BH Multiply AL with BH; result in AX

MUL CX Multiply AX with CX; result high word in DX, low word in AX

MUL BYTE PTR [BX] Multiply AL with byte in DS pointed to by [BX]

MUL FACTOR [BX] Multiply AL with byte at effective address FACTOR [BX], if it is declared as type byte with DB. Multiply AX with word at effective address FACTOR [BX], if it is declared as type word with DW.

MOV AX, MCAND_16 Load 16-bit multiplicand into AX MOV CL, MPLIER_8 Load 8-bit multiplier into CL MOV CH, 00H Set upper byte of CX to all 0’s MUL CX AX times CX; 32-bit result in DX and AX

IMUL – IMUL Source

This instruction multiplies a signed byte from source with a signed byte in AL or a signed word from some source with a signed word in AX. The source can be a register or a memory location. When a byte from source is multiplied with content of AL, the signed result (product) will be put in AX.

IMUL BH Multiply signed byte in AL with signed byte in BH; result in AX.

IMUL AX Multiply AX times AX; result in DX and AX

MOV CX, MULTIPLIER Load signed word in CX

MOV AL, MULTIPLICAND Load signed byte in AL CBW Extend sign of AL into AH

IMUL CX Multiply CX with AX; Result in DX and AX

DIV – DIV Source This instruction is used to divide an unsigned word by a byte or to divide an unsigned double word (32 bits) by a word.

When a word is divided by a byte, the word must be in the AX register. The divisor can be in a register or a memory location. After the division, AL will contain the 8-bit quotient, and AH will contain the 8-bit remainder. When a double word is divided by a word, the most significant word of the double word must be in DX, and the least significant word of the double word must be in AX. After the division, AX will contain the 16-bit quotient and DX will contain the 16-bit remainder

DIV BL Divide word in AX by byte in BL; Quotient in AL, remainder in AH

DIV CX Divide down word in DX and AX by word in CX; Quotient in AX, and remainder in DX.

DIV SCALE [BX] AX / (byte at effective address SCALE [BX]) if SCALE [BX] is of type byte; or (DX and AX) / (word at effective address SCALE[BX] if SCALE[BX] is of type word IDIV

IDIV Source This instruction is used to divide a signed word by a signed byte, or to divide a signed double word by a signed word. When dividing a signed word by a signed byte, the word must be in the AX register. The divisor can be in an 8-bit register or a memory location. After the division, AL will contain the signed quotient, and AH will contain the signed remainder

IDIV BL Signed word in AX/signed byte in BL

IDIV BP Signed double word in DX and AX/signed word in BP

IDIV BYTE PTR [BX] AX / byte at offset [BX] in DS INC

INC Destination

The INC instruction adds 1 to a specified register or to a memory location. AF, OF, PF, SF, and ZF are updated, but CF is not affected. This means that if an 8-bit destination containing FFH or a 16-bit destination containing FFFFH is incremented, the result will be all 0’s with no carry.

INC BL Add 1 to contains of BL register

INC CX Add 1 to contains of CX register

INC BYTE PTR [BX] Increment byte in data segment at offset contained in BX.

INC WORD PTR [BX] Increment the word at offset of [BX] and [BX + 1] in the data segment.

INC TEMP Increment byte or word named TEMP in the data segment.

Increment byte if MAX_TEMP declared with DB. Increment word if MAX_TEMP is declared with DW.

INC PRICES [BX] Increment element pointed to by [BX] in array PRICES.

Increment a word if PRICES is declared as an array of words; Increment a byte if PRICES is declared as an array of bytes.

DEC – DEC Destination

This instruction subtracts 1 from the destination word or byte. The destination can be a register or a memory location. AF, OF, SF, PF, and ZF are updated, but CF is not affected. This means that if an 8-bit destination containing 00H or a 16-bit destination containing 0000H is decremented, the result will be FFH or FFFFH with no carry (borrow).

DEC CL Subtract 1 from content of CL register

DEC BP Subtract 1 from content of BP register

DEC BYTE PTR [BX] Subtract 1 from byte at offset [BX] in DS.

DEC WORD PTR [BP] Subtract 1 from a word at offset [BP] in SS.

DEC COUNT Subtract 1 from byte or word named COUNT in DS. Decrement a byte if COUNT is declared with a DB; Decrement a word if COUNT is declared with a DW.

DAA (DECIMAL ADJUST AFTER BCD ADDITION)

This instruction is used to make sure the result of adding two packed BCD numbers is adjusted to be a legal BCD number. The result of the addition must be in AL for DAA to work correctly. If the lower nibble in AL after an addition is greater than 9 or AF was set by the addition, then the DAA instruction will add 6 to the lower nibble in AL. If the result in the upper nibble of AL in now greater than 9 or if the carry flag was set by the addition or correction, then the DAA instruction will add 60H to AL.

Let AL = 59 BCD, and BL = 35 BCD ADD AL, BL AL = 8EH; lower nibble > 9, add 06H to AL DAA

AL = 94 BCD, CF = 0

Let AL = 88 BCD, and BL = 49 BCD ADD AL, BL AL = D1H; AF = 1, add 06H to AL

DAA AL = D7H; upper nibble > 9, add 60H to AL AL = 37 BCD, CF = 1

The DAA instruction updates AF, CF, SF, PF, and ZF; but OF is undefined.

DAS (DECIMAL ADJUST AFTER BCD SUBTRACTION)

This instruction is used after subtracting one packed BCD number from another packed BCD number, to make sure the result is correct packed BCD. The result of the subtraction must be in AL for DAS to work correctly. If the lower nibble in AL after a subtraction is greater than 9 or the AF was set by the subtraction, then the DAS instruction will subtract 6 from the lower nibble AL. If the result in the upper nibble is now greater than 9 or if the carry flag was set, the DAS instruction will subtract 60 from AL.

Let AL = 86 BCD, and BH = 57 BCD SUB AL, BH AL = 2FH; lower nibble > 9, subtract 06H from AL AL = 29 BCD, CF = 0

Let AL = 49 BCD, and BH = 72 BCD SUB AL, BH AL = D7H; upper nibble > 9, subtract 60H from AL DAS AL = 77 BCD, CF = 1 (borrow is needed)

The DAS instruction updates AF, CF, SF, PF, and ZF; but OF is undefined.

AAA (ASCII ADJUST FOR ADDITION) Numerical data coming into a computer from a terminal is usually in ASCII code.

In this code, the numbers 0 to 9 are represented by the ASCII codes 30H to 39H. After the addition, the AAA instruction is used to make sure the result is the correct unpacked BCD.

Let AL = 0011 0101 (ASCII 5), and BL = 0011 1001 (ASCII 9) ADD AL, BL AL = 0110 1110 (6EH, which is incorrect BCD) AAA AL = 0000 0100 (unpacked BCD 4) CF = 1 indicates answer is 14 decimals.

The AAA instruction works only on the AL register. The AAA instruction updates AF and CF; but OF, PF, SF and ZF are left undefined.

AAS (ASCII ADJUST FOR SUBTRACTION)

Numerical data coming into a computer from a terminal is usually in an ASCII code. In this code the numbers 0 to 9 are represented by the ASCII codes 30H to 39H. The 8086 allows you to subtract the ASCII codes for two decimal digits without masking the “3” in the upper nibble of each. The AAS instruction is then used to make sure the result is the correct unpacked BCD.

Let AL = 00111001 (39H or ASCII 9), and BL = 00110101 (35H or ASCII 5)

SUB AL, BL AL = 00000100 (BCD 04), and CF = 0

AAS AL = 00000100 (BCD 04), and CF = 0 (no borrow required)

Let AL = 00110101 (35H or ASCII 5), and BL = 00111001 (39H or ASCII 9)

SUB AL, BL AL = 11111100 (– 4 in 2’s complement form), and CF = 1 AAS AL = 00000100 (BCD 06), and CF = 1 (borrow required)

The AAS instruction works only on the AL register. It updates ZF and CF; but OF, PF, SF, AF are left undefined.

AAM (BCD ADJUST AFTER MULTIPLY) Before you can multiply two ASCII digits, you must first mask the upper 4 bits of each. This leaves unpacked BCD (one BCD digit per byte) in each byte. After the two unpacked BCD digits are multiplied, the AAM instruction is used to adjust the product to two unpacked BCD digits in AX.

AAM works only after the multiplication of two unpacked BCD bytes, and it works only the operand in AL. AAM updates PF, SF and ZF but AF; CF and OF are left undefined.

Let AL = 00000101 (unpacked BCD 5), and BH = 00001001 (unpacked BCD 9)

MUL BH AL x BH: AX = 00000000 00101101 = 002DH AAM AX = 00000100 00000101 = 0405H (unpacked BCD for 45)

AAD (BCD-TO-BINARY CONVERT BEFORE DIVISION) AAD converts two unpacked BCD digits in AH and AL to the equivalent binary number in AL. This adjustment must be made before dividing the two unpacked BCD digits in AX by an unpacked BCD byte. After the BCD division, AL will contain the unpacked BCD quotient and AH will contain the unpacked BCD remainder. AAD updates PF, SF and ZF; AF, CF and OF are left undefined.

Let AX = 0607 (unpacked BCD for 67 decimal), and CH = 09H AAD AX = 0043 (43H = 67 decimal) DIV CH AL = 07; AH = 04; Flags undefined after DIV If an attempt is made to divide by 0, the 8086 will generate a type 0 interrupt.

2.5.3 Logical group

AND – AND Destination, Source

This instruction ANDs each bit in a source byte or word with the same numbered bit in a destination byte or word. The result is put in the specified destination. The content of the specified source is not changed. The source can be an immediate number, the content of a register, or the content of a memory location. The destination can be a register or a memory location. The source and the destination cannot both be memory locations. CF and OF are both 0 after AND. PF, SF, and ZF are updated by the AND instruction. AF is undefined. PF has meaning only for an 8-bit operand.

AND CX, [SI] AND word in DS at offset [SI] with word in CX register; Result in CX register

AND BH, CL AND byte in CL with byte in BH; Result in BH

AND BX, 00FFH 00FFH Masks upper byte, leaves lower byte unchanged.

OR – OR Destination, Source

This instruction ORs each bit in a source byte or word with the same numbered bit in a destination byte or word. The result is put in the specified destination. The content of the specified source is not changed. The source can be an immediate number, the content of a register, or the content of a memory location. The destination can be a register or a memory location. The source and destination cannot both be memory locations. CF and OF are both 0 after OR. PF, SF, and ZF are updated by the OR instruction. AF is undefined. PF has meaning only for an 8-bit operand.

OR AH, CL CL ORed with AH, result in AH, CL not changed

OR BP, SI SI ORed with BP, result in BP, SI not changed

OR SI, BP BP ORed with SI, result in SI, BP not changed

OR BL, 80H BL ORed with immediate number 80H; sets MSB of BL to 1

OR CX, TABLE [SI] CX ORed with word from effective address TABLE [SI]; Content of memory is not changed.

XOR – XOR Destination, Source

This instruction Exclusive-ORs each bit in a source byte or word with the same numbered bit in a destination byte or word. The result is put in the specified destination. The content of the specified source is not changed. The source can be an immediate number, the content of a register, or the content of a memory location. The destination can be a register or a memory location. The source and destination cannot both be memory locations. CF and OF are both 0 after XOR. PF, SF, and ZF are updated. PF has meaning only for an 8-bit operand. AF is undefined.

XOR CL, BH Byte in BH exclusive-ORed with byte in CL. Result in CL. BH not changed.

XOR BP, DI Word in DI exclusive-ORed with word in BP. Result in BP. DI not changed.

XOR WORD PTR [BX], 00FFH Exclusive-OR immediate number 00FFH with word at offset [BX] in the data segment. Result in memory location [BX]

NOT – NOT Destination The NOT instruction inverts each bit (forms the 1’s complement) of a byte or word in the specified destination. The destination can be a register or a memory location. This instruction does not affect any flag. NOT BX Complement content or BX register

NOT BYTE PTR [BX] Complement memory byte at offset [BX] in data segment.

NEG – NEG Destination

This instruction replaces the number in a destination with its 2’s complement. The destination can be a register or a memory location. It gives the same result as the invert each bit and add one algorithm.

The NEG instruction updates AF, AF, PF, ZF, and OF.

NEG AL Replace number in AL with its 2’s complement

NEG BX Replace number in BX with its 2’s complement

NEG BYTE PTR [BX] Replace byte at offset BX in DX with its 2’s complement

NEG WORD PTR [BP] Replace word at offset BP in SS with its 2’s complement

CMP – CMP Destination, Source This instruction compares a byte / word in the specified source with a byte / word in the specified destination. The source can be an immediate number, a register, or a memory location. The destination can be a register or a memory location.

CX = BX 0 1 0 Result of subtraction is 0 CX > BX 0 0 0 No borrow required, so CF = 0 CX < BX 1 0 1 Subtraction requires borrow, so CF = 1

CMP AL, 01H Compare immediate number 01H with byte in AL CMP BH, CL Compare byte in CL with byte in BH

CMP CX, TEMP Compare word in DS at displacement TEMP with word at

CX CMP PRICES [BX], 49H Compare immediate number 49H with byte at offset [BX] in array PRICES TEST

– TEST Destination, Source This instruction ANDs the byte / word in the specified source with the byte / word in the specified destination. Flags are updated, but neither operand is changed. The test instruction is often used to set flags before a Conditional jump instruction

TEST AL, BH AND BH with AL.

No result stored; Update PF, SF, ZF.

TEST CX, 0001H AND CX with immediate number 0001H; No result stored; Update PF, SF, ZF TEST BP, [BX][DI] AND word is offset [BX][DI] in DS with word in BP. No result stored. Update PF, SF, and ZF.

References:

1. Microprocessor Book by A.P.Godse and D.A.Godse

2. Microprocessor And Microcontroller Book by A.P.Godse