Unit-5

Peripheral Devices

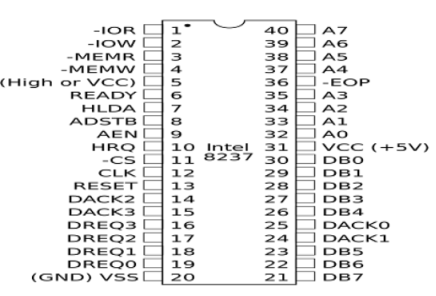

Pin Configuration

|

Fig.1: Pin Configuration of 8237

- It uses a power supply of 5V.

- D7-0 / A15-8: For communicating, there are 8 bidirectional data pins. When the processor is in active mode and the 8257 in active state then it is in slave mode. When the processor remains in the HOLD state and 8257 behaves as the master, then they send most significant 8 bits of memory address.

- A3-0: When the processor remains in active state and uses address input pins of 8257 to select one of the registers.

- IOR : It is an active low signal which is activated by the processor to read an Address Register, Counter Register, or the status register, when the it works in the slave mode.

- IOW: It is an active low signal which is activated by the processor to write to an Address Register, Counter Register, or the control register, when the it remains in the slave mode.

- MR: It is an active low output pin which operates when it is in the slave mode.

- MW: It is an active low output pin when it is in the slave mode. When the processor is in the HOLD state, it drives the pin that is activated for a DMA write machine cycle and becomes inactive for DMA read machine cycle.

- CS: It is an active low input pin used for chip selection.

- CLK: It is an input pin for clock pulse. The maximum allowed frequency is about 3 MHz. The input of the clock is connected to the output of the processor in a system which is based on 8086.

- READY: It is an active high input pin. Devices having slow access times can use it to insert wait states during the DMA read or write to the machine cycles.

- HRQ: HRQ stands for HOLD REQUEST. It is an active high output pin and is connected to the HOLD input of 8086. Whenever a DRQ input inactive and the DMA channel corresponding to it is enabled then the HRQ output is activated by 8257.

- HLDA: HLDA stands for HOLD acknowledge. It is an active high input pin which is connected to the HLDA output of 8086.

- TC: TC stands for terminal count and is an active high output pin. The output is activated when all the 14 Least Significant bits of the Control Register becomes 0.

- MARK: This is an active high output pin and is activated when the Least Significant 7 bits of the Control Register become 0 for the DMA channel.

- AEN: AEN stands for address enable. It is an active high output pin. Intel8257 gives an outputs 0 on AEN when 8086 becomes the master of the computer system.

- ADSTB: ADSTB stands for address strobe and is an active high output pin performing the same function to output of 8085. Here, if the output on this pin is 0, then it is in the slave mode.

- DACK3-0 : These are the active low DMA acknowledged output pins used only once for every four DMA channels.

- DRQ3-0: They are active high DMA request input pins assigned one for each DMA channel. They are activated by some special-purpose I/O port chips.

- RESET : It is an active high input pin which is connected to the RESET OUT pin of 8086. After 8257 is reset, the control register contents turn to 00H.

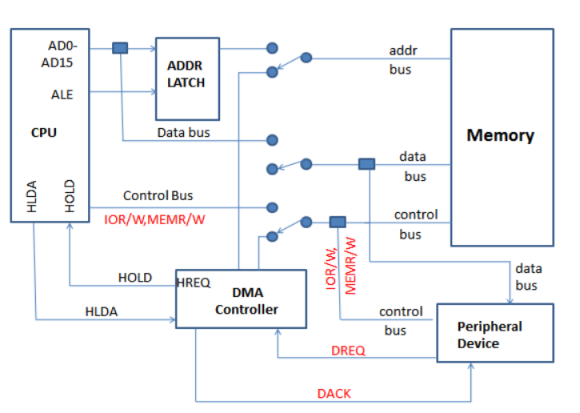

Functional block diagram:

|

Fig 2 Functional Block Diagram of 8237

- The 8237 supplies memory & I/O with control signals and memory address information during the DMA transfer.

- It is actually a special-purpose microprocessor which transfer high-speed data between memory and I/O.

- 8237 is not a discrete component in modern microprocessor-based systems.

- It appears within many system controller chip sets.

- 8237 is a four-channel device compatible with 8086/8088, adequate for small systems.

- Expandable to any number of DMA channel inputs

- 8237 is capable of DMA transfers at rates up to 1.6MB per second.

- Each channel is capable of addressing a full 64K-byte section of memory.

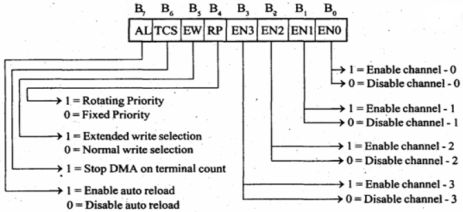

Control Word Register

|

Operating Modes

The operating modes of 8237 are as follows:

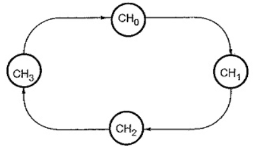

- Rotating priority mode

- Here, the priority of channels has a circular sequence.

- The channel that is serviced has the lowest priority and the channel present next to it has the highest priority.

- This is explained with the help of figure.

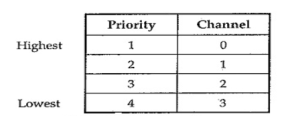

|

- Fixed priority mode

- Here, channel 0 has highest priority and channel 3 has the lowest priority.

- After one channel is recognized for service, other channels are prevented from interfering until the service is completed.

|

- Extended write mode

- It is used to provide alternate timing for the I/O or memory to write signals.

- This allows the devices to an early READY signal and prevents the unnecessary occurrence of wait states.

- It is done by activating MEMW and IOW signals .

- TC stop mode

- If TC is set, channel is disabled.

- Hence, it prevents further DMA operation on that channel.

- To enable DMA operation it is necessary to set the enable bit of the channel present in the mode set register.

- If TC stop bit is not set then the presence of TC output has no effect on the channel enable bits.

- Auto load mode

- When turned ON , it enables block chaining operations.

- In this, channel 2 parameters are initialized for the first data block.

- They are automatically copied to channel 3 registers.

- When an update cycle is initialized, the channel 3 parameters are transferred to channel 2.

- This is auto reload and is used for applications like CRT refreshing.

Key takeaway

- Used in graphics cards, network cards, sound cards etc.

- Used in intra-chip transfer in multi-core processors.

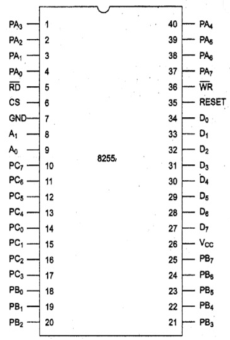

Pin Configuration

|

Fig.3: Pin Configuration of 8255

- It is also known as Programmable Peripheral Interface.

- It is a multi port device.

- It has 24 I/O pins. They are divided into three 8 bit ports PA, PB, PC.

- Port A and port B are used as 8-bit I/O ports.

- Port C is used as an 8-bit I/O port or as two 4-bit I/O ports or produces handshake signals for ports A and B.

- CS: The chip select CS (pin 6) is used to enable the 8255 chip. It is an active-low signal, hence is enabled when CS = 0.

- RESET: It is an input pin 35 and is connected to the RESET line of system 8085. When the system is reset, all the ports behave as input lines. This is done to prevent 8255 from being destroyed due to mismatch of ports.

- Eight data lines (D0–D7) are available to read/write data into the ports or control register under the status of the RD (pin 5) and WR (pin 36), which are active-low signals for read and write operations respectively.

- Address lines A1 and A0 allow to access a data register for each port or a control register, as listed below:

A1 | A0 | PORT SELECTED |

0 | 0 | PORT A |

0 | 1 | PORT B |

1 | 0 | PORT C |

1 | 1 | Control Register |

Operating Modes

There are two basic operating modes of 8255.

- Bit set/reset mode (BSR mode)

- Input/ output mode (I/O mode)

The modes selected by the D7 bit of the control word register are:

When D7 = 1, 8255 operates in I/O mode else BSR mode.

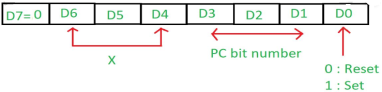

BSR MODE

|

- D7 bit is always 0 for this mode.

- Bits D6, D5 and D4 are don't care bits.

- Bits D3, D2 and D1 are used for pin selection of Port C.

- Bit D0 is used to set/reset the above selected pin.

Selection of port C pin is determined as follows:

D3 | D2 | D1 | Bit/pin of port C selected |

0 | 0 | 0 | PC0 |

0 | 0 | 1 | PC1 |

0 | 1 | 0 | PC2 |

0 | 1 | 1 | PC3 |

1 | 0 | 0 | PC4 |

1 | 0 | 1 | PC5 |

1 | 1 | 0 | PC6 |

1 | 1 | 1 | PC7 |

For example:

If PC4 be set, then in the control word is,

- Since it is a BSR mode, D7 = '0'.

- Since D4, D5, D6 are don’t care hence assuming them to be '0'.

- PC4 has to be selected, hence, D3 = '1', D2 = '0', D1 = '0'.

- PC4 has to be set, hence, D0 = '1'.

Thus, as per the above values, 0AH (in hex) will be loaded into the Control Word Register (CWR).

I/O MODE

When D7 bit of the Control Word Register is 1, this mode is selected.

There are three I/O modes and they are:

- Mode 0 - Simple I/O

- Mode 1 - Strobed I/O

- Mode 2 - Strobed Bi-directional I/O

- Mode 0 – Simple or basic I/O mode:

Port A, B and C can work either as input or as output function. The outputs are latched but the inputs are not latched. It can handle interrupts.

- Mode 1 – Handshake or strobbed I/O: Here, either port A or B can work and port C is used to provide handshake signals. The outputs as well as inputs are latched. It can handle interrupts. Before actual data is transmitted, there is transmission of signal to match speed of CPU and printer.

- Mode 2 – Bidirectional I/O: In this mode only port A will work, port B can either is in mode 0 or 1 and port C bits are used as handshake signal. The outputs as well as inputs are latched. It has interrupt handling capability.

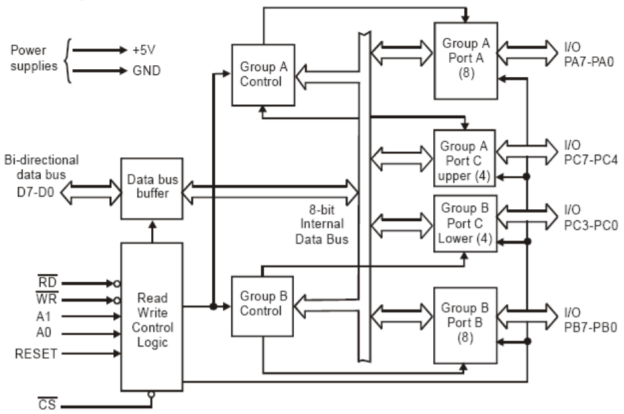

Functional block diagram

|

Fig 4 Functional Block Diagram

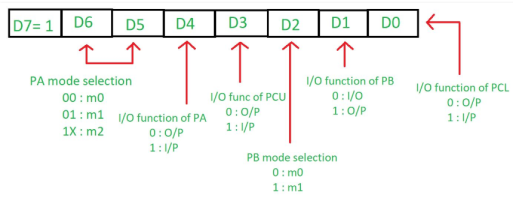

Control Word for I/O mode

|

- The most significant bit (D7) is 1 for the I/O mode.

- D6 & D5: It is used to set the port A mode.

|

- D4 : It is used to check whether port A is taking input or displaying the output. If it is 1 then input else output.

- D3: It is used to check whether port C higher bites takes input or output. If 1, then input else output.

- D2: It tells the mode of port B. If 0, then port B is in M0 mode else in M1 mode.

- D1: It is used to check whether port B is taking input or displaying output. If 1, then input else output.

- D0: It is used to tell whether port C lower bits is taking input or displaying output. If 1, then it takes input else displays output.

Key takeaway

When 8255 microprocessors are reset, it clears the control word register contents and sets all the ports to input mode. Used as keyboard and display interface, traffic light control, printer interface and so on.

Pin Configuration

|

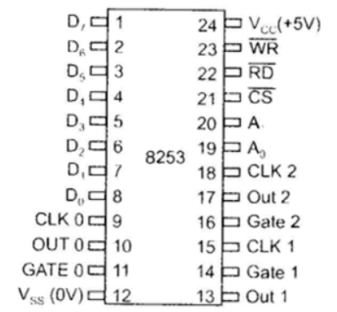

Fig.5: Pin Configuration of 8253

- It is a programmable counter / timer chip which is used as an Intel microcomputer peripheral.

- It uses nMOS technology with +5V supply and is packaged in a 24-pin plastic DIP.

- It is used as an event counter, elapsed time indicator, programmable one-shot etc.

- There are three counters, a data bus buffer, Read/Write control logic, and a control register. Each counter has two input signals - CLOCK & GATE, and one output signal - OUT.

It is a tri-state, bi-directional, 8-bit buffer, which is used to interface the 8253 to the system data bus. It has three basic functions −

- Programming the modes of 8253.

- Loading the count registers.

- Reading the count values.

It includes 5 signals, i.e. RD, WR, CS, and the address lines A0 & A1. In the peripheral I/O mode, the RD and WR signals are connected to IOR and IOW and in the memory mapped I/O mode to MEMR and MEMW.

Address lines A0 & A1 of the CPU are connected to lines A0 and A1 of the 8253 and CS is tied to a decoded address.

A1 | A0 | Result |

0 | 0 | Counter 0 |

0 | 1 | Counter 1 |

1 | 0 | Counter 2 |

1 | 1 | Control Word Register |

X | X | No Selection |

Functional block diagram:

|

Fig 6 Block Diagram of 8253

Control Word Register

This register can be accessed when lines A0 & A1 are at logic 1.

It is used to write a command word, its mode and either a read or write operation.

Following table provides the result for various control inputs:

A1 | A0 | RD | WR | CS | Result |

0 | 0 | 1 | 0 | 0 | Write Counter 0 |

0 | 1 | 1 | 0 | 0 | Write Counter 1 |

1 | 0 | 1 | 0 | 0 | Write Counter 2 |

1 | 1 | 1 | 0 | 0 | Write Control Word |

0 | 0 | 0 | 1 | 0 | Read Counter 0 |

0 | 1 | 0 | 1 | 0 | Read Counter 1 |

1 | 0 | 0 | 1 | 0 | Read Counter 2 |

1 | 1 | 0 | 1 | 0 | No operation |

X | X | 1 | 1 | 0 | No operation |

X | X | X | X | 1 | No operation |

Operating Modes

8253 can be operated in 6 different modes. They are:

Mode 0 ─ Interrupt on Terminal Count

- It is used for generating an interrupt to the microprocessor after a certain interval.

- The output is low after the mode is set and remains LOW after the count value is loaded into the counter.

- The counter decrement continues till the terminal count is reached.

- The GATE signal remains high for normal counting. When it is low, counting is terminated and the current count is latched till it goes high again.

Mode 1 – Programmable One Shot

- It is used as a mono stable multi-vibrator.

- GATE is used as a trigger input in this mode.

- As the count is loaded the output remains high and a trigger is applied.

- The output is high after initialization.

- Whenever the count becomes zero, a low pulse is generated at the output and the counter is reloaded.

Mode 3 – Square Wave Generator

- This mode is same as Mode 2 except that the output remains low for half of the timer period and high for the next half of the period.

Mode 4 − Software Triggered Mode

- In this, the output remains high till the timer counts to zero and at this point the output is low and then goes high again.

- The count is latched when GATE LOW.

- As per the terminal count, for one clock cycle the output goes low then goes HIGH. The low pulse is used as a strobe.

Mode 5 – Hardware Triggered Mode

- This mode generates a strobe as a result to an externally generated signal.

- It is same as mode 4 except that the counting is initiated by a signal at the gate input.

- As soon as it is initialized, the output goes high.

- When the terminal count is reached, the output goes low for one clock cycle.

Key takeaway

- In free running counter applications.

- As an event counter.

- Rate generator.

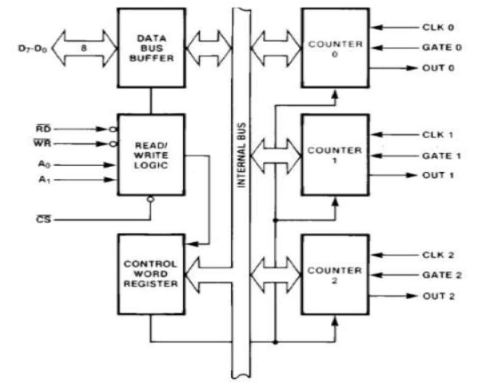

It is commonly known as PIC (Programmable Interrupt controller).

|

Fig 7 Block Diagram of 8259

Data Bus Buffer:

The data bus buffer allows the 8086 to send control words to the 8259A. The 8-bit data bus buffer also allows the 8259A to send interrupt opcode and address of the interrupt service subroutine to the 8086.

Read/Write Logic:

The RD and WR inputs control the data flow on the data bus when the device is selected by asserting its chip select (CS) input low.

Control Logic:

This block has an input and an output line. If the 8259A is properly enabled, the interrupt request will cause the 8259A to assert its INT output pin high.

Interrupt Request Register (IRR):

It is used to store all the interrupt levels which are requesting the service. The eight interrupt inputs set corresponding bits of the Interrupt Request Register upon service request.

Interrupt Service Register (ISR):

It stores all the levels that are currently being serviced.

Interrupt Mask Register (IMR):

It stores the masking bits of the interrupt lines to be masked. This register can be programmed by an Operation Command Word (OCW).

Priority Resolver:

It determines the priorities of the bits set in the IRR. The bit corresponding to the highest priority interrupt input is set in the ISR during the INTA input.

Cascade Buffer Comparator:

It generates control signals necessary for cascade operations. It also generates Buffer-Enable signals. Here, the former is called a master, and the latter are called slaves. The 8259 can be set up as a master or a slave by the SP/EN pin.

CAS0— CAS2

For a master 8259, the CAS0-CAS2 pins are output pins, and for slave 8259, these are input pins. When the 8259 is a master (that is, when it accepts interrupt requests from other 8259s), the CALL opcode is generated by the Master in response to the first INTA.

SP / EN (Slave Program /Enable Buffer):

The SP/EN signal is tied high for the master. However it is grounded for the slave.

Priority Modes and Other Features:

The various modes of operation of the Block Diagram of 8259 Programmable Interrupt Controller are :

o Fully Nested Mode,

o Special Fully Nested Mode (SFNM)

o Rotating Priority Mode,

o Special Masked Mode, and

o Polled Mode.

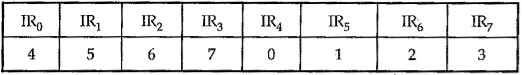

Fully Nested Mode (FNM) :

After initialization, the 8259A operates in fully nested mode so it is called default mode. In this mode, IR0 has highest priority and IR7 has lowest priority. When the interrupt is acknowledged, it sets the corresponding bit in ISR. This bit will inhibit all interrupts of the same or lower level, however it will accept higher priority interrupt requests. The vector address corresponding to this interrupt is then sent. The bit in the ISR will remain set until an EOI command is issued.

End of Interrupt (EOI):

- The ISR bit is reset by an EOI command issued by the CPU, usually just before exiting from the interrupt routine.

- In the Fully Nested Mode, the highest level in the ISR would necessarily correspond to the last interrupt acknowledged and serviced. In such a case, a non-specific EOI command may be issued by the CPU.

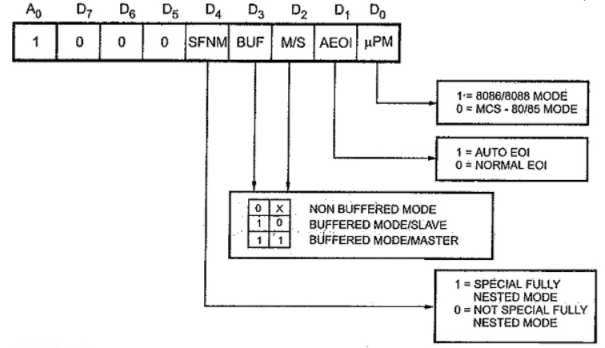

Special Fully Nested Mode (SFNM):

The Special Fully Nested Mode (SFNM) is used to avoid this problem. The SFNM is set up by ICW4 during initialisation. It is similar to the FNM.

Rotating Priority Mode:

The Rotating Priority mode can be set in Automatic Rotation, and Specific Rotation.

Automatic Rotation:

In this mode, a device, after being serviced, receives the lowest priority. The device just been serviced, will receive the seventh priority. Here IR3 has just been serviced.

Specific Rotation:

In this, the lowest priority can be assigned to any interrupt input (IR0 to IR7) thus fixes all other priorities.

For example if the lowest priority is assigned to IR2, other priorities are as shown below.

Special Mask Mode:

If any interrupt is in service, then the corresponding bit is set in ISR and the lower priority interrupts are inhibited. Some applications may require an interrupt service routine to dynamically alter the system priority structure during its execution under software control.

Poll Mode:

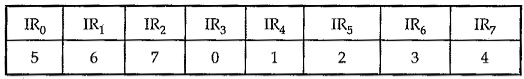

In this mode the INT output is not used. The microprocessor checks the status of interrupt requests by issuing poll command. The microprocessor reads contents of 8259A after issuing poll command. During this read operation the 8259A provides polled word and sets ISR bit of highest priority active interrupt request FORMAT.

I = 1 —> One or more interrupt requests activated.

I = 0 —> No interrupt request activated.

W2 W1 W0 —>Binary code of highest priority active interrupt request.

|

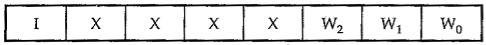

A write command issued to the 8259 with A0 = 0 and D4 = 1 is interpreted as ICW1, which starts the initialization sequence. It specifies,

- Single or multiple 8259As in the system

- 4 or 8 bit interval between the interrupt vector locations.

- The address bits A7 – A5 of the CALL instruction. (3 bits of lower byte address of CALL are given by user, rest bits are inserted by 8259A)

- Edge triggered or level triggered interrupts.

- ICW4 is needed or not.

|

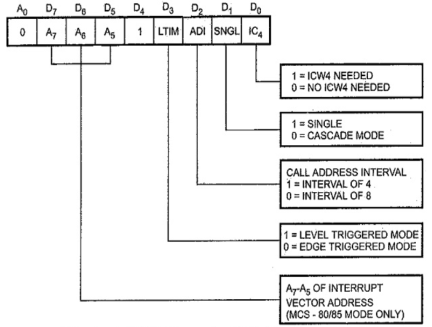

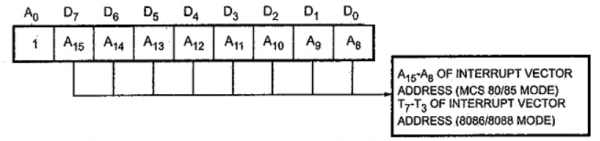

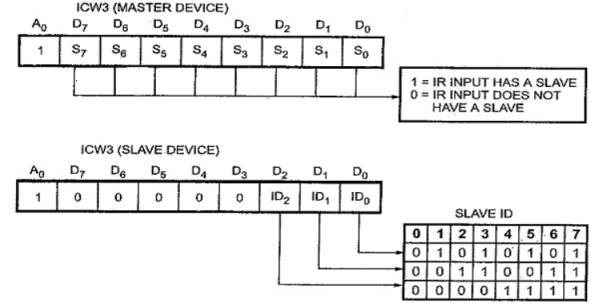

A write command following ICW1, with A0 = 1 is interpreted as ICW2. This is used to load the high order byte of the interrupt vector address of all the interrupts.

|

|

Key takeaway

After initialization, the 8259A operates in fully nested mode so it is called default mode. In this mode, IR0 has highest priority and IR7 has lowest priority. When the interrupt is acknowledged, it sets the corresponding bit in ISR.

The ISR bit is reset by an EOI command issued by the CPU, usually just before exiting from the interrupt routine. In the Fully Nested Mode, the highest level in the ISR would necessarily correspond to the last interrupt acknowledged and serviced. In such a case, a non-specific EOI command may be issued by the CPU.

8251 universal synchronous asynchronous receiver transmitter (USART) acts as a mediator between microprocessor and peripheral to transmit serial data into parallel form and vice versa.

- It takes data serially from peripheral (outside devices) and converts into parallel data.

- After converting the data into parallel form, it transmits it to the CPU.

- Similarly, it receives parallel data from microprocessor and converts it into serial form.

- After converting data into serial form, it transmits it to outside device (peripheral).

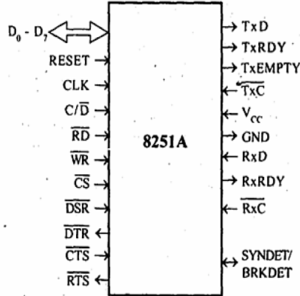

Pin Configuration

|

Fig 8 Pin Configuration

Data Bus : Bi-directional, tri-state, 8-bit Data Bus. This pin allows transfer of bytes between the CPU and the 8251A.

RD (Read) : A low on this input allows the CPU to read data or status bytes from 8251A

WR (Write) : A low on this input allows the CPU to write data or command word to the 8251A.

CLK (Clock) : The CLK input is used to generate internal device timing. The frequency of CLK must be greater than 30 times the receiver or transmitter data bit rates.

RESET : A high on this input forces the 8251A into an “Idle” mode. The device will remain at “Idle” until a new set of control words is written into the 8251 Pin Diagram to program its functional definition.

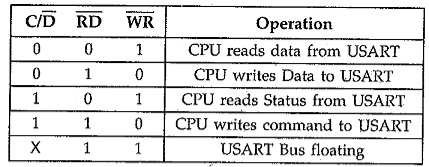

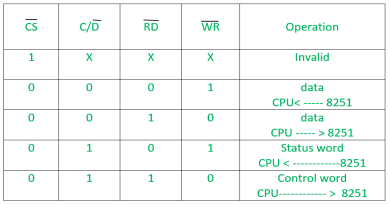

C/D (Control /Data) : This input in conjuction with the WR and RD inputs, informs the 8251A that the word on the Data Bus is either a data character control word or status information as shown in table.

CS (Chip Select) : A low on this input allows communication between CPU and 8251A

|

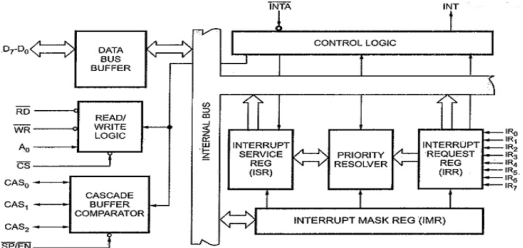

Fig 9 Block Diagram

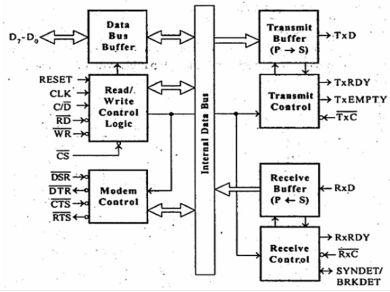

It contains the following blocks:

- Data bus buffer – This block helps in interfacing the internal data bus of 8251 to the system data bus. The data transmission is possible between 8251 and CPU by the data bus buffer block.

- Read/Write control logic – It is a control block for overall device. It controls the overall working by selecting the operation to be done. The operation selection depends upon input signals as:

|

In this way, this unit selects one of the three registers- data buffer register, control register, status register.

- Modem control (modulator/demodulator) –

A device converts analog signals to digital signals and vice-versa and helps the computers to communicate over telephone lines or cable wires. The following are active-low pins of Modem.- DSR: Data Set Ready signal is an input signal.

- DTR: Data terminal Ready is an output signal.

- CTS: It is an input signal which controls the data transmit circuit.

RTS: It is an output signal which is used to set the status RTS.

- Transmit buffer –

This block is used for parallel to serial converter that receives a parallel byte for conversion into serial signal and further transmission onto the common channel.- TXD: It is an output signal, if its value is one, means transmitter will transmit the data.

- Transmit control –

This block is used to control the data transmission with the help of following pins:- TXRDY: It means transmitter is ready to transmit data character.

- TXEMPTY: An output signal which indicates that TXEMPTY pin has transmitted all the data characters and transmitter is empty now.

- TXC: An active-low input pin which controls the data transmission rate of transmitted data.

- Receive buffer –

This block acts as a buffer for the received data.- RXD: An input signal which receives the data.

- Receive control –

This block controls the receiving data.- RXRDY: An input signal indicates that it is ready to receive the data.

- RXC: An active-low input signal which controls the data transmission rate of received data.

- SYNDET/BD: An input or output terminal. External synchronous mode-input terminal and asynchronous mode-output terminal.

Key takeaway

8251 universal synchronous asynchronous receiver transmitter (USART) acts as a mediator between microprocessor and peripheral to transmit serial data into parallel form and vice versa.

- It takes data serially from peripheral (outside devices) and converts into parallel data.

- After converting the data into parallel form, it transmits it to the CPU.

- Similarly, it receives parallel data from microprocessor and converts it into serial form.

- After converting data into serial form, it transmits it to outside device (peripheral).

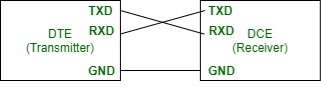

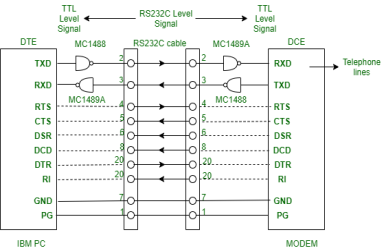

RS232 is an Interface and the protocol between DTE(data terminal equipment) and DCE(data communication equipment) using serial binary data exchange. Here C is used for the current version. Universal Asynchronous Data Receiver & Transmitter (UART), attached in a motherboard, used in connection with RS232 for transmitting data to any serial device like modem or printer from its DTE interface.

|

Fig 10 RS232 Protocol

Electrical Specifications:

Voltages:

There can be two states in the signal level of RS232C pins.

- Mark state – It is the high bit which is represented by binary 1 and have negative voltages. Its voltage limits for transmitting signal ranges from -5 to -15V. Its voltage limits for receiving signals ranges from -3 to -25V.

- Space state – It is the low bit which is represented by binary 0 and have positive voltages. Its voltage limits for transmitting signal ranges from +5 to +15V. Its voltage limits for receiving signals ranges from +3 to +25V.

Cables and Wires: The maximum cable length for RS232C is equals to 15.24 metres or equal to the capacitance of 2500pF. Limits for impedance of wires ranges from 3 ohms to 7 ohms.

Data and Slew rates: Rate of data transmission through RS232C is up to 20Kbps. The rate of change in signal levels i.e., slew rate is up to 30V/microsecond.

Current:

Maximum current rating is 3Amps at the maximum operating voltage of 250V AC.

Pins and Working:

|

Fig 11 RS232 Pin and Signal

RS232C requires 25 pins connector for connecting DTE and DCE. Here is the list of pins and signals of RS232C and the connection between DTE and DCE using drivers and receivers.

- TXD & RXD – Transmit Data and Receive Data on the DTE are the serial data lines. These lines have opposite functions on a DCE. TXT sends outgoing data to DCE. RXD receives incoming data from DTE.

- RTS & CTS – Transmitter activates the Request to Send when it requires to transmit data over the line. The line itself gets deactivated when the communication stops. Receiver activates the Clear to Send to tell the transmitter whether it is ready or not to receive the data. It remains active during the transmission.

- DTR & DSR – Through the Data Terminal Ready line, DTE informs the DCE that it is in online mode and the process of communication can occur. The main task of Data Set Ready signal is to inform that DCE is ready for communication.

- DCD – DCE activates the Data Carrier Detect in order to show that it has been connected to DTE.

- RI – When an incoming call on the telephone line is detected by DCE, then the Ring Indicator gets activates.

- Initially, the computer activates RTS signal to modem when a data is transferred from computer to modem.

- Modem in turn activates the DCD and then the CTS gets activated.

- Computer then sends data on TXD. After the data transmission is completed, the computer deactivates the RTS which causes the modem to deactivate CTS.

Key takwaway

RS232 is an Interface and the protocol between DTE(data terminal equipment) and DCE(data communication equipment) using serial binary data exchange. Here C is used for the current version. Universal Asynchronous Data Receiver & Transmitter (UART), attached in a motherboard, used in connection with RS232 for transmitting data to any serial device like modem or printer from its DTE interface.

Reference:

1. Gaonkar, Ramesh S , “Microprocessor Architecture, Programming and Applications with 8085”, Penram International Publishing.

2. Ray A K, Bhurchandi K M, “Advanced Microprocessors and Peripherals”, TMH Hall D V, Microprocessor Interfacing’, TMH

3.Liu and, “Introduction to Microprocessor”, TMH

4. Brey, Barry B, “INTEL Microprocessors”, PHI