Unit-3

Digital Modulation

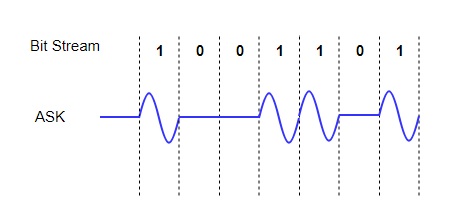

In ASK, the amplitude of the signal is varied to represent the signal levels, while frequency and phase remains constant. In order to represent 0 and 1, two different amplitudes are used.

Fig. : ASK

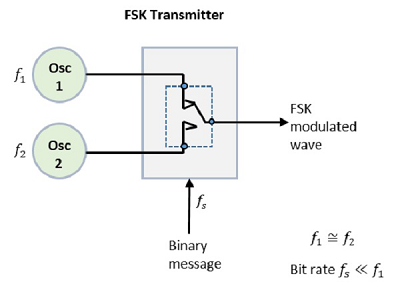

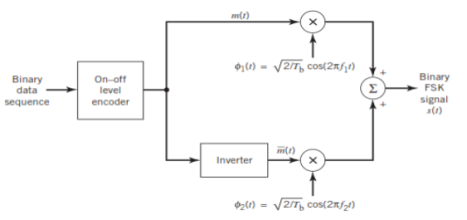

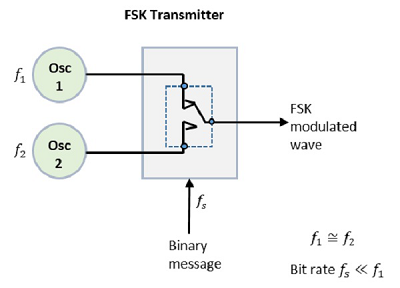

FSK Modulator

The FSK modulator block diagram comprises of two oscillators with a clock and the input binary sequence. Following is its block diagram.

Fig.: FSK modulator

The two oscillators, producing a higher and a lower frequency signals, are connected to a switch along with an internal clock. To avoid the abrupt phase discontinuities of the output waveform during the transmission of the message, a clock is applied to both the oscillators, internally. The binary input sequence is applied to the transmitter so as to choose the frequencies according to the binary input.

FSK Demodulator

There are different methods for demodulating a FSK wave. The main methods of FSK detection are asynchronous detector and synchronous detector. The synchronous detector is a coherent one, while asynchronous detector is a non-coherent one.

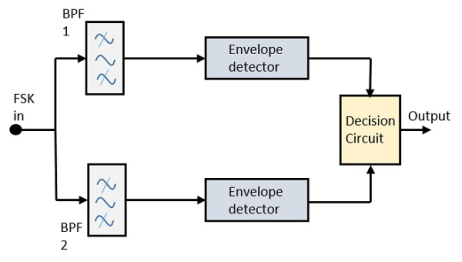

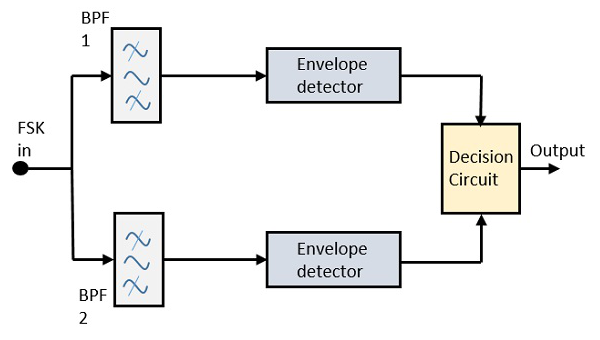

Asynchronous FSK Detector

The block diagram of Asynchronous FSK detector consists of two band pass filters, two envelope detectors, and a decision circuit. Following is the diagrammatic representation.

Fig.: FSK demodulator

The FSK signal is passed through the two Band Pass Filters BPFs, tuned to Space and Mark frequencies. The output from these two BPFs look like ASK signal, which is given to the envelope detector. The signal in each envelope detector is modulated asynchronously.

The decision circuit chooses which output is more likely and selects it from any one of the envelope detectors. It also re-shapes the waveform to a rectangular one.

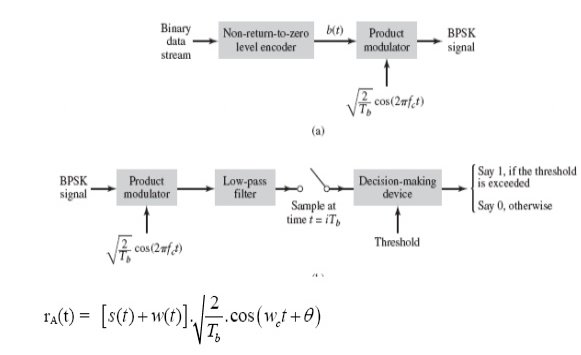

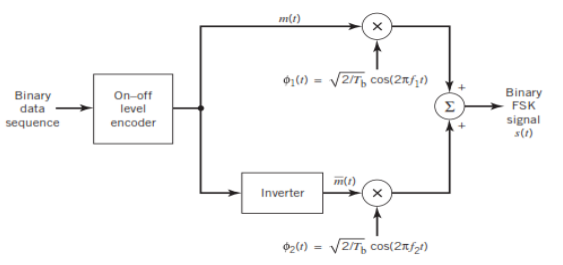

GENERATION AND COHERENT DETECTION OF BPSK SIGNALS

(i) Generation

To generate the BPSK signal, we build on the fact that the BPSK signal is a special case of DSB-SC modulation. Specifically, we use a product modulator consisting of two components.

(i) Non-return-to-zero level encoder, whereby the input binary data sequence is encoded in polar form with symbols 1 and 0 represented by the constant-amplitude.

(ii)Product modulator, which multiplies the level encoded binary wave by the sinusoidal carrier of amplitude to produce the BPSK signal. The timing pulses used to generate the level encoded binary wave and the sinusoidal carrier wave are usually, but not necessarily, extracted from a common master clock.

Fig. : Product modulator

(ii)Detection

To detect the original binary sequence of 1s and 0s, the BPSK signal at the channel output is applied to a receiver that consists of four sections

(a) Product modulator, which is also supplied with a locally generated reference signal that is a replica of the carrier wave

(b) Low-pass filter, designed to remove the double-frequency components of the product modulator output (i.e., the components centered on) and pass the zero-frequency components.

(c) Sampler, which uniformly samples the output of the low-pass filter at where; the local clock governing the operation of the sampler is synchronized with the clock responsible for bit-timing in the transmitter.

(d) Decision-making device, which compares the sampled value of the low-pass filters output to an externally supplied threshold, every second. If the threshold is exceeded, the device decides in favour of symbol 1; otherwise, it decides in favour of symbol 0 levels.

Fig.: Decision-making device

Fig.: Decision-making device

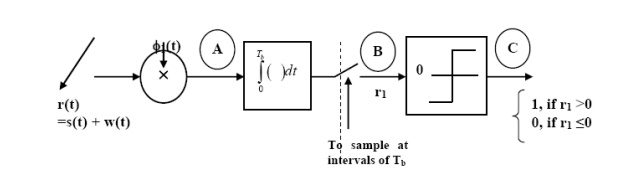

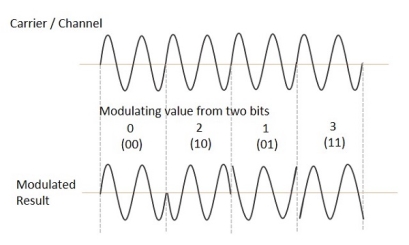

GENERATION AND COHERENT DETECTION OF BFSK SIGNALS

(i) Generation

On-off level encoder:

Here, the output is of constant amplitude √Eb for input 1 and 0 for input 0.

Pair of oscillators:

Frequency f1 and f2 differ by integer multiple of 1/Tb. The lower oscillator has frequency f2 preceded by inverter. When in a signal interval, the input symbol is 1, the upper oscillator is switched on, and signal s1(t) is transmitted, while lower oscillator is switched off.

When input is 0, upper oscillator is off, lower oscillator is on and signal s2(t) is transmitted.

Fig.: BFSK generation

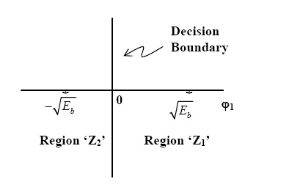

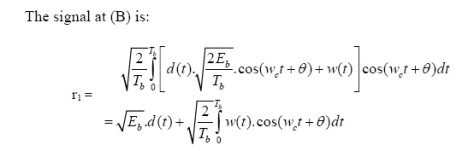

(ii) Detection

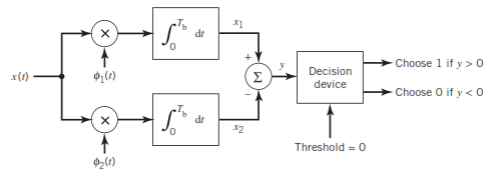

Fig.: BFSK detection

It consists of two correlators with a common input, and reference signals Ø1(t), Ø2(t) are applied.

Then y = x1 – x2

The output y is compared with the threshold =0

If y>0 then output = 1 else 0.

But if y=0 then the receiver makes a random guess of 0 or 1.

Key Takeaways:

1. The FSK modulator block diagram comprises of two oscillators with a clock and the input binary sequence

2. The main methods of FSK detection are asynchronous detector and synchronous detector.

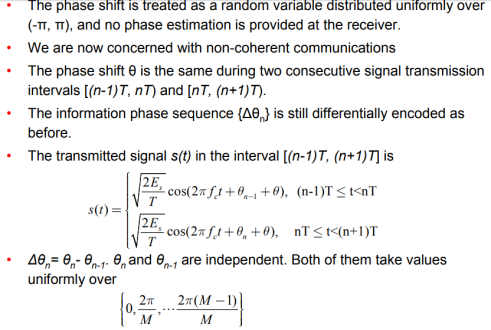

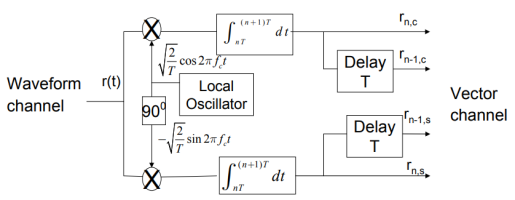

Differential phase shift keying

Fig.: DPSK generation

Key Takeaways:

Here, the phase of the modulated signal is shifted relative to the previous signal element. No reference signal is considered here. The signal phase follows the high or low state of the previous element. This DPSK technique doesn’t need a reference oscillator.

Quadrature modulation techniques

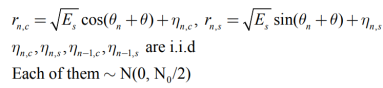

GENERATION AND COHERENT DETECTION OF QPSK SIGNALS

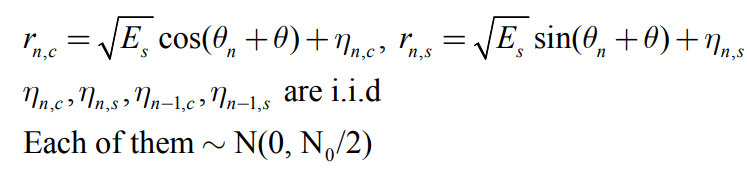

(i) Generation

The QPSK Modulator uses a bit-splitter, two multipliers with local oscillator, a 2-bit serial to parallel converter, and a summer circuit.

Fig.: QPSK generation

At the modulator’s input, the message signal’s even bits (i.e., 2nd bit, 4th bit, 6th bit, etc.) and odd bits (i.e., 1st bit, 3rd bit, 5th bit, etc.) are separated by the bits splitter and are multiplied with the same carrier to generate odd BPSK (called as PSKI) and even BPSK (called as PSKQ). The PSKQ signal is anyhow phase shifted by 90° before being modulated.

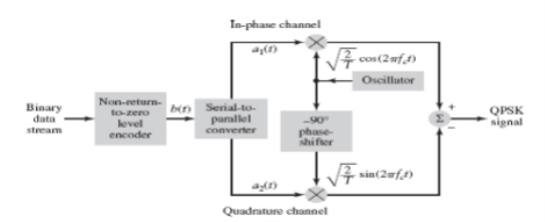

The QPSK waveform for two-bits input is as follows, which shows the modulated result for different instances of binary inputs.

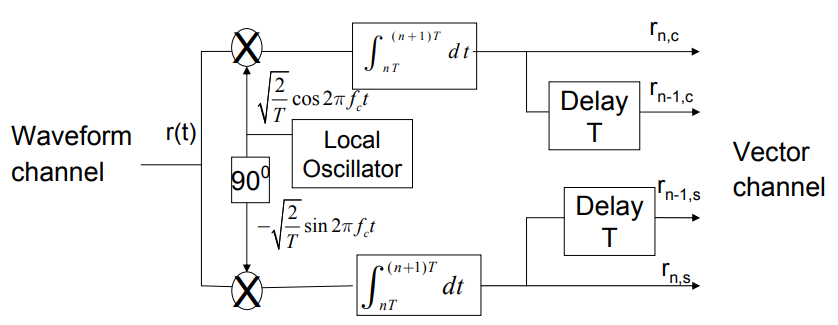

(ii) Detection

The QPSK Demodulator uses two product demodulator circuits with local oscillator, two band pass filters, two integrator circuits, and a 2-bit parallel to serial converter.

Fig.: QPSK detectors

The two product detectors at the input of demodulator simultaneously demodulate the two BPSK signals. The pair of bits are recovered here from the original data. These signals after processing are passed to the parallel to serial converter.

Fig.: QPSK output

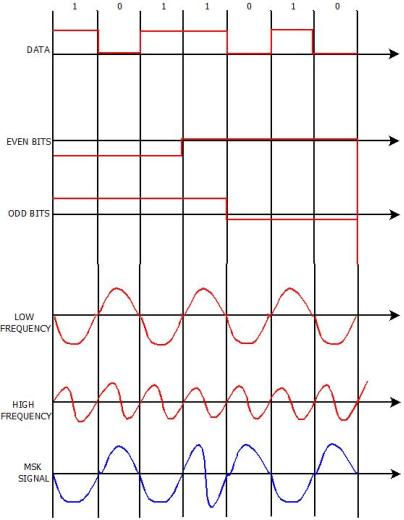

MSK

Minimum Shift Key Modulation is another type of digital modulation technique used to convert a digital signal into analog signals. It is also called Minimum-shift keying (MSK) or Advance Frequency Shift Keying because it is a type of continuous-phase frequency-shift keying.

Key features

Fig.: MSK output

Key Takeaways:

1. Minimum Shift Key Modulation is another type of digital modulation technique used to convert a digital signal into analog signals. It is also called Minimum-shift keying (MSK) or Advance Frequency Shift Keying because it is a type of continuous-phase frequency-shift keying.

2. QPSK Modulator uses a bit-splitter, two multipliers with local oscillator, a 2-bit serial to parallel converter, and a summer circuit.

A constellation diagram is a representation of a signal modulated by a digital modulation scheme such as quadrature amplitude modulation or phase-shift keying. It displays the signal as a two-dimensional xy-plane scatter diagram in the complex plane at symbol sampling instants.

The word binary represents two bits. M represents a digit that corresponds to the number of conditions, levels, or combinations possible for a given number of binary variables.

This is the type of digital modulation technique used for data transmission in which instead of one bit, two or more bits are transmitted at a time. As a single signal is used for multiple bit transmission, the channel bandwidth is reduced.

M-ary Equation

If a digital signal is given under four conditions, such as voltage levels, frequencies, phases, and amplitude, then M = 4.

The number of bits necessary to produce a given number of conditions is expressed mathematically as

N=log2M

Where

N is the number of bits necessary

M is the number of conditions, levels, or combinations possible with N bits.

The above equation can be re-arranged as

2N=M

For example, with two bits, 22 = 4 conditions are possible.

This is called as M-ary Phase Shift Keying M−aryPSK

The phase of the carrier signal, takes on M different levels.

Si(t)=√2E/T cos(wot+ϕit) 0≤t≤Tandi=1,2...M

ϕi(t)=2πiM wherei=1,2,3......M

Some prominent features of M-ary PSK are −

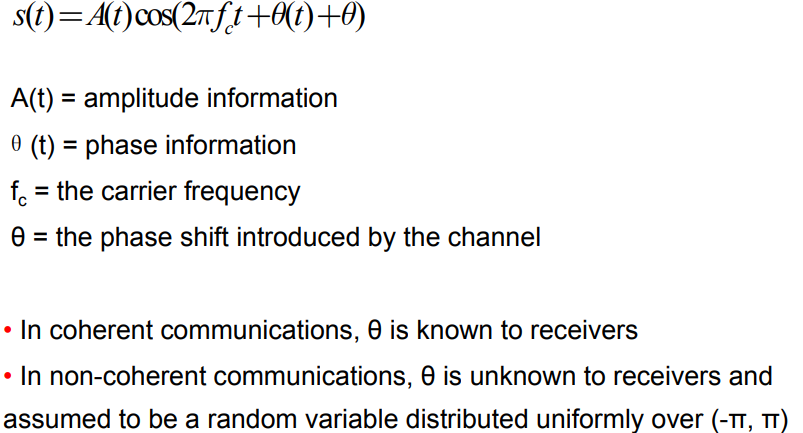

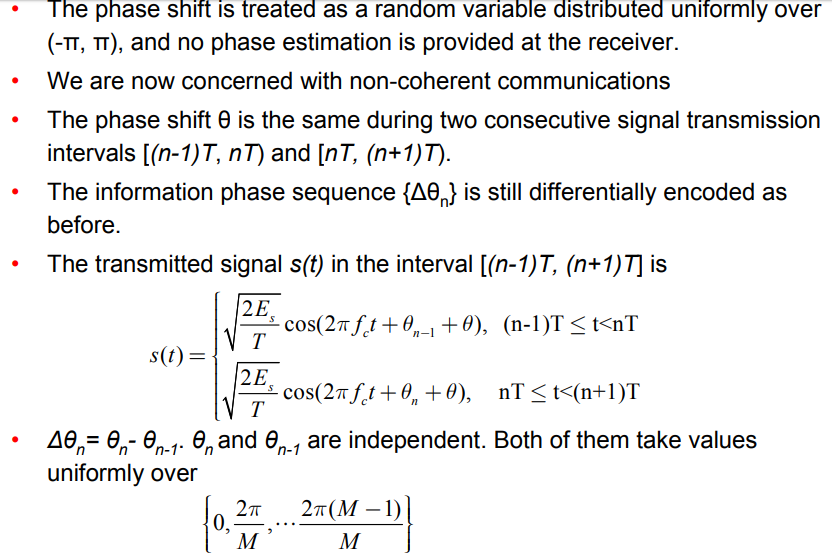

So far, we have discussed different modulation techniques. The output of all these techniques is a binary sequence, represented as 1s and 0s

A phase diagram and signal constellation diagram for the case of M = 8 are shown below:

Fig: phase diagram and signal constellation

M-ary QAM

The QAM modulator essentially follows the idea that can be seen from the basic QAM theory where there are two carrier signals with a phase shift of 90° between them. These are then amplitude modulated with the two data streams known as the I or In-phase and the Q or quadrature data streams. These are generated in the baseband processing area.

Basic QAM I-Q modulator circuit

The two resultant signals are summed and then processed as required in the RF signal chain, typically converting them in frequency to the required final frequency and amplifying them as required.

Fig.: Basic QAM

It is worth noting that as the amplitude of the signal varies any RF amplifiers must be linear to preserve the integrity of the signal. Any non-linearities will alter the relative levels of the signals and alter the phase difference, thereby distorting he signal and introducing the possibility of data errors.

Basic QAM I-Q demodulator circuit

The basic modulator assumes that the two quadrature signals remain exactly in quadrature.

A further requirement is to derive a local oscillator signal for the demodulation that is exactly on the required frequency for the signal. Any frequency offset will be a change in the phase of the local oscillator signal with respect to the two double sideband suppressed carrier constituents of the overall signal.

Systems include circuitry for carrier recovery that often utilises a phase locked loop - some even have an inner and outer loop. Recovering the phase of the carrier is important otherwise the bit error rate for the data will be compromised.

Fig.: Basic QAM demodulator

The circuits shown above show the generic IQ QAM modulator and demodulator circuits that are used in a vast number of different areas. Not only are these circuits made from discrete components, but more commonly they are used within integrated circuits that are able to provide a large number of functions.

Key Takeaways:

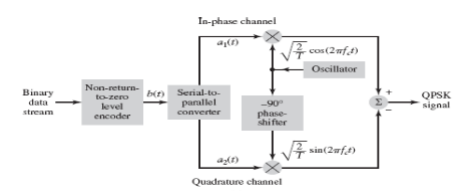

1. Error Probability

2. The number of bits necessary to produce a given number of conditions is expressed mathematically as

N=log2M

Reference:

1. P Ram krishna Rao, Digital Communication, Mc Graw Hill Publication

2. Ha Nguyen, Ed Shwedyk, ―A First Course in Digital Communication‖, Cambridge

University Press.

3. B P Lathi, Zhi Ding ―Modern Analog and Digital Communication System‖, Oxford

University Press, Fourth Edition.

4. Bernard Sklar, Prabitra Kumar Ray, ―Digital Communications Fundamentals and

Applications‖ Second Edition, Pearson Education

5. Taub, Schilling, ―Principles of Communication System‖, Fourth Edition, McGraw Hill.