Unit-4

Assembly Language Programming based on Intel 8085/8086

4.1.1 Instructions

An instruction is a binary pattern designed inside a microprocessor to perform a specific function.

- The entire group of instructions that a microprocessor supports is called Instruction Set.

- 8085 has 246 instructions.

- Each instruction is represented by an 8-bit binary value.

- These 8-bits of binary value is called Op-Code or Instruction Byte.

4.1.2 Data Transfer Instructions

These instructions transfer data between registers or between memory and registers. These instructions are used to copy data from source to destination. While copying, the contents of source cannot be modified.

OPCODE | OPERAND | DESCRIPTION |

MOV | Rd, Rs Rd, M M, Rs | Transfer the contents of the source to the destination. |

MVI | Rd, data M, data | Move immediate data into the destination register |

LXI | Reg. pair, data | Move 16 bit data into the register pair |

LDA | 16 bit address | Load accumulator with data present at the specified address |

XCHG | - | Exchange the contents of HL with DE |

For example: MOV B, C

MVI B, 20H

LXI H, 4020H

LDA 6000H

4.1.3 Arithmetic Instructions

These instructions perform the operations like:

• Addition

• Subtraction

• Increment

• Decrement

OPCODE | OPERAND | DESCRIPTION |

ADD | R M | Add the contents of register with the contents of accumulator and save in accumulator. |

ADC | R M | Add the contents of register with the contents of accumulator with carry and save in accumulator. |

ADI | 8 bit data | Add data with the content of acc |

DAD | Reg pair | Add register pair to H-L pair |

SUB | R M | Subtract the contents of register with the contents of accumulator and save in accumulator. |

SBB | R M | Subtract the contents of register with borrow from the contents of accumulator and save in accumulator. |

SUI | 8 bit data | Subtract data with the content of acc |

INR | R M | Increment register or memory by 1 |

DCR | R M | Decrement register or memory by 1 |

For example: ADD C

ADC M

ADI 40H

DAD HL

SUB B

SUI 20H

INR C

4.1.4 Logical Instructions

The logical operations are:

• AND • OR • XOR • Rotate • Compare • Complement

OPCODE | OPERAND | DESCRIPTION |

CMP | R M | Compare the contents of register or memory with accumulator |

ANA | R M | Logical AND the contents of register with accumulator |

ANI | 8 bit data | Logical AND the data with accumulator |

XRA | R M | XOR the contents of register with accumulator |

ORA | R M | Logical OR the contents of register with accumulator |

RLC | - | Rotate accumulator left |

RRC | - | Rotate accumulator right |

CMA | - | Complement accumulator |

For example: CMP C

ANA B

ANI 40H

XRA M

ORA C

RLC

4.1.5 Branch Operation Instructions

These instructions alter the normal sequential flow conditionally or unconditionally.

OPCODE | OPERAND | DESCRIPTION |

JMP | 16 bit address | Jump unconditionally to the given location |

JC | 16 bit address | Jump if carry |

JNC | 16 bit address | Jump if no carry |

JZ | 16 bit address | Jump if zero |

JNZ | 16 bit address | Jump if no zero |

CALL | 16 bit address | Call unconditionally |

RET | - | Return unconditionally |

RST | 0-7 | Restart (Software Interrupts) |

For example: JMP 2000H

RET

RST 6

Key takeaway

We use instructions to perform various operations. They are the codes written by the user to instruct the microprocessor to perform several operations like arithmetical, logical etc.

Continuous Loop

The loop formed by using unconditional jump instruction. This loop will follow the instructions and repeat the same task until the system is reset.

Conditional Loop

The conditional jump instruction set up a conditional loop. These instructions check the flags such as zero, carry etc and then repeat the specified task if that condition is satisfied. These loops include counting and indexing.

Indexing means to refer objects with sequential numbers. The counting is set up by loading specific count value in the register. It can be incremental or decremental.

Key takeaway

Continuous Loop

The loop formed by using unconditional jump instruction. This loop will follow the instructions and repeat the same task until the system is reset.

Conditional Loop

These loops include counting and indexing.

Example-1

Write a program to add two 8-bit numbers.

MEMORY ADDRESS | MNEMONICS | COMMENTS |

3000 | LDA 3050 |

|

3003 | MOV H, A | A -> H |

3004 | LDA 3051 | A<-[2051] |

3007 | ADD H | A + H -> A |

3006 | MOV L, A | A -> L |

3007 | MVI A 00 | 00 -> A |

3009 | ADC A | A+A+carry -> A |

300A | MOV H, A | A -> H |

300B | SHLD 4050 | H→4051, L→4050 |

300E | HLT |

|

Explanation:

- LDA 3050 moves the contents of 3050 memory location to the accumulator (A).

- MOV H, A copies contents of accumulator to register H .

- LDA 3051 moves the contents of 3051 memory location to the accumulator.

- ADD H adds contents of A and H. The result is then stored in A.

- MOV L, A copies contents of A to L.

- MVI A 00 moves immediate data (i.e., 00) to A.

- ADC A adds contents of A(00), contents of register specified (i.e A) and carry (1).

- MOV H, A copies contents of A (01) to H.

- SHLD 4050 moves the contents of L register in 4050 memory location and contents of H register in 4051 memory location.

- HLT stops program execution.

Example-2 Write a program to subtract two 8-bit numbers

Mnemonics | Operand | Comments |

LXI H, | 3502 H | Get address of 2nd no. in H-L pair. |

MVI A, | 99 | Place 99 in accumulator. |

SUB | M | 9’s compliment of 2nd no. |

INR | A | 10’s compliment of 2nd no. |

DCX | H | Get address of 1st no. |

ADD | M | Add 1st no. & 10’s compliment 2nd no. |

DAA |

| Decimal Adjustment. |

STA | 3503 H | Store result in 3503 H. |

HLT

|

| Stop the program. |

DATA

3501- 96 H.

3502- 38 H.

The result is stored in memory location 3503 H.

RESULT

2503- 58 H.

Example-3

Write a program to add two 16-bit numbers.

We are taking two numbers ABCD + FE2D = 1B9FA

INPUT:

…. | … |

5000H | CD |

5001H | AB |

5002H | 2D |

5003H | FE |

… | …. |

PROGRAM:

Labels | Mnemonics | Operand | Comments |

| LXI H, | 5000H | Point to LSB of first operand |

| LXI D, | 5002H | Point to LSB of second address |

| LDAX | D | Load Acc with content pointed by DE |

| ADD | M | Add memory element pointed by HL with Acc |

| MOV C, | A | Store LSB result at C |

| INX | H | Point to next byte of first operand |

| INX | D | Point to next byte of second operand |

| LDAX | D | Load Acc with content pointed by DE |

| ADC | M | Add memory element pointed by HL with Acc+ Carry |

| MOV B, | A | Store the MSB at B |

| MOV H, | B | Move B to H |

| MOV L, | C | Move C to L |

| SHLD | 5050H | Store the result at 5050H and 5051H |

| JNC | DONE | Skip to end |

| MVI A, | 01H | Load 1 to Acc |

| STA | 5052H | Store Acc content into 5052H |

DONE: | HLT |

| Stop the program. |

RESULT:

5052: FA

5053: B9

5054: 01

Example-4

WAP for finding lowest & highest no. in data array

WAP for finding lowest no. in data array

Labels | Mnemonics | Operand | Comments |

| LXI H, | 5000H | Address for count in H-L pair |

| MOV C, | M | Count in C register |

| INX | H | Address for 1st no. |

| MOV A, | M | 1st no. sent to the accumulator |

| DCR | C | Decrement count |

LOOP: | INX | H | Address of next no. |

| CMP | M | Compare next no. |

| JC | AHEAD | If no, get smaller no. in accumulator go to AHEAD |

| MOV A, | M | get smaller no. in accumulator |

AHEAD: | DCR | C | Decrement count |

| JNZ | LOOP |

|

| STA | 4000H | Store in 4000H |

| HLT |

| Stop program |

DATA:

5000H : 03

5001H : 75

5002H : 98

5003H : 99

RESULT:

4000H : 03

WAP for finding highest no. in data array

Labels | Mnemonics | Operand | Comments |

| LXI H, | 5000H | Address for count in H-L pair |

| MOV C, | M | Count in C register |

| INX | H | Address for 1st no. |

| MOV A, | M | 1st no. sent to the accumulator |

| DCR | C | Decrement count |

LOOP: | INX | H | Address of next no. |

| CMP | M | Compare next no. |

| JNC | AHEAD | If no, go to AHEAD |

| MOV A, | M | Or get larger no. in accumulator |

AHEAD: | DCR | C | Decrement count |

| JNC | LOOP |

|

| STA | 4000H | Store in 4000H |

| HLT |

| Stop program |

DATA:

5000H : 03

5001H : 75

5002H : 98

5003H : 99

RESULT:

4000H : 99

Counters are used to keep track of events. They can be used in any program by loading specific count value in a register through INR or DCR instructions. Time delays are used to set up accurate timing between two events. In time delay a register is loaded with a number (which is the required delay) and the register is decremented until zero is reached. The delay is caused by the clock period of the system.

Time delay using one register

For the instructions below

Instruction | Comment | T-states |

MVI B, FFH | Load Register B with FH | 7 |

Loop: DCR B | Decrement B | 4 |

JNZ Loop | Jump back to decrement B | 10/7 |

Now, Let the operating frequency f=2MHz

Then, T=1/f = 0.5μsec

Time delay in loop TL = N10 x No. of T-states in loop x T

= 255x (7+4+ ) x 0.5

) x 0.5

= 1785 μ sec

= 1.8msec

N10: Decimal value of count in delay register

The last cycle requires only 7T states not 10T states as it will not jump back to decrement instruction. So, the adjusted time delay TLA will be

TLA = TL – 3T

= 1785 – (3x0.5)

= 1.8msec

Time delay outside the loop To will be

To = No. of T-states x T [For MVI instruction]

=7 x 0.5

= 3.5 μ sec

Total time delay = TLA +To

= 1785 μ sec +3.5 μ sec

= 1787 μ sec

Time delay using Register Pair

Instructions | Comments | T-states |

LXI B,2384 | Load BC with 2384 | 10 |

xxx: DCX B | Decrement B by 1 | 6 |

MOV A,C | Move value in C to A | 4 |

ORA B | OR B with C to set zero flag | 4 |

JNZ:xxx | Jump if not zero | 10/7 |

Now, Let the operating frequency f=2MHz

Then, T=1/f = 0.5μsec

Time delay in loop TL = N10 x No. of T-states in loop x T

(2384)H= (9092)10

TL = 9092x24x0.5

=109msec

The instruction LXI will add 5 μ sec as instruction outside the loop. The total delay will now become

Total time delay = TL +To

= 109 msec+ 5 μ sec

= 109msec

Time delay loop in loop technique

Instructions | Comments | T-states |

MVI B, 38H | Move count 38 to B | 7 |

Loop2 MVI C, FFH | Move count FF to C | 7 |

Loop1 DCR C | Decrement value of C by 1 | 4 |

JNZ: Loop1 | Jump to DCR if not zero | 10/7 |

DCR B | Decrement count of B by 1 | 4 |

JNZ: Loop2 | Jump to Location of Loop 2 if not zero | 10/7 |

Here we calculate

Time delay in Loop1 as calculated in time delay using one register

TL1 = 1787μsec

Time delay inside Loop 2 = N10 (TL1+No. of T-states in loop xT)

= 56(1787+21x0.5)

= 100.46msec

Time delay outside the loop To = 7xT = 7x0.5 = 3.5 μsec

Now Total Time Delay = Time delay inside Loop 2+ Time delay outside the loop

= 100.46msec + 3.5 μsec

=10.46msec

Example-1

Write a program for delay subroutine using register

- The microprocessor does not execute other tasks, when the delay subroutine is executed.

- For the delay, we use the instruction execution times.

- Execution of some instructions in a loop, the delay can be generated.

- Some methods for generating delays are as follows:

- Using NOP instructions

- Using 8-bit register as counter

- Using 16-bit register pair as counter.

Using NOP instructions

- It takes four clock pulses for fetching, decoding and executing.

- If the 8085 MPU is working on 4MHz clock frequency, then the internal clock frequency is 2MHz.

- Hence, can easily determine that each clock period is 1/2 of a microsecond.

- So the NOP will be executed in 1/2 * 4 = 2µs.

- If the entire memory uses NOP instruction, then 64K NOP instructions will be executed. Then the overall delay will be 216 * 2µs = 131072µs.

- Hence, it can be used to generate a short time delay of few milliseconds.

Using 8-bit register as counter

Labels | Mnemonics | Operand | Comments |

| MVI B, | FFH | 7 T states required |

LOOP: | DCR | B | 4 T states required and will be executed 255 (FF) times |

| JNZ | LOOP | 10 T states required when it jumps (It jumps 254 times), otherwise it take 7 T-States |

| RET |

| 10 T states required |

7 + ((4*255) + (10*254)) + 7 + 10 = 3584.

So the time delay will be 3584 * 1/3µs = 1194.66µs.

So when small delay is needed, then we can use this technique with some other values in the place of FF.

Using 16-bit register pair as counter

Labels | Mnemonics | Operand | Comments |

| LXI B, | FFFFH | 10 T states required |

LOOP: | DCX | B | 6 T states required |

| MOV A, | B | 4 T states required |

| ORA | C | 4 T states required |

| JNZ | LOOP | 10 T states required when it jumps, otherwise it take 7 T-States |

| RET |

| 10 T states required |

10 + (6 + 4 + 4 + 10) * 65535H – 3 + 10 = 17 + 24 * 65535H = 1572857.

Time delay = 1572857 * 1/3µs = 0.52428s.

Here we are getting nearly 0.5s delay.

Key takeaway

For Time delay using one register

Time delay in loop TL = N10 x No. of T-states in loop x T

The adjusted time delay TLA will be

TLA = TL – 3T

Time delay outside the loop To will be

To = No. of T-states x T

Time delay loop in loop technique

Time delay in Loop1 as calculated in time delay using one register TL1

Time delay inside Loop 2 = N10 (TL1+No. of T-states in loop xT)

Time delay outside the loop To

Now Total Time Delay = Time delay inside Loop 2+ Time delay outside the loop

Stack is set of memory locations which are specified by the programmer in main program. These memory locations are used to store binary information temporarily during execution of program. The stack is shared by programmer and the microprocessor. There is a 16-bit memory address in stack pointer register (SP) of microprocessor. LXI SP, memory address instruction is used to load the SP with specific memory address.

The Stack is assigned the highest memory location so that the program is not affected. By using PUSH instruction, the data bytes in the register pair can be stored in the stack in reverse order. Using POP instruction, they can be again transferred to the respective registers.

The address in the SP register indicates the next two memory locations which are in descending order can be used for storage.

Example-1

LXI SP, xx99H | Load SP register with address xx99 |

PUSH H | It copies content of register pair (HL) on stack [H:xx98,L:xx97]. The SP register is decremented each time [SP = xx97] |

PUSH B | It copies content of register pair (BC) on stack [B:xx96, C:xx95] The SP register is decremented each time [SP = xx95] |

PUSH PSW | It is program status word which means content of A and F [A:xx94, F: xx93]. The SP register is decremented each time [SPxx93] |

POP H | It copies content of top 2 memory locations to HL. [H: xx94, L: xx93]. The SP is incremented each time [SP: xx95] |

POP B | It copies content of top 2 memory locations to HL. [H: xx95, L: xx96]. The SP is incremented each time [SP: xx97] |

POP PSW | It is program status word which means content of A and F [A: xx98, F: xx97]. The SP register is incremented each time [SP: xx99] |

Subroutine

Example-1

Memory location | Instruction |

2000H | LX SP, 2300H |

2040H | CALL 2070H |

2043H | Next Instruction |

The CALL instruction requires 5 machine cycles and 18 T-states. The machine cycles are explained below.

M1 Opcode Fetch: The content of program counter 2040 are placed on address bus and the machine code is fetched using data bus. In the same time the program counter is incremented by one. So, now the new value in program counter is 2041H. After instruction is decoded and executed SP is decremented by 1. This machine cycle needs 6T-states.

M2-M3: These two are memory read cycles. The 16-bit address of CALL which is 2070H is fetched. The lower order 70H is fetched first and placed in internal register Z. Next the higher order address is fetched which is 20H and placed in register W. For machine cycle M3 the program counter is upgraded to location pointing next instruction. The both machine cycles require 3T states each.

M4-M5: It is storing of program counter. When M4 begins the content of SP register 23FFH is placed on address bus. The higher order is placed on the data bus 20H and stored in stack location 23FFH. Then simultaneously the SP is also decremented by 1(23FEH). In M5 the content of SP is placed on address bus and lower byte of program counter 43H is placed on data bus and stored in stack location 23FEH. The both machine cycles require 3T states each.

RET Execution

At the end of subroutine RET is executed. The program sequence is transferred to 2043H location. This was stored in top two stack locations 23FEH and 23FFH in CALL instruction. The RET requires 3 machine cycles. M1 is the opcade fetch. In M2 content of SP are placed on address bus. The data byte 43H from top of stack is fetched first and stored in Z and SP is incremented by 1. The next byte is copied in M3 i.e 20H and stored in W and SP is again incremented by 1(2400H).

Key takeaway

The Stack is assigned the highest memory location so that the program is not affected. By using PUSH instruction, the data bytes in the register pair can be stored in the stack in reverse order. Using POP instruction, they can be again transferred to the respective registers.

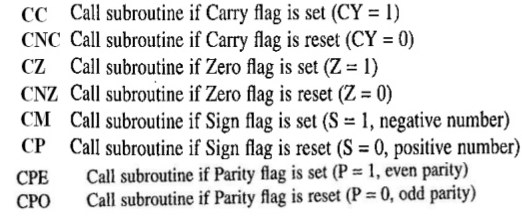

Conditional call Instructions

|

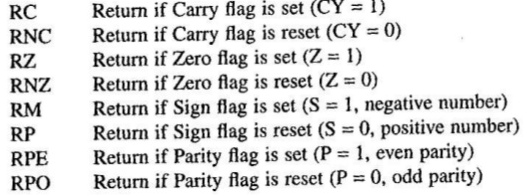

Conditional Return Instructions

|

Reference:

1. Gaonkar, Ramesh S , “Microprocessor Architecture, Programming and Applications with 8085”, Penram International Publishing.

2. Ray A K, Bhurchandi K M, “Advanced Microprocessors and Peripherals”, TMH Hall D V, Microprocessor Interfacing’, TMH

3.Liu and, “Introduction to Microprocessor”, TMH

4. Brey, Barry B, “INTEL Microprocessors”, PHI