UNIT-3

PIC Interrupts & Interfacing-I

Interrupt:

- Interrupt is a hardware mechanism in which, the device notices the CPU that it requires its attention. Interrupt can take place at any time.

- So when CPU gets an interrupt signal trough the indication interrupt-request line, CPU stops the current process and respond to the interrupt by passing the control to interrupt handler which services device.

- In interrupt, the device notices the CPU that it requires its attention.

- An interrupt is not a protocol, its a hardware mechanism.

- In interrupt, the device is serviced by interrupt handler.

- Interrupt can take place at any time.

- In interrupt, interrupt request line is used as indication for indicating that device requires servicing.

- In interrupts, processor is simply disturbed once any device interrupts it.

Polling:

- In polling is not a hardware mechanism, its a protocol in which CPU steadily checks whether the device needs attention.

- Wherever device tells process unit that it desires hardware processing, in polling process unit keeps asking the I/O device whether or not it desires CPU processing.

- The CPU ceaselessly check every and each device hooked up thereto for sleuthing whether or not any device desires hardware attention.

- Each device features a command-ready bit that indicates the standing of that device, i.e., whether or not it’s some command to be dead by hardware or not.

- If command bit is ready one, then it’s some command to be dead else if the bit is zero, then it’s no commands.

- Whereas, in polling, CPU steadily checks whether the device needs attention.

- Whereas it isn’t a hardware mechanism, its a protocol.

- While in polling, the device is serviced by CPU.

- Whereas CPU steadily ballots the device at regular or proper interval.

- While in polling, Command ready bit is used as indication for indicating that device requires servicing.

- On the opposite hand, in polling, processor waste countless processor cycles by repeatedly checking the command-ready little bit of each device.

- The intermediate value theorem describes a key property of continuous functions: for any function that's continuous over the interval [a,b][a,b]open bracket, a, comma, b, close bracket, the function will take any value between f(a)f(a)f, left parenthesis, a, right parenthesis and f(b)f(b)f, left parenthesis, b, right parenthesis over the interval.

- More formally, it means that for any value LLL between f(a)f(a)f, left parenthesis, a, right parenthesis and f(b)f(b)f, left parenthesis, b, right parenthesis, there's a value ccc in [a,b][a,b]open bracket, a, comma, b, close bracket for which f(c)=Lf(c)=Lf, left parenthesis, c, right parenthesis, equals, L.

- This theorem makes a lot of sense when considering the fact that the graphs of continuous functions are drawn without lifting the pencil.

- If we know the graph passes through (a,f(a))(a,f(a))left parenthesis, a, comma, f, left parenthesis, a, right parenthesis, right parenthesis and (b,f(b))(b,f(b))left parenthesis, b, comma, f, left parenthesis, b, right parenthesis, right parenthesis...

|

Fig.1. IVT

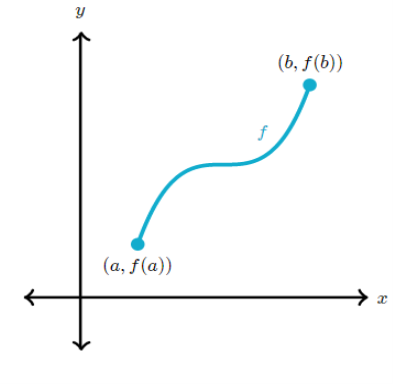

- then it must pass through any yyy-value between f(a)f(a)f, left parenthesis, a, right parenthesis and f(b)f(b)f, left parenthesis, b,

right parenthesis.

|

Fig.2. IVT

- The program associated with the interrupt is called the interrupt service and routine (ISR).

- Step in executing an Interrupt:

1. It finish the instruction it is executing and saves the address of the next instruction (PC) on the stack.

2. It also saves the current status of all the interrupt internally.

- The sequence of steps that occurs during interrupt processing are:

- The contents of flag register the CS and IP are pushed on to the stack.

- To disable single steps and INTR interupts the TF and IF are cleared.

- The program then jumps to the beginning or starting address of ISS.

- When the IRET executes last line that are also ISS last line the CS and IP flag contents are popped from stack and placed in appropriate registers.

- Once the flags are restored then Tf and IF values are also restored to their previous values.

- Then it continues the process which was doing before interrupt.

- Internal interrupts

- External interrupt

- Exceptions

- Non-maskable interrupts

- Software interrupts

- Internal interrupts:

- Internal interrupts are those that are generated by on-chip peripherals such as serial and parallel ports.

- With an external peripheral, the device will normally assert an external pin which is connected to an interrupt pin on the processor.

- With internal peripherals, this connection is already made.

- Some integrated processors allow some flexibility concerning these hardwired connections and allow the priority level to be adjusted or even masked out or disabled altogether.

- External interrupts:

- External interrupts are the common method of connecting external peripherals to the processor.

- They are usually provided through external pins that are connected to peripherals and are asserted by the peripheral.

- For example, a serial port may have a pin that is asserted when there is data present within its buffers.

- The pin could be connected to the processor interrupt pin so that when the processor sees the data ready signal as an interrupt.

- The corresponding interrupt service routine would then fetch the data from the peripheral before restoring the previous processing.

- Exceptions:

- Many processor architectures use the term exception as a more generic term for an interrupt.

- While the basic definition is the same (an event that changes the software flow to process the event) an exception is extended to cover any event, including internal and external interrupts, that causes the processor to change to a service routine.

- Typically, exception processing is normally coupled with a change in the processor’s mode. This will be described in more detail for some example processors later in this chapter.

- The range of exceptions can be large and varied. A MC68000 has a 256 entry vector table which describes about 90 exception conditions with the rest reserved for future expansion.

- An 8 bit micro may have only a few.

- Software interrupt:

- The advantage of an interrupt is that it includes a mechanism to change the program flow and in some processor architectures, to change into a more protected state.

- This means that an interrupt could be used to provide an interface to other software such as an operating system.

- This is the function that is provided by the software interrupt.

- It is typically an instruction or set of instructions that allows a currently executing software sequence to change flow and return using the more normal interrupt mechanism.

- With devices like the Z80 this function is provided by the SWI (software interrupt instruction).

- With the MC68000 and PowerPC architectures, the TRAP instruction is used.

- Non-maskable interrupt:

- A non-maskable interrupt (NMI) is as its name suggests an external interrupt that cannot be masked out.

- It is by default at the highest priority of any interrupt and will always be recognized and processed.

- In terms of a strict definition, it is masked out when the ISR starts to process the interrupt so that it is not repeatedly recognized as a separate interrupt and therefore the non-maskable part refers to the ability to mask the interrupt prior to its assertion.

- To enable means to allow interrupts at this time.

- Conversely, to disable means to postpone interrupts until a later time.

- On the ARM Cortex-M processor there is one interrupt enable bit for the entire interrupt system.

- The processor services interrupts and exceptions only between the end of one instruction and the beginning of the next.

- When the repeat prefix is used to repeat a string instruction, interrupts and exceptions may occur between repetitions. Thus, operations on long strings do not delay interrupt response.

- Certain conditions and flag settings cause the processor to inhibit certain interrupts and exceptions at instruction boundaries.

- An interrupt control register, or ICR, is a hardware register in a computer chip used to configure the chip to generate interrupts to raise a signal on an interrupt line in response to some event occurring within the chip or a circuit connected to the chip.

- IMR

- ICR

- ISR

- IPR

- ICR:

- An interrupt control register, or ICR, is a hardware register in a computer chip used to configure the chip to generate interrupts—to raise a signal on an interrupt line—in response to some event occurring within the chip or a circuit connected to the chip.

- An Interrupt Control is usually used in Micro controllers to generate interrupts signals which tells the CPU to pause its current task and start executing another set of predefined activities.

- ISR: ISR is an integrated intelligence and operations function that can be defined as a coordinated acquisition, processing, and provision of accurate, relevant, timely information and intelligence to support a commander's decision making process.

- A priority interrupt is a system which decides the priority at which various devices, which generates the interrupt signal at the same time, will be serviced by the CPU.

- The system has authority to decide which conditions are allowed to interrupt the CPU, while some other interrupt is being serviced.

- Generally, devices with high speed transfer such as magnetic disks are given high priority and slow devices such as keyboards are given low priority.

- When two or more devices interrupt the computer simultaneously, the computer services the device with the higher priority first.

Key Takeaway:

- Interrupt is a hardware mechanism in which, the device notices the CPU that it requires its attention. Interrupt can take place at any time.

- In polling is not a hardware mechanism, it’s a protocol in which CPU steadily checks whether the device needs attention.

- A priority interrupt is a system which decides the priority at which various devices, which generates the interrupt signal at the same time, will be serviced by the CPU.

- The program associated with the interrupt is called the interrupt service and routine (ISR).

- An interrupt control register, or ICR, is a hardware register in a computer chip used to configure the chip to generate interrupts to raise a signal on an interrupt line in response to some event occurring within the chip or a circuit connected to the chip.

3.8.1 Timer using interrupts:

- The timer interrupts IT0 and IT1 are related to Timers 0 and 1, respectively.

- The interrupt programming for timers involves following steps :

- Configure TMOD register to select timer(s) and its/their mode.

- Enable Timer Interrupt by configuring bits of IE register.

- Start timer by setting timer run bit TRx.

- Write subroutine for Timer Interrupt. The interrupt number is 1 for Timer0 and 3 for Timer1.

- To stop the timer, clear TRx in the end of subroutine. Otherwise it will restart from 0000H in case of modes 0 or 1 and from initial values in case of mode 2.

- If the Timer has to run again and again, it is required to reload initial values within the routine itself (in case of mode 0 and 1). Otherwise after one cycle timer will start counting from 0000H.

- Example code

Timer interrupt to blink an LED; Time delay in mode1 using interrupt method // Use of Timer mode0 for blinking LED using interrupt method // XTAL frequency 11.0592MHz

#include<reg51.h> sbit LED = P1^0; //LED connected to D0 of port 1

void timer(void) interrupt 1 //interrupt no. 1 for Timer 0 { led=~led; //toggle LED on interrupt TH0=0xFC; // initial values loaded to timer TL0=0x66; } main() { TMOD = 0x01; // mode1 of Timer0 TH0 = 0xFC; // initial values loaded to timer TL0 = 0x66; IE = 0x82; // enable interrupt TR0 = 1; //start timer while(1); // do nothing }

|

3.8.2 External hardware interrupts

- The external interrupts are the interrupts received from the (external) devices interfaced with the microcontroller. They are received at INTx pins of the controller.

- These can be level triggered or edge triggered. In level triggered, interrupt is enabled for a low at INTx pin; while in case of edge triggering, interrupt is enabled for a high to low transition at INTx pin. The edge or level trigger is decided by the TCON register.

- The TCON register has following bits:

- Bit Values of TCON Register of 8051 Microcontroller

|

Fig.3 Bit Values of TCON

2. Setting the IT0 and IT1 bits make the external interrupt 0 and 1 edge triggered respectively.

3. By default these bits are cleared and so external interrupt is level triggered.

4. For a level trigger interrupt, the INTx pin must remain low until the start of the ISR and should return to high before the end of ISR.

5. If the low at INTx pin goes high before the start of ISR, interrupt will not be generated.

6. Also if the INTx pin remains low even after the end of ISR, the interrupt will be generated once again.

7. This is the reason why level trigger interrupt (low) at INTx pin must be four machine cycles long and not greater than or smaller than this.

8. Following are the steps for using external interrupt :

- Enable external interrupt by configuring IE register.

- Write routine for external interrupt. The interrupt number is 0 for EX0 and 2 for EX1 respectively.

9. Example code

//Level trigger external interrupt void main() { IE = 0x81; while(1); } void ISR_ex0(void) interrupt 0 { <body of interrupt> }

|

3.8.3 Serial communication interrupts:

- To use the serial interrupt the ES bit along with the EA bit is set.

- Whenever one byte of data is sent or received, the serial interrupt is generated and the TI or RI flag goes high.

- Here, the TI or RI flag needs to be cleared explicitly in the interrupt routine (written for the Serial Interrupt).

- The programming of the Serial Interrupt involves the following steps:

1. Enable the Serial Interrupt (configure the IE register).

2. Configure SCON register.

3. Write routine or function for the Serial Interrupt. The interrupt number is4.

4. Clear the RI or TI flag within the routine.

- Example code

Send ‘A’ from serial port with the use of interrupt // Sending ‘A’ through serial port with interrupt // XTAL frequency 11.0592MHz void main() { TMOD = 0x20; TH1 = -1; SCON = 0x50; TR1 = 1; IE = 0x90; while(1); } void ISR_sc(void) interrupt 4 { if(TI==1) { SBUF = ‘A’; TI = 0; } else RI = 0; }

|

- Light Emitting Diodes or LEDs are the mostly commonly used components in many applications.

- They are made of semiconducting material. In this project, I will describe about basics of Interfacing LED with 8051 Microcontroller.

Principle behind Interfacing LED

- The main principle of this circuit is to interface LEDs to the 8051 family micro controller.

- Commonly, used LEDs will have voltage drop of 1.7v and current of 10mA to glow at full intensity.

- This is applied through the output pin of the micro controller.

- Is very commonly used electronic display module and having a wide range of applications such as calculators, laptops, mobile phones etc.

- 16 x 2 character lcd display is very basic module which is commonly used in electronics devices and projects.

- It can display 2 lines of 16 characters.

- Each character is displayed using 5×7 or 5×10 pixel matrix. Interfacing 16×2 LCD with 8051 using Keil C is bit complex because there is no powerful libraries in Keil C.

- To solve this problem we have developed an LCD library which includes commonly used features, you just need to include our header file and use it. You can download the header file at the bottom of this article.

- In Embedded system design, matrix keypad (4x4, 4x3, 3x3 or 5x5) is used for key in the user inputs.

- Similarly character LCD display [16x2, 16x4, 20x2 or 20x4 LCDs] is used for indicating the system status / parameters. This intractable is about interfacing 16×2 LCD and 4x4 matrix keypad with Arduino microcontroller.

- Parts and components

- Arduino Uno board

- 16x2 LCD

- 1 K ohm potentiometer

- 4x4 matrix keypad

- The 16x2 is very common type LCD, with two rows, and each row displays 16 characters of either 5x7 or 5x8 dot matrix characters.

- The LCD is available in a 16 pin package. It consists of back light and contrast adjustment function and each dot matrix has 5×8 dot resolution.

- The 16x2 LCD display is connected to the Arduino (A0,A1,A2,A3,A4,A5) analog IO pins, where those pins are configured as digital in / out, where LCD operates at 4 bit data mode.

- If the display is not visible, adjust the Contrast pot (1K), to make it visible.

- Matrix key pad is arranged by push button switches in rows and columns. In a simple technique, the 16 keys of matrix keypad is connected with 8 digital IOpins of Arduino.

- Usually the keypad scan procedure is

2. The key is decoded through Column selection / Row read.

3. Write HIGH to Column One. And keep rest of the Column to LOW.

4. Scan (Read) the Row One to Row Four, to find the key.

5. Repeat until a key press (are multiple) is identified.

6. The Row pins are connected to 5,4,3 and 2nd digital IO pins of Arduino.

7. The Column pins are connected to 6,7,8 and 9th digital IO pins of Arduino.

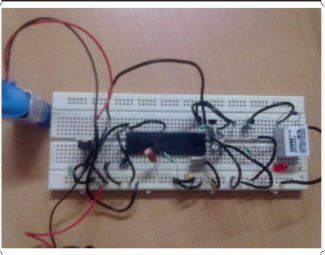

- In this circuit we show the relay and buzzer interfacing with micro controller.

- The relay is a switching device that use to control the high voltage DC/AC through 5v/9v/12v DC.

- The relay work on elector mechanical system. In this device a coil is present which generate the magnetic field when the 5v DC is provided.

- An iron rod is present near the coil which one point connected to the spring.

- The spring force the rod. In this circuit we show the relay and buzzer interfacing with micro controller.

- The relay is a switching device that use to control the high voltage DC/AC through 5v/9v/12v DC.

- The relay work on elector mechanical system. In this device a coil is present which generate the magnetic field when the 5v DC is provided.

- An iron rod is present near the coil which one point connected to the spring.

- The spring force the rod opposite direction of coil. In bottom side of rod two poles are present, one present near the coil and second present other side of coil.

- In normal condition the rod connected to the pole second. When the supply is provided to the coil it attract the rod and it connected to the pole one and connected to the pole one until the coil is magnetized.

- The controlling device like AC bulb, fan etc is connected to the rod and first pole with supply.

- So when we give the 5v the relay your bulb is ON and it ON continuously until the 5v supply is present. The relay require the more current so it connect to the transistor.

- Here we use the NPN transistor so it ON when positive supply is given to the base.

- The coil also store the DC so the stored can be damage the transistor by give the back current so we use the diode in reverse bias to protect the back current.

- The present LED use to indicate the relay condition. The buzzer is use to give the sound.

- Its positive terminal (red wire) is connected to the 5v supply and ground terminal (black wire) is connect to the ground through PNP transistor.

- PNP transistor is ON when ground is given to the base. Here we connect a switch to the P1.0, connect the relay P2.0 and connect the buzzer to the P2.1.

- When we press the switch the buzzer give the sound until the switch is pressed. The first time press the switch the relay is start and work as a dipper.

- After pressing the switch the relay will stop. Again press the switch the relay start the dipper.

|

Fig.4. relay and buzzer interfacing with micro controller

Key Takeaway:

- The timer interrupts IT0 and IT1 are related to Timers 0 and 1, respectively.

- The external interrupts are the interrupts received from the (external) devices interfaced with the microcontroller. They are received at INTx pins of the controller.

- To use the serial interrupt the ES bit along with the EA bit is set.

- The relay work on elector mechanical system.

Reference

1.Peatman, John B, “Design with PIC Microcontroller”, Pearson Education PTE

2.Ramesh Gaonkar, “Fundamentals of Microcontrollers and Applications In Embedded Systems(with the PIC18 Microcontroller Family)”Thomson/Delmar Learning; 1 edition (January 8, 2007), ISBN:978-1401879143

3.Microchip’s PIC18FXXX Data Sheet