UNIT-6

CURRENT TRENDS IN PROCESSOR ARCHITECTURE

- It is a design philosophy aimed at delivering simple but powerful instruction set that executes within a single cycle at high clock speed.

- RISC is an acronym for Reduced Instruction Set Computers.

- CISC – Complex Instruction Set Computer.

- CISC and RISC differ in complexities of their instruction sets where CISC is more complex than RISC.

- Concentrates on reducing the complexity of instructions performed by the hardware to provide greater flexibility and intelligence in software.

- The smaller instruction set allows a designer to implement a hardwired control unit which runs at a higher clock rate than its equivalent micro sequenced control unit.

|

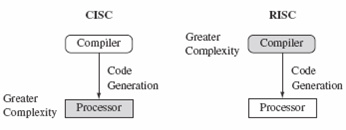

Fig.1. RISC design

- Rule 1. Instructions

Reduced number of instruction classes to provide simple operations that caneach execute in a single cycle.

Each instruction is a fixed length to allow the pipeline to fetch future instructions before decoding the current instruction. (Unlike CISC)

- Rule 2. Pipelines

The processing of instructions is broken down into smaller units that can be executed in parallel by pipelines.

Ideally, the pipeline advances by one step on each cycle for maximum throughput. Instructions can be decoded in one pipeline stage.

- Rule 3. Registers

RISC machines have a large general-purpose register set. Any register can contain either data or an address.(CISC: Have dedicated registers for specific purposes)

- Rule 4. Load-Store Architecture

The processor operates on data held in registers. Separate load and store instructions: transfer data between the register bank and external memory. Because memory accesses are costly.

ARM Processors

ARM Processors can be divided into

- ARM Classic Processors: Arm classic processors include the Arm11, Arm9, and Arm7 processor families. These processors are still widely used around the globe, providing cost-effective solutions for many of today's applications.

- ARM Embedded Processors : Software development for embedded applications includes anything which uses a microcontroller or microprocessor to execute dedicated tasks on its own or within a larger system. Arm supports embedded software development at every stage of the project workflow.

- ARM Application Processors: Advanced RISC machine (ARM) is the first reduced instruction set computer RISC processor for commercial use, which is currently being developed by ARM holdings. ... ARM processor finds applications in digital TVs, set-top boxes, smart phones, mobile, laptops etc.

- ARM Classic processors include ARM7, ARM9 and ARM11 families and ARM7TMDI is still the highest shipping 32-bit processor. ARM7 based processors are still used in many small and simple 32-bit devices.

Version ARM 7:

- ARM7 is a group of older 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use.

- The ARM7 core family consists of ARM700, ARM710, ARM7DI, ARM710a, ARM720T, ARM740T, ARM710T, ARM7TDMI, ARM7TDMI-S, ARM7EJ-S. The ARM7TDMI and ARM7TDMI-S were the most popular cores of the family.

|

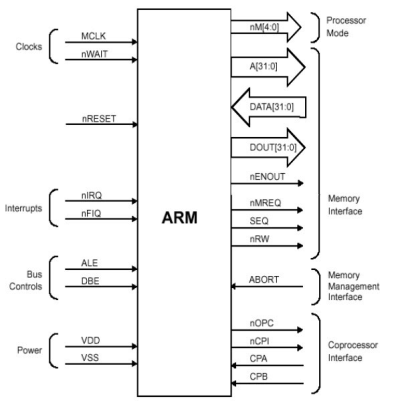

Fig.2. ARM7 FUNCTIONAL DIAGRAM

- The final thing that must be explained is how the ARM will be used and the way in which the chip appear.

- The various signals that interface with the processor are input, output or supervisory signals which will be used to control the ARM operation.

- ARM9 is a group of older 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use.

- The ARM9 core family consists of ARM9TDMI, ARM940T, ARM9E-S, ARM966E-S, ARM920T, ARM922T, ARM946E-S, ARM9EJ-S, ARM926EJ-S, ARM968E-S, ARM996HS.

- Since ARM9 cores were released from 1998 to 2006, they are no longer recommended for new IC designs, instead ARM Cortex-A, ARM Cortex-M, ARM Cortex-R cores are preferred.

- The Arm9 family includes three processors:

- Arm968E-S is the smallest and lowest-power Arm9 processor, built with interfaces for Tightly Coupled Memory and aimed at real-time applications.

- Arm946E-S is a real-time orientated processor with optional cache interfaces, a full Memory Protection Unit, and Tightly Coupled Memory.

- Arm926EJ-S is the entry point processor capable of supporting full Operating Systems including Linux, Windows CE, and Symbian.

Applications of ARM9:

- Consumer type: Smart phones, PDA, Set-Top box, Electronics Toys, Digital Cameras, etc.

- Networking type: Wireless LAN, 802.11, Bluetooth, etc.

- Automatic: Power Train, ABS, Navigation, etc.

- Embedded USB controllers, Bluetooth controllers, Medical scanners, etc.

- Storage: HDD controllers, solid state drivers etc.

- The Arm11 family includes four processors:

- Arm11MPCore introduced multicore technology and is still used in a wide range of applications.

- Arm1176JZ(F)-S is the highest-performance single-core processor in the Classic Arm family. It also introduced Trust Zone technology to enable secure execution outside of the reach of malicious code.

- Arm1156T2(F)-S is the highest-performance processor in the real-time Classic Arm family.

- Arm1136J(F)-S is very similar to Arm926EJ-S, but includes an extended pipeline, basic SIMD (Single Instruction Multiple Data) instructions, and improved frequency and performance.

- ARM11 is the successor to the ARM10, a low-power performance ARM microarchitecture designed by ARM Holdings for the mobile market. This microarchitecture is designed as an IP core and is sold to other semiconductor companies to be implemented in their own chips. The ARM11 was designed by the Arm Sophia-Antipolis design center.

- The ARM11 is a 32-bit RISC processor cores. The ARM11 micro architecture (announced 29 April 2002) introduced the ARMv6 architectural. This micro architecture includes SIMD media instructions, multiprocessor support and a new cache architecture. Learn more in: Automation in Sputum Microscopy: A Hybrid Intelligent Technique in Diagnostic Device Automation.

Features of ARM11:

- Pipeline Depth: 8stage

- Operating frequency: 335MHz.

- Power Consumption: 0.4mW/MHz

- MIPS/MHz: 1.2

- Architecture used: Harvard

- MMU/MPU: Present

- Multiplier unit: 16x32 (16 bits of 32-bit size register)

- Cache Memory: present (4-64k size)

- ISA (Instruction Set Architecture): V6

- Enhanced multiply instruction & saturation

- Powerful ARMV6 instruction set architecture

- Supports the thumb instruction set-memory BW & Size requirements reduces by up to 35%

- Supports Jazelle Technology for efficient embedded JAVA execution

- Supports the DSP extensions

- SIMD media processing extensions deliver up to 2x performance for video processing

- ARM Trust-Zone Technology for on chip security

- Thumb-2 Technology for enhanced performance energy efficiency & code density

- Low power consumption

- High performance integer processor

- Vectored interrupt interface & low-interrupt latency mode speeds up interrupt response & real time performance

- Optional vector floating point co-processor for automotive/ industrial controls & 3D graphics acceleration.

The main features of ARM Processor are mentioned below :

- Multiprocessing Systems –

ARM processors are designed so that they can be used in cases of multiprocessing systems where more than one processors are used to process information. First AMP processor introduced by name of ARMv6K had ability to support 4 CPUs along with its hardware.

- Tightly Coupled Memory –

Memory of ARM processors is tightly coupled. This has very fast response time. It has low latency (quick response) that can also be used in cases of cache memory being unpredictable.

- Memory Management –

ARM processor has management section. This includes Memory Management Unit and Memory Protection Unit. These management systems become very important in managing memory efficiently.

- Thumb-2 Technology –

Thumb-2 Technology was introduced in 2003 and was used to create variable length instruction set. It extends 16-bit instructions of initial Thumb technology to 32-bit instructions. It has better performance than previously used Thumb technology.

2. One cycle execution time –

ARM processor is optimized for each instruction on CPU. Each instruction is of fixed length that allows time for fetching future instructions before executing present instruction. ARM has CPI (Clock Per Instruction) of one cycle.

3. Pipelining –

Processing of instructions is done in parallel using pipelines. Instructions are broken down and decoded in one pipeline stage. The pipeline advances one step at a time to increase throughput (rate of processing).

4. Large number of registers –

Large number of registers are used in ARM processor to prevent large amount of memory interactions. Registers contain data and addresses. These act as local memory store for all operations.

Advantages of ARM Processor :

- Affordable to create –

ARM Processor is very affordable as it does not need expensive equipment’s for its creation. When compare to other processors, it is created at much lesser price. This is why they are apt for making of low cost Mobile phones and other electronic devices.

- Low Power Consumption –

AMP Processors have lesser power consumption. They were initially designed for performing at lesser power. They even have lesser transistors in their architecture. They have various other features that allow for this.

- Work Faster –

ARM performs single operation at a time. This makes it work faster. It has lower latency that is quicker response time.

- Multiprocessing feature –

ARM processors are designed so that they can be used in cases of multiprocessing systems where more than one processors are used to process information. First AMP processor introduced by name of ARMv6K had ability to support 4 CPUs along with its hardware.

- Better Battery Life –

ARM Processors have better battery life. This is seen from administering devices that use ARM processors and those that do not. Those that used ARM processors worked for longer and got discharged later than those that did not work on ARM processors.

- Load store architecture –

The processor uses load store architecture that stores data in various registers (to reduce memory interactions). It has separate load and store instructions that are used to transfer data between external memory and register bank.

- Simple Circuits –

ARM processors have simple circuits; hence they are very compact and can be used in devices that are smaller in size (several devices are becoming smaller and more compact due to customer demands).

Instruction Set for Embedded Systems

- The ARM instruction set differs from the pure RISC definition in several ways that make the ARM instruction set suitable for embedded applications: Variable cycle execution for certain instructions—Not every ARM instruction executes in a single cycle.

- For example, load-store-multiple instructions vary in the number of execution cycles depending upon the number of registers being transferred.

- Inline barrel shifter leading to more complex instructions—The inline barrel shifter is a hardware component that preprocesses one of the input registers before it is used by an instruction.

- Thumb 16-bit instruction set—ARM enhanced the processor core by adding a second 16-bit instruction set called Thumb that permits the ARM core to execute either16- or 32-bit instructions.

- Conditional execution—An instruction is only executed when a specific condition has been satisfied.

- Enhanced instructions—The enhanced digital signal processor (DSP) instructions were added to the standard ARM instruction set to support fast 16×16-bit multiplier operations and saturation.

- The ARM processor controls the embedded device. An ARM processor comprises a core plus the surrounding components that interface it with a bus. These components can include memory management and caches.

- Controllers coordinate important functional blocks of the system. Two commonly found controllers are interrupt controller and memory controller.

- The peripherals provide all the input-output capability external to the chip and are responsible for the uniqueness of the embedded device.

- A bus is used to communicate between different parts of the device.

I. ARM Bus Technology

- Embedded systems use different bus technologies. The most common PC bus technology, the Peripheral Component Interconnect (PCI) bus, this type of technology is external or off-chip.

- Embedded devices use an on-chip bus that is internal to the chip and that allows different peripheral devices to be interconnected with an ARM core.

- There are two different classes of devices attached to the bus.

- Bus master(ARM processor core)—a logical device capable of initiating a data transfer with another device across the same bus.

- Bus slaves(Peripherals)—logical devices capable only of responding to a transfer request from a bus master device.

- A bus has two architecture levels.

- physical level — that covers the electrical characteristics and bus width (16, 32, or 64 bits).

- Second level deals with protocol—the logical rules that govern the communication between the processor and a peripheral.

II. AMBA Bus Protocol

- The Advanced Microcontroller Bus Architecture (AMBA) has been widely adopted as the on-chip bus architecture used for ARM processors.

- The first AMBA buses introduced were the 1.ARM System Bus(ASB) and the2. ARM Peripheral Bus(APB).

- Later ARM introduced another bus design, called the 3. ARM High Performance Bus(AHB).

- Plug-and-play interface for hardware developers — Using AMBA, peripheral designers can reuse the same design on multiple projects.

- A peripheral can simply be bolted onto the on-chip bus without having to redesign an interface for each different processor architecture.

III. Memory

- An embedded system has to have some form of memory to store and execute code.

- It has some specific memory characteristics, such as hierarchy, width, and type.

- Hierarchy-

- All computer systems have memory arranged in some form of hierarchy.

- Memory trade-offs: the fastest memory cache is physically located nearer the ARM processor core and the slowest secondary memory is set further away.

- Cache is placed between main memory and the core. It is used to speed up data transfer between the processor and main memory.

- The main memory is around 256 KB to 256 MB, depending on the application.

- Secondary storage is the largest and slowest form of memory may vary from 600 MB to 60 GB.

2.Width-

- The memory width is the number of bits the memory returns on each access typically 8, 16, 32, or 64 bits. Use of thumb instructions.

- If you have an uncached system using 32-bit ARM instructions and 16-bit-wide memory chips, then the processor will have to make two memory fetches per instruction.

- Each fetch requires two 16-bit loads. This obviously has the effect of reducing system performance, but the benefit is that 16-bit memory is less expensive.

- In contrast, if the core executes 16-bit Thumb instructions, it will achieve better performance with a 16-bit memory.

3.Types-

- Read-only memory (ROM) is the least flexible of all memory types because it contains an image that is permanently set at production time and cannot be reprogrammed.

- Many devices also use a ROM to hold boot code.

- Flash ROM can be written to as well as read, it is slow to write.

- Its main use is for holding the device firmware. The erasing and writing of flash ROM are completely software controlled.

- Dynamic random access memory (DRAM) is the most commonly used RAM for devices. It has the lowest cost per megabyte.

- DRAM is dynamic it needs to have its storage cells refreshed and given a new electronic charge every few milliseconds, so you need to set up a DRAM controller before using the memory.

- Static random access memory (SRAM) is faster .

- The RAM does not require refreshing.

- The access time is shorter. Higher cost.

- Synchronous dynamic random access memory (SDRAM) run at much higher clock speeds and it synchronizes itself.

IV. Peripherals

- Outside world interaction of Embedded Systems.

- A peripheral device performs input and output functions for the chip by connecting to other devices that are off-chip.

- Each peripheral device usually performs a single function.

- Peripherals range from a simple serial communication to complex 802.11 wireless device.

- All ARM peripherals are memory mapped—the programming interface is a set of memory-addressed registers..

- Connect different types of memory to the processor bus.

- On power-up a memory controller is configured in hardware to allow certain memory devices to be active.

- Some memory devices must be set up by software.

- Specialized peripherals called as Controllers that implement higher levels of functionality. Two important types

- Memory controllers-

- Interrupt controllers-An interrupt controller provides a programmable that allows software to determine which peripheral or device can interrupt the processor at any specific time by setting the appropriate bits in the interrupt controller registers.

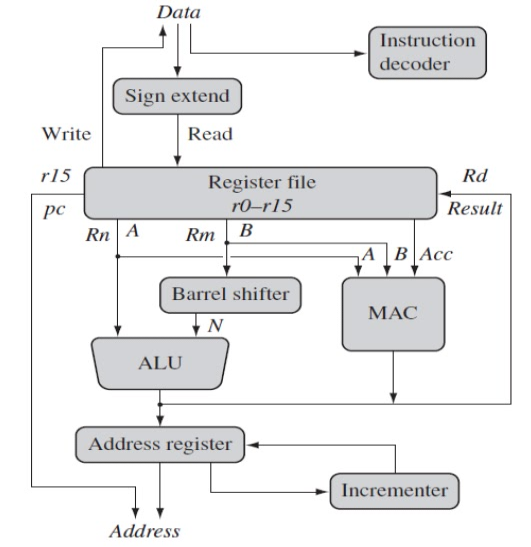

- When an instruction is decoded inside the ARM core and how a particular instruction is executed by interacting with the internal registers file and then send result out of the registers.

|

Fig.4. ARM control flow model.

Features

- Von Neuman Architecture Hence data coming through bus is either instruction or data (same memory).

- The Sign extend hardware converts signed 8-bit & 16-bit numbers to 32-bit values as they are read from memory & placed in a register (for signed values), fill zeros if unsigned.

- Source operands (Rn & Rm) are read from the register file using the internal buses A & B respectively & result Rd is written back.

- The PC value is in the address register which is fed in to the incremented, then the incremented value is copied back in to r15.

- It is also written in to address register to be used as the address for the next instruction fetch.

- ALU: (The Arithmetic & logic Unit) or MAC (multiply & accumulate Unit) takes the register values Rn & Rm from A & B buses & computers a result).

- Data processing instructions write the result in Rd directly to the register file.

- Load & Store instruction use the ALU to generate on Address to be to be held in the address register & broadcast on the address bus.

- It determines which register are active & The access to the CPSR register itself.

- When does ARM enters in particular mode?

Abort | Failed attempt to access memory. |

Fast interrupt request

| Interrupt request arrives through FIQ channel (input).

|

Interrupt request

| Interrupt request arrives through IRQ channel |

Supervisor | After reset. It is generally the mode that an OS . kernel operates in.

|

System | Special version of user mode that allows full read- write access to cpsr.

|

CPSR:

- The CPSR (Current Program Status Register) this stores additional information about the state of the processor: and finally in privileged modes, a particular SPSR (Saved Program Status Register).

- This stores a copy of the previous CPSR value when an exception occurs.

SPSR:

- A Saved Program Status Register (SPSR) stores the current value of the CPSR when an exception is taken so that the CPSR can be restored after handling the exception.

- Each exception handling mode can access its own SPSR.

- User mode and System mode do not have an SPSR because they are not exception handling modes.

- The execution state bits, including the endianness state and current instruction set state can be accessed from the SPSR in any exception mode, using the MSR and MRS instruction.

- You cannot access the SPSR using MSR or MRS in User or System mode.

Implementation of CPSR and SPSR register in ARM

- The ARM architecture provides a total of 37 registers, all of which are 32-bits long. However these are arranged into several banks, with the accessible bank being governed by the current processor mode.

- A particular set of 13 General Purpose Registers (r0 - r12).

- A particular r13 - which is typically used as a stack pointer. This will be a different r13 for each mode, so allowing each exception type to have its own stack.

- A particular r14 - which is used as a link (or return address) register. Again this will be a different r14 for each mode.

- r15 - whose only use is as the Program counter.

- The CPSR (Current Program Status Register) - this stores additional information about the state of the processor:

- And finally in privileged modes, a particular SPSR (Saved Program Status Register).

- This stores a copy of the previous CPSR value when an exception occurs.

- This combined with the link register allows exceptions to return without corrupting processor state.

- Direct use of a block cipher is inadvisable

- Enemy can build up “code book” of plaintext/ciphertext equivalents

- Beyond that, direct use only works on messages that are a multiple of the cipher block size in length

Five standard Modes of Operation:

- Electronic Code Book(ECB),

- Cipher Block Chaining (CBC)

- Cipher Feedback (CFB)

- Output Feedback (OFB)

- Counter (CTR).

ECB:

- Direct use of the block cipher

- Used primarily to transmit encrypted keys

- Very weak if used for general-purpose encryption; never use it for a file or a message.

- Attacker can build up codebook; no semantic security

- We write {P}k → C to denote “encryption of plaintext P with key k to produce ciphertext C”.

CBC:

|

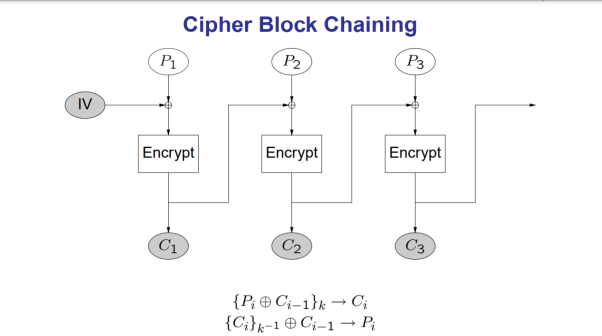

Fig.5.Cipher Block Chaining

- The ciphertext of each encrypted block depends on the IV and the plaintext of all preceding blocks.

- There is a dummy initial ciphertext block C0 known as the Initialization Vector (IV); the receiver must know this value.

- Consider a 4-block message:

C1 = {P1 ⊕ IV }k

C2 = {P2 ⊕ C1}k

C3 = {P3 ⊕ C2}k

C4 = {P4 ⊕ C3}k

- If C2 is damaged during transmission, what happens to the plaintext?

CFB:

- Underlying block cipher used only in encryption mode

- Feedback path actually incorporates a shift register: shift old cipher

- input left by n bits; insert first n bits of previous ciphertext output

- 8-bit CFB is good for asynchronous terminal traffic — but requires

- one encryption for each byte of plaintext

- Errors propagate while bad data is in the shift register — 17 bytes for

- CFB8 when using AES.

- Copes gracefully with deletion of n-bit unit

- Interesting uses: CFB1, CFB8, CFB128

- IV selected the same way as in CBC mode.

OFB:

PROPERTIES OF OFB

- No error propagation

- Active attacker can make controlled changes to plaintext

- OFB is a form of stream cipher

CTR

PROPERTIES OF CTR

- Another form of stream cipher

- Frequently split the counter into two sections: message number and

- block number within the message

- Active attacker can make controlled changes to plaintext

- Highly parallelizable; no linkage between stages

- Vital that counter never repeat for any given key

6.11 DIFFRENCE BETWEEN PIC AND ARM

PIC:

- PIC microcontroller refers to peripheral interface controller.

- Pic microcontrollers are available in 8 bit ,16 bit and 32bit.

- It supports PIC ,UART, USART, CAN ,LIAN , ethernet, SPI ,12S,commucation protocol.

- It has an effective instruction rate of 4 clock cycle per instruction.

- It uses a SRAM ,flash memory.

- It is based on some features of RISC.

- It is based on hardware memory architecture.

- PIC microcontroller family includes PIC16,PIC17,PIC18,PIC24,PIC32.

- It has a very good community support.

- Its manufacturer is microchip.

- It is available with an average cost as compared to the features.

- Popular microcontroller includes PIC18IXX8,PIC32MXX

ARM:

- ARM microcontroller refers to advanced RISC machine.

- ARM microcontroller are available in 32bit mostly also available in 64bit.

- It support UART, USART,SPI,CAN,LAIN, 12C,DSP,SAI commucation protocol.

- It has an effective instruction rate of 1 clock cycle per instruction.

- It uses Flash, SDRAM, EEPROM memory.

- It is based on RISC instruction set architecture.

- It is based on modified Harvard architecture .

- ARM microcontroller family includes ARM v4, 5,6,7 and series.

- It has vast community support.

- Its manufacturers are apple , Nvidia ,Qualcomm, Samsung electronics and TI etc.

- Its available with a low cost as compare to the features.

- Popular microcontrollers include LPC2148, ARM Cortes-MO to ARM cortex M7 etc.

Key Takeaway

- RISC is an acronym for Reduced Instruction Set Computers

- CISC – Complex Instruction Set Computer

- Arm classic processors include the Arm11, Arm9, and Arm7 processor families.

- ARM Processors can be divided into

i)ARM Classic Processors

ii)ARM Embedded Processors :

iii)ARM Application Processors:

5. ARM7 is a group of older 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use.

6. PIC microcontroller refers to peripheral interface controller.

7. PIC microcontroller refers to peripheral interface controlle

Reference:

1.Peatman, John B, “Design with PIC Microcontroller”, Pearson Education PTE

2.Ramesh Gaonkar, “Fundamentals of Microcontrollers and Applications In Embedded Systems(with the PIC18 Microcontroller Family)”Thomson/Delmar Learning; 1 edition (January 8, 2007), ISBN:978-1401879143

3.Microchip’s PIC18FXXX Data Sheet

4.Muhammad Ali Mazidi, SarmadNaimi,“ARM Assembly Language Programming & Architecture”