Unit - 2

Arithmetic and logical instructions

Arithmetic Instructions:

The 8051 can perform addition, subtraction. Multiplication and division operations on 8-bit numbers.

Addition

In this group, we have instructions to

i. Add the contents of A with immediate data with or without carry.

i. ADD A, #45H

ii. ADDC A, #OB4H

ii. Add the contents of A with register Rn with or without carry.

i. ADD A, R5

ii. ADDC A, R2

iii. Add the contents of A with contents of memory with or without carry using direct and indirect addressing

i. ADD A, 51H

ii. ADDC A, 75H

iii. ADD A, @R1

iv. ADDC A, @R0 CY AC, and OV flags will be affected by this operation.

Subtraction

In this group, we have instructions to

i. Subtract the contents of A with immediate data with or without carry.

i. SUBB A, #45H

ii. SUBB A, #OB4H

ii. Subtract the contents of A with register Rn with or without carry.

i. SUBB A, R5

ii. SUBB A, R2

iii. Subtract the contents of A with contents of memory with or without carry using direct and indirect addressing

i. SUBB A, 51H

ii. SUBB A, 75H

iii. SUBB A, @R1

iv. SUBB A, @R0 CY AC, and OV flags will be affected by this operation.

Multiplication

MUL AB.

This instruction multiplies two 8 bit unsigned numbers which are stored in the A and B register. After multiplication, the lower byte of the result will be stored in the accumulator and the higher byte of the result will be stored in the B register.

Eg. MOV A,#45H ;[A]=45H

MOV B,#0F5H ;[B]=F5H

MUL AB ;[A] x [B] = 45 x F5 = 4209 ;[A]=09H, [B]=42H

Division

DIV AB.

This instruction divides the 8-bit unsigned number which is stored in A by the 8-bit unsigned number which is stored in the B register. After division, the result will be stored in the accumulator and the remainder will be stored in the B register.

Eg. MOV A,#45H ;[A]=0E8H

MOV B,#0F5H ;[B]=1BH

DIV AB ;[A] / [B] = E8 /1B = 08 H with remainder 10H ;[A] = 08H, [B]=10H

DA A (Decimal Adjust After Addition).

When two BCD numbers are added, the answer is a non-BCD number. To get the result in BCD, we use DA A instruction after the addition. DA A works as follows.

Eg 1: MOV A,#23H

MOV R1,#55H

ADD A,R1 // [A]=78

DA A // [A]=78 no changes in the accumulator after DAA

Eg 2: MOV A,#53H

MOV R1,#58H ADD A,R1 // [A]=ABh

DA A // [A]=11, C=1 .

ANSWER IS 111. Accumulator data is changed after DAA

LOGICAL Instructions

LOGICAL AND

a. ANL C, BIT (BIT ADDRESS) ;

Logically and carry the content of Bit address and store the result in carrying.

b. ANL C, /BIT;

Logically and carry and complement the content of bit address and store the result in carrying.

Examples:

ANL A, #n ;

AND each bit of A with the same bit of immediate number n, Result is placed in A.

ANL A, add ;

AND each bit of A with the same bit of the direct RAM address, the result is placed in A

ANL A, Rr ;

AND each bit of A with the same bit of register Rr, the result is placed In A.

ANL A, @Rr ;

AND each bit of A with the same bit of the contents of RAM Address in Rp, the result is placed in A.

ANL add, A ;

AND each bit of A with the same bit of the direct RAM address, the result is placed in direct RAM add.

ANL add, #n ;

AND each bit of A with the same bit of the immediate number, the result is placed in direct RAM add.

Find the result of the following code:

MOV A,#57H ; A = 57H

ANL A,#0F0H ; A = A and F0 H

57 H = 0101 0111

F0 H = 1111 0000

0101 0000 = 50H

A = 50H

LOGICAL OR

a. ORL C,BIT(BIT ADDRESS) ;

Logically OR carry the content of bit address and store the result in carrying.

b. ORL C, /BIT;

Logically OR carry and Complement the content of bit address and then store the result in carrying.

Examples

ORL A, #n ;

OR each bit of A with the same bit of immediate number n, Result is placed in A.

ORL A, add ;

OR each bit of A with the same bit of the direct RAM address, the result is placed in A

ORL A, Rr ;

OR each bit of A with the same bit of register Rr, the result is placed in A.

ORL A, @Rr ;

OR each bit of A with the same bit of the contents of RAM Address in Rp, the result is placed in A.

ORL add, A ;

OR each bit of A with the same bit of the direct RAM address, the result is placed in direct RAM add.

ORL add, #n ;

OR each bit of A with the same bit of the immediate number, the result is placed in direct RAM add.

Find the result of the following code:

MOV A,#15H ; A =15H

ORL A,#70H ; A=A OR 70H

Solution:

15 H 0001 0101

70H 0111 0000

0 111 0101 = 75H

A= 75H

LOGICAL XOR

a. XRL C,BIT(BIT ADDRESS) ;

Logically XOR carries the content of bit address and stores the result in carrying.

b. XRL C, /BIT;

Logically XOR carries and Complement the content of the bit address and then stores the result in carrying.

Examples

XRL A, #n ;

XOR each bit of A with the same bit of immediate number n, Result is placed in A.

XRL A, add

XOR each bit of A with the same bit of the direct RAM address, the result is placed in A

XRL A, Rr ;

XOR each bit of A with the same bit of register Rr, the result is placed in A.

XRL A, @Rr ;

XOR each bit of A with the same bit of the contents of RAM Address in Rp, the result is placed in A.

XRL add, A ;

XOR each bit of A with the same bit of the direct RAM address, the result is placed in direct RAM add.

XRL add, #n ;

XOR each bit of A with the same bit of the immediate number, the result is placed in direct RAM add.

Find the result of the following code:

MOV A,#55H ; A = 55H

XRL A,#F0H ; A= A OR F0H

Solution

55 H = 0101 0101

F0 H = 1111 0000

1010 0101 = A5H

A = A5H

CLR bit

a. CLR bit ; Content of Bit Address specified will be cleared.

b. CLR C ; Content of Carry will be cleared.

CPL bit

a. CPL bit; Content of Bit address specified will be complemented.

b. CPL C; Content of carrying will be complemented.

Assembly programs:

Write a program to add two 16-bit numbers. The numbers are 3CE7H and 3B8DH. Place the sum in R7 and R6; R6 should have the lower byte.

CLR C

MOV A,#0E7H ; load the low byte now A = E7 H

ADD A,#8DH ; add the low byte now A =74H and CY=1

MOV R6, A ; save the low byte of the sum in R6

MOV A,#3CH ; load the high byte

ADDC A,#3BH ; add with carry 3B +3C +1 = 78

MOV R7, A ; save the high byte of the sum

Write a program to find the sum of the values. At the end of the program, register A should contain the low byte and R7 the high byte. All values are in hex.

40=(7D) 41=(EB) 42=(C5) 43=(5B) 44=(30)

MOV R0,#40H ; load pointer

MOV R2,#5 ; load counter

CLR A ; A=0

MOV R7, A ; clear R7

AGAIN: ADD A,@R0 ; add the byte pointer to A by R0

JNC NEXT ; if CY=0 don’t accumulate carry

INC R7 ; keep track of carries

INC R0 ; increment pointer

DJNZ R2, AGAIN; repeat until R2 is zero.

Key Takeaways

Boolean instructions

This group of instructions is associated with single-bit operations of 8051.

This includes set, clear, complement, move.

CLR C

The clear instruction can operate on the carry flag.

CLR bit

The CLR instruction can operate on any directly addressable bit.

CLR P2.7

If Port2 has been written as DCH (11011100) then the operation leaves the port set to 5CH

SETB C:

SETB instruction operates on the carry flag and sets the specified bit to 1.

SETB C

sets the carry flag to 1.

SETB instruction operates on any directly-addressable bit and sets the specified bit to1.

Port 2 has the value of 24H(00100100) the Port2 value changes to 25H(00100101)

CPL C

This operation complements the carry flag

CPL C

CPL bit

CPL instruction complements any directly addressable bit.

CPL P2.2

If Port2 has the value 53H 901010011) then after the execution the port set to 55H(01010101).

Program Branching Instructions

Jump and Call Program Range

There are 3 types of jump instructions.

They are:-

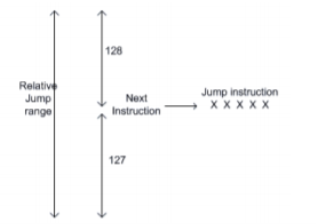

Relative Jump that replaces the PC (program counter) content with a new address that is greater than (the address following the jump instruction by 127 or less) or less than (the address following the jump

Fig 1. Jump instruction

The advantages of the relative jump are as follows:-

1. Only 1 byte of jump address needs to be specified in the 2's complement form, ie. For jumping ahead, the range is 0 to 127 and for jumping back, the range is -1 to -128.

2. Specifying only one byte reduces the size of the instruction and speeds up program execution. 3. The program with relative jumps can be relocated without reassembling to generate absolute jump addresses.

Disadvantages of the absolute jump: -

Instructions that use Relative Jump

SJMP; this is an unconditional jump

The remaining relative jumps are conditional jumps

JC <relative address>

JNC <relative address>

JB bit <relative address>

JNB bit <relative address>

JBC bit <relative address>

CJNE<destination byte> <source byte> <relative address>

DJNZ <byte><relative address

JZ<relative address>

JNZ<relative address>

Short Absolute Jump In this case only 11bits of the absolute jump address are needed. The absolute jump address is calculated in the following manner.

In 8051, 64 kbyte of program memory space is divided into 32 pages of 2 kbyte each. The hexadecimal addresses of the pages are given as follows:-

Page(Hex) | Address(Hex) |

00 | 0000-07FF |

01 | 0800-0FFF |

02 | 1000-17FF |

03 | 1800-1FFF |

……. |

|

1F | F800-FFFF |

The upper 5bits of the program counter (PC) hold the page number and the lower 11bits of the PC hold the address within that page. Thus, an absolute address is formed by taking page numbers of the instruction (from the program counter) following the jump and attaching the specified 11bits to it to form the 16-bit address.

Advantage: The instruction length becomes 2 bytes.

Example of short absolute jump: - ACALL, AJMP

Long Absolute Jump/Call

Applications that need to access the entire program memory from 0000H to FFFFH use a long absolute jump. Since the absolute address has to be specified in the op-code, the instruction length is 3 bytes (except for JMP @ A+DPTR). This jump is not re-locatable.

Example: - LCALL

LJMP

JMP @A+DPTR

Another classification of jump instructions is

1. Unconditional Jump

2. Conditional Jump

1. The unconditional jump is a jump in which control is transferred unconditionally to the target location.

a. LJMP (long jump). This is a 3-byte instruction. The first byte is the op-code and the second and third bytes represent the 16-bit target address which is any memory location from 0000 to FFFFH

eg: LJMP 3000H

b. AJMP: this causes the unconditional branch to the indicated address, by loading the 11-bit address to 0 -10 bits of the program counter. The destination must be therefore within the same 2K blocks.

c. SJMP (short jump). This is a 2-byte instruction. The first byte is the op-code and the second byte is the relative target address, 00 to FFH (forward +127 and backward -128 bytes from the current PC value). To calculate the target address of a short jump, the second byte is added to the PC value which is the address of the instruction immediately below the jump.

2. Conditional Jump instructions.

JBC Jump if bit = 1 and clear bit

JNB Jump if bit = 0

JB Jump if bit = 1

JNC Jump if CY = 0

JC Jump if CY = 1

CJNE reg,#data Jump if byte ≠ #data

CJNE A, byte Jump if A ≠ byte

DJNZ Decrement and Jump if A ≠ 0

JNZ Jump if A ≠ 0

JZ Jump if A = 0

All conditional jumps are short jumps.

Bit-level jump instructions: Bit-level JUMP instructions will check the conditions of the bit and if the condition is true, it jumps to the address specified in the instruction. All the bit jumps are relative.

JB bit, rel; jump if the direct bit is set to the relative address specified.

JNB bit, rel; jump if the direct bit is clear to the relative address specified.

JBC bit, rel; jump if the direct bit is set to the relative address specified and then clear the bit.

Assembly Language:

MOV 24H,10H; copy item from 10H to 24H

CPL 24.2; complement bit b2

MOVC,24.5; Copy b5 to C

MOV 24.4, C; Move C to b4

MOVC 24.0; Make copy of b0 to C

ORLC,/1; OR C and complement of b1

SETB24.6; Set bit b6

CLR 24.3; Reset bit b3

MOV 30H,24H; Store the result at 30H

HALT: SJMP HALT

WAP to calculate the 500us time delay.

MOV TMOD, #10H //select the timer mode by the registers//

MOV TH1, #0FEH // store the delay time in higher bit//

MOV TL1, #32H // store the delay time in low bit//

JNB TF1, $ //decrement the value of the timer till it is zero//

CLR TF1 //clear the timer flag bit//

CLR TR1 //OFF the timer//

Key Takeaways:

There are two kinds of branch instructions:

Unconditional jump instructions: upon their execution, a jump to a new location from where the program continues execution is executed.

Conditional jump instructions: a jump to a new program location is executed only if a specified condition is met. Otherwise, the program normally proceeds with the next instruction.

Various methods of accessing the data are called addressing modes.

8051 addressing modes are classified as follows.

Immediate addressing:

In this addressing mode, the data is provided as a part of the instruction itself.

That is the data immediately follows the instruction.

Eg. MOV A,#30H ;

ADD A, #83 ;

Here # Symbol indicates that data is immediate.

Register addressing.

In this addressing mode, the register will hold the data.

One of the eight general registers (R0 to R7) is used and specified as the operand.

Eg. MOV A, R0 ;

ADD A, R6

R0 – R7 will be selected from the current selection of the registered bank. The default register bank will be bank 0.

Direct addressing

There are two ways to access the internal memory that is by using the direct address and indirect address.

In the direct addressing mode, we not only address the internal memory but SFRs also.

In direct addressing, an 8-bit internal data memory address is specified as part of the instruction and hence, it can specify the address only in the range of 00H to FFH.

In this addressing mode, data is obtained directly from the memory.

Eg. MOV A,60h

ADD A,30h

Indirect addressing

The indirect addressing mode uses a register to hold the actual address that is used in data movement.

Registers R0 and R1 and DPTR are the only registers that can be used as data pointers.

Indirect addressing cannot be used to refer to SFR registers.

Both R0 and R1 can hold an 8-bit address and DPTR can hold a 16-bit address.

Eg. MOV A,@R0

ADD A,@R1

MOVX A,@DPTR

Indexed addressing

In indexed addressing, either the program counter (PC), or the data pointer (DTPR)—is used to hold the base address, and A is used to hold the offset address.

Adding the value of the base address to the value of the offset address forms the effective address.

Effective address = Base address + value of offset address.

Indexed addressing is used with JMP or MOVC instructions.

Lookup tables are easily implemented with the help of index addressing.

Eg. MOVC A, @A+DPTR // copies the contents of memory location pointed by the sum of the accumulator A and the DPTR into accumulator A.

MOVC A, @A+PC // copies the contents of memory location pointed by the sum of the accumulator A and the program counter into accumulator A.

Relative Addressing

Relative addressing is used only with conditional jump instructions. The relative address, (offset), is an 8 bit signed number, which is automatically added to the PC to make the address of the next instruction.

The 8 bit signed offset value gives an address range of +127 to —128 locations.

The jump destination is usually specified using a label and the assembler calculates the jump offset accordingly.

The advantage of relative addressing is that the program code is easy to relocate and the address is relative to the position in the memory.

Eg. SJMP LOOP1 JC BACK

Absolute addressing

Absolute addressing is used only by the AJMP (Absolute Jump) and ACALL (Absolute Call) instructions.

These are 2 bytes instructions.

The absolute addressing mode specifies the lowest 11 bits of the memory address as part of the instruction.

The upper 5 bits of the destination address are the upper 5 bits of the current program counter. Hence, absolute addressing allows branching only within the current 2 Kbyte page of the program memory.

Eg. AJMP LOOP1 ACALL LOOP2

Long Addressing

The long addressing mode is used with the instructions LJMP and LCALL. These are 3-byte instructions. The address specifies a full 16-bit destination address so that a jump or a call can be made to a location within a 64 Kbyte code memory space.

Eg. LJMP FINISH LCALL DELAY

Bit Inherent Addressing

In this addressing, the address of the flag which contains the operand is implied in the opcode of the instruction. Eg. CLR C; Clears the carry flag to 0

Bit Direct Addressing

In this addressing mode, the direct address of the bit is specified in the instruction. The RAM space 20H to 2FH and most of the special function registers are a bit addressable. Bit address values are between 00H to 7FH.

Eg. CLR 07h; Clears the bit 7 of 20h RAM space

SETB 07H; Sets the bit 7 of 20H RAM space.

Program:

Write a program to count the number of and o's of 8-bit data stored in location 6000H.

ORG 00008; Set program counter 00008

MOV DPTR, #6000h ; Copy address 6000H to DPTR

MOVX A, @DPTR; C o p y n u m b e r t o A

MOV R0,#08 ; C o py 0 8 i n R O

MOV R2,#00 ; C o p y 0 0 i n R 2

MOV R3,#00 ; C o p y 0 0 i n R 3

CLR C; Clear carry flag

BACK: RLC A; R o t a t e A t h r o u g h c a r r y f l a g

JC NEXT; I f C F = 1, b r a n c h t o n e x t

INC R2; I f C F = 0, i n c r e m e n t

R 2: AJMP NEXT2

NEXT: INC R3; I f C F = 1, i n c r e m e n t R 3

NEXT2: DJNZ RO,BACK ; R e p e a t u n t i l R O i s z e r o

END

Write a program to find the cube of an 8-bit number program is as follows

ORG 0000H

MOV R1,#N

MOV A, R1

MOV B, R1

MUL AB //SQUARE IS COMPUTED

MOV R2, B

MOV B, R1

MUL AB

MOV 50,A

MOV 51,B

MOV A, R2

MOV B, R1

MUL AB

ADD A, 51H

MOV 51H, A

MOV 52H, B

MOV A, # 00H ADDC A, 52H

MOV 52H, A //CUBE IS STORED IN 52H,51H,50H

END

Ten 8 bit numbers are stored in internal data memory from location 5oH. Write a program to increment the data. Assume that ten 8 bit numbers are stored in internal data memory from location 50H, hence R0 or R1 must be used as a pointer. The program is as follows.

OPT 0000H

MOV R0,#50H

MOV R3,#0AH

Loopl: INC @R0

INC RO DJNZ R3, loopl

END

END

Key Takeaways:

There are 5 different ways to execute this instruction and hence we say therefore we use addressing modes for 8051.

References:

1. The 8051 Microcontroller and Embedded Systems using Assembly and C by Muhammad Ali Mazidi.

2. The 8051 Microcontroller by I. Scott Mackenzie, Raphael C.W Phan

8051 Microcontrollers: Internals, Instructions, Programming, and Interfacing Book by Subrata Ghoshal

3. 8051 Microcontroller Based Embedded Systems Textbook by MANISH K PATEL

4. 8051 Microcontrollers: An Applications Based Introduction Book by David Calcutt, Frederick Cowan, and G. Hassan

5. Advanced PIC Microcontroller Projects in C Book by Dogan Ibrahim