VLSI

UNIT - 1VHDL MODELING 1.1 Data ObjectA data object holds a value of a specified type, created by using object declaration. Every data object belongs to one of the following three classes. An object declaration is used to declare an object, its type, and its class, and optionally assign it a value. 1.2 Data TypesThere are four types of data objects in VHDL:signals variables constants files SignalThe signal represents interconnection wires between ports it may be declared in the declaration part ofpackages entities architectures blocks The signal declaration issignal signal_name : signal_type;Signal assignment: <= VariableThe variable locally stores temporary data and it is used only inside a sequential statement that meansprocess function procedures The variable is visible only inside processes and subprograms in which it is declared. The variable declaration is

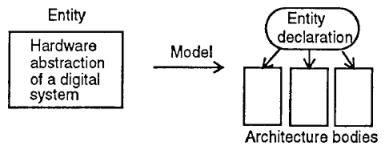

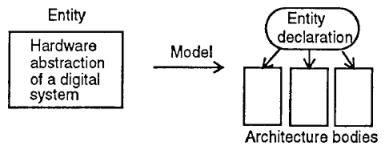

variable variable_name : variable_type;Variable assignment: := ConstantThe constant names specific values to make the model better documented and easy to update.The constant can be declared in all the declarative VHDL statement,sequential concurrent that means it may be declared in the declaration section of packages, entities, architectures, processes, subprograms and blocksThe constant declaration isconstant constant_name : constant_type := value; FileThe File type is used to access File on disk.It is used only in test bench; in fact File type cannot be implemented in hardware.In order to use the FILE type you shall include the TextIO package that contains all procedures and functions that allow you to read from and write to formatted text files.Input ASCII files are handled as file of lines, where a line is a string, terminated by a carriage return.TextIO package declares a type line used to holda line read from an input file a line to write to an output file process_write_file : process(...) file file_name_write : text; -- declare filevariable row : line; -- line to access filevariable integer_value : integer; -- integer value write to file begin -- open file write modefile_open(file_name_read, “file_to_write.txt”, write_mode); -- read line from file and then read integer value writeline(file_name_write,row); write(row,integer_value);... end process process_write_file; 1.3 Entity It is the beginning of the building block of a VHDL design. Each design has only one entity block which describes the interfacing .The syntax for an entity declaration is given as: entity entity_name isport (signal_name,signal_name : mode type;signal_name,signal_name : mode type); end entity_name;  Fig.: Entity and its model (ref 4)

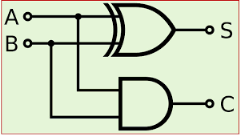

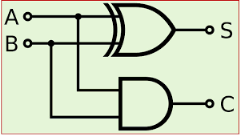

Fig.: Entity and its model (ref 4) It starts with word entity followed by the entity_name. Names and identifiers contain letters, numbers, and under score character, but must always begin with an alphabetic character. Next word is ‘is’ and then the port declarations is done. A single PORT declaration is used to declare the interfacing signals and to assign MODE and data TYPE to them. If more than one signal of the same type is used then each identifier name is separated by a comma. Identifiers are followed by a colon (:). In general, there are five modes out of them only three are frequently used. These three are in, out, and inout. Signal declarations of different mode or type are separated by semicolons (;). The last signal declaration in a port statement are terminated by a semicolon but on the outside the closing parenthesis. The entity declaration is completed by further using an end operator followed by entity name. Here is an example of an entity declaration for a half adder  Fig.: Half adder (ref 4) entity hf isport (A,B : in std_logic; Sum, Carry : out std_logic); end hf; 1.4 Architecture & Types of Modelling

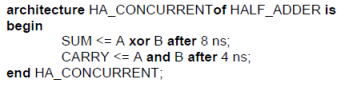

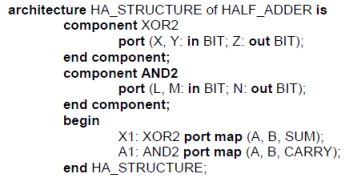

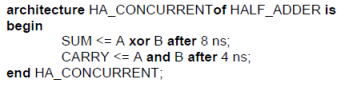

Fig.: Half adder (ref 4) entity hf isport (A,B : in std_logic; Sum, Carry : out std_logic); end hf; 1.4 Architecture & Types of ModellingIt defines how the entity operates. This may be described with the help of modeling styles. STRUCTURAL, DATA FLOW or BEHAVIORAL formats. The BEHAVIORAL or DATAFLOW approach describes the actual logic behavior of the circuit. This is generally in the form of a Boolean expression or process. The STRUCTURAL approach defines how the entity is structured i.e.by what logic devices the circuit or design is made.  The general syntax for the architecture block is:

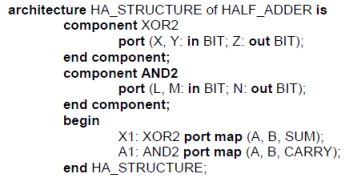

The general syntax for the architecture block is:For example: the VHDL code for half adder is given below:

variable variable_name : variable_type;Variable assignment: := ConstantThe constant names specific values to make the model better documented and easy to update.The constant can be declared in all the declarative VHDL statement,

Fig.: Entity and its model (ref 4)

Fig.: Entity and its model (ref 4)  Fig.: Half adder (ref 4) entity hf isport (A,B : in std_logic; Sum, Carry : out std_logic); end hf; 1.4 Architecture & Types of Modelling

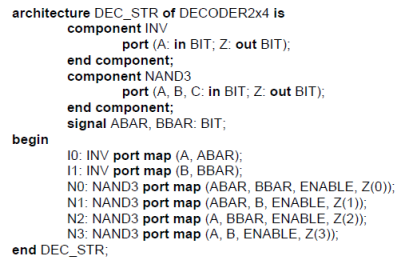

Fig.: Half adder (ref 4) entity hf isport (A,B : in std_logic; Sum, Carry : out std_logic); end hf; 1.4 Architecture & Types of Modellinglibrary ieee;use ieee.std_logic_1164.all;-- entity blockentity hf isport (A,B : in std_logic; Sum, Carry : out std_logic); end hf;-- architecture block architecture hf1 of hf is begin-- assignment statements{ Sum<= a xor b;Carry <= a and b; }end hf1; Types of modelling There are 3 types of modeling styles:Dataflow Behavioral Structural Structural Modeling In this an entity is described as a set of interconnected components . Such a model is described with the help of code:  A structural representation of 2X4 decoder is given by:

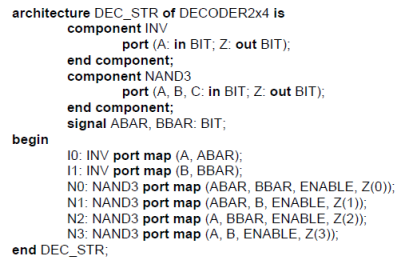

A structural representation of 2X4 decoder is given by:  DataFlow Modeling Here, the flow of data through the entity is expressed using concurrent signal assignments. The structure of the entity is not specified. Such a model is described with the help of code:

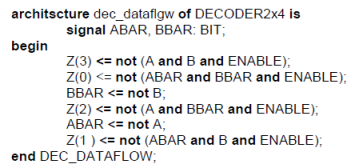

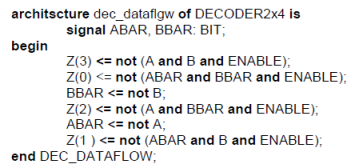

DataFlow Modeling Here, the flow of data through the entity is expressed using concurrent signal assignments. The structure of the entity is not specified. Such a model is described with the help of code:  A dataflow representation of 2X4 decoder is given by:

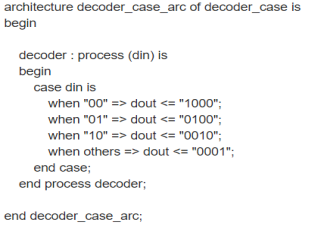

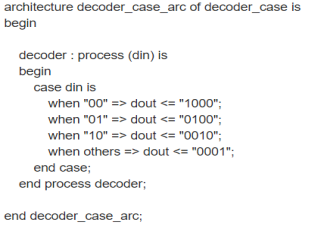

A dataflow representation of 2X4 decoder is given by:  Behavioral Modeling It specifies the behavior of the entity as a set of statements that are executed sequentially in a particular manner. These statements are specified under a process statement. A process statement can appear inside an architecture body only.

Behavioral Modeling It specifies the behavior of the entity as a set of statements that are executed sequentially in a particular manner. These statements are specified under a process statement. A process statement can appear inside an architecture body only.  1.5 Sequential Statements Several statements are used in a process. These are called sequential statements as they are executed in a sequential manner. They appear in the design from the top of the process body to the bottom. Sequential Statements• wait statement• assertion statement• report statement• signal assignment statement• variable assignment statement• procedure call statement• if statement• case statement• loop statement• next statement• exit statement• return statement• null statement wait statement It is used to wait. Explained with an example underneath.SYNTAX:[ label: ] wait [ sensitivity clause ] [ condition clause ] ; For Example:wait for 10 ns;-- timeout clause, specific time delay.

1.5 Sequential Statements Several statements are used in a process. These are called sequential statements as they are executed in a sequential manner. They appear in the design from the top of the process body to the bottom. Sequential Statements• wait statement• assertion statement• report statement• signal assignment statement• variable assignment statement• procedure call statement• if statement• case statement• loop statement• next statement• exit statement• return statement• null statement wait statement It is used to wait. Explained with an example underneath.SYNTAX:[ label: ] wait [ sensitivity clause ] [ condition clause ] ; For Example:wait for 10 ns;-- timeout clause, specific time delay.

A structural representation of 2X4 decoder is given by:

A structural representation of 2X4 decoder is given by:  DataFlow Modeling Here, the flow of data through the entity is expressed using concurrent signal assignments. The structure of the entity is not specified. Such a model is described with the help of code:

DataFlow Modeling Here, the flow of data through the entity is expressed using concurrent signal assignments. The structure of the entity is not specified. Such a model is described with the help of code:  A dataflow representation of 2X4 decoder is given by:

A dataflow representation of 2X4 decoder is given by:  Behavioral Modeling It specifies the behavior of the entity as a set of statements that are executed sequentially in a particular manner. These statements are specified under a process statement. A process statement can appear inside an architecture body only.

Behavioral Modeling It specifies the behavior of the entity as a set of statements that are executed sequentially in a particular manner. These statements are specified under a process statement. A process statement can appear inside an architecture body only.  1.5 Sequential Statements Several statements are used in a process. These are called sequential statements as they are executed in a sequential manner. They appear in the design from the top of the process body to the bottom. Sequential Statements• wait statement• assertion statement• report statement• signal assignment statement• variable assignment statement• procedure call statement• if statement• case statement• loop statement• next statement• exit statement• return statement• null statement wait statement It is used to wait. Explained with an example underneath.SYNTAX:[ label: ] wait [ sensitivity clause ] [ condition clause ] ; For Example:wait for 10 ns;-- timeout clause, specific time delay.

1.5 Sequential Statements Several statements are used in a process. These are called sequential statements as they are executed in a sequential manner. They appear in the design from the top of the process body to the bottom. Sequential Statements• wait statement• assertion statement• report statement• signal assignment statement• variable assignment statement• procedure call statement• if statement• case statement• loop statement• next statement• exit statement• return statement• null statement wait statement It is used to wait. Explained with an example underneath.SYNTAX:[ label: ] wait [ sensitivity clause ] [ condition clause ] ; For Example:wait for 10 ns;-- timeout clause, specific time delay. Program for D flip-flop: entity FF isport (D, CLK : in bit;Q: out bit);end FF;architecture BEH_1 of FF is beginprocessbeginwait on CLK;if (CLK = '1') thenQ<=D;end if;end process; end BEH_1; assertion statement It is used for internal consistency check or error message generation. SYNTAX:[ label: ] assert boolean_condition [ report string ] [ severity name ] ; For Example:assert a=(b or c); Predefined severity names are: NOTE, WARNING, ERROR, FAILURE . Default severity for assert is ERROR. Report statement It is used for output messages.SYNTAX:[ label: ] report string [ severity name ] ;

end BEH_1; assertion statement It is used for internal consistency check or error message generation. SYNTAX:[ label: ] assert boolean_condition [ report string ] [ severity name ] ; For Example:assert a=(b or c); Predefined severity names are: NOTE, WARNING, ERROR, FAILURE . Default severity for assert is ERROR. Report statement It is used for output messages.SYNTAX:[ label: ] report string [ severity name ] ;

For Example:report "finished pass1"; signal assignment statementIt is a concurrent statement rather than a sequential statement. It can be used as a sequential statement but has the side effect of obeying the general rules for when the target is actually updated. It cannot be declared within a process but can be declared is some other appropriate scope. SYNTAX: [ label: ] target <= [ delay_mechanism ] waveform ; For Example: delay_mechanism transport reject time_expression inertialwaveformwaveform_element [, waveform_element]unaffected Variable assignment statement

delay_mechanism transport reject time_expression inertialwaveformwaveform_element [, waveform_element]unaffected Variable assignment statementIt can be defined in a process and are accessible within this process. Variables and signals show a fundamental behavior. Value assignments to variables are carried out on an immediate basis. Difference between a signal and a variable assignment is : ' <= ' indicates a signal assignment and ' := ' indicates a variable assignment. SYNTAX:[ label: ] target := expression ; For Example:architecture RTL of XYZ is signal A, B, C : integer range 0 to 7;signal Y, Z : integer range 0 to 15; begin process (A, B, C)variable M, N : integer range 0 to 7; beginM:=A;N:=B;Z<=M+N; M:=C;Y<=M+N;end process; end RTL; Procedure call statement

process (A, B, C)variable M, N : integer range 0 to 7; beginM:=A;N:=B;Z<=M+N; M:=C;Y<=M+N;end process; end RTL; Procedure call statementCall a procedure. SYNTAX:[ label: ] procedure-name [ ( actual parameters ) ] ; For Example:do_it; -- no actual parameterscompute(stuff, A=>a, B=>c+d); -- positional association first,--

then named association of -- formal parameters to actual parameters if statementThe if condition evaluates ('true' or 'false'). After the first if condition, n number of elsif conditions may follow. An else is inserted in the last. The if statement is terminated with 'end if'. The first if condition has top priority: if this is fulfilled then corresponding statements will be carried out . SYNTAX:if CONDITION then-- sequential statements end if; if CONDITION then-- sequential statementselse-- sequential statements end if; For Example:entity IF_STATEMENT is port (A, B, C, X : in bit_vector (3 downto 0); Z : out bit_vector (3 downto 0); end IF_STATEMENT;

if CONDITION then-- sequential statementselse-- sequential statements end if; For Example:entity IF_STATEMENT is port (A, B, C, X : in bit_vector (3 downto 0); Z : out bit_vector (3 downto 0); end IF_STATEMENT;

architecture EXAMPLE1 of IF_STATEMENT is beginprocess (A, B, C, X)beginZ<=A; if (X = "1111") thenZ<=B;elsif (X > "1000") thenZ<=C; end if;end process; end EXAMPLE1 case statementSYNTAX:case EXPRESSION iswhen VALUE_1 =>-- sequential statementswhen VALUE_2 | VALUE_3 =>- sequential statementswhen VALUE_4 to VALUE_N =>

-- sequential statementswhen others =>-- sequential statementsend case ; For Example:entity CASE_STATEMENT isport (A, B, C, X : in integer range 0 to 15;Z : out integer range 0 to 15;end CASE_STATEMENT;architecture EXAMPLE of CASE_STATEMENT is beginprocess (A, B, C, X)begincase X iswhen 0 =>Z<=A;when 7 | 9 =>Z<=B; when 1 to 5 =>Z<=C;when others =>Z<=0;end case; end process; end EXAMPLE; loop statement

when 1 to 5 =>Z<=C;when others =>Z<=0;end case; end process; end EXAMPLE; loop statementThe loop label is optional. By defining the range the direction as well as the possible values of the loop variable are fixed. The loop variable is only accessible within the loop. For synthesis it has to be locally static and independent on signal or variable values and are not synthesizable.

Three kinds of iteration statements. SYNTAX:[ label: ] loopsequence-of-statements -- use exit statement to get out end loop [ label ] ;[ label: ] for variable in range loopsequence-of-statementsend loop [ label ] ;[ label: ] while condition loop sequence-of-statementsend loop [ label ] ;loopinput_something; exit when end_file; end loop; For Example:entity CONV_INT isport (VECTOR: in bit_vector(7 downto 0);RESULT: out integer); end CONV_INT;architecture A of CONV_INT isbeginprocess(VECTOR)variable TMP: integer;beginTMP := 0;for I in 7 downto 0 loopif (VECTOR(I)='1') thenTMP := TMP + 2**I;end if;end loop;RESULT <= TMP;

end process;end A; architecture C of CONV_INT isbeginprocess(VECTOR)variable TMP: integer;variable I: integer;beginTMP := 0;I := VECTOR’ high;while (I >= VECTOR’ low) loop if (VECTOR(I)='1') thenTMP := TMP + 2**I;end if;I:=I-1;end loop;RESULT <= TMP; end process; end C; next statement

end process; end C; next statementIt is used in a loop to cause the next iteration. SYNTAX:[ label: ] next [ label2 ] [ when condition ] ;next; For Example:next outer_loop;next when A>B;next this_loop when C=D or done; -- done is a Boolean variable exit statementIt may be used in a loop to immediately exit the loop. SYNTAX:[ label: ] exit [ label2 ] [ when condition ] ;exit; For Example:exit outer_loop;exit when A>B;

exit this_loop when C=D or done; -- done is a Boolean variable return statementIt is required in a function and its optional to use in a procedure. SYNTAX: [ label: ] return [ expression ] ; For Example:return; -- from somewhere in a procedure return a+b; -- returned value in a function null statementUsed when a statement is required. SYNTAX: [ label: ] null ; 1.6 Concurrent StatementsConcurrent Statements• block statement• generate statement block statement

[ label: ] null ; 1.6 Concurrent StatementsConcurrent Statements• block statement• generate statement block statementThe sub modules in an architecture body is known as blocks. It has its own interface that is connected to other blocks or ports. SYNTAX:block_label :block [ ( guard_expression ) ]block_headerblock_declarative_partbeginblock_statement_partend block [ block_label ] ; For Example:architecture block_structure of processor is type data_path_control is … ;signal internal_control : data_path_control;begincontrol_unit : blockport (clk : in bit; bus_control : out proc_control;bus_ready : in bit;control : out data_path_control); port map (clk => clock,bus_control => control, bus_ ready => ready; control => internal_control); declarations for control_unit beginstatements for control_unitend block control_unit;data_path : blockport (address : out integer;data : inout word_32;control : in data_path_control);port map (address => address, data => data, control => internal_control); declarations for data_pathbeginstatements for data_pathend block data_path;end block_structure; GENERATE statement

beginstatements for control_unitend block control_unit;data_path : blockport (address : out integer;data : inout word_32;control : in data_path_control);port map (address => address, data => data, control => internal_control); declarations for data_pathbeginstatements for data_pathend block data_path;end block_structure; GENERATE statementIt can be used in architecture to describe regular structures such as arrays of blocks, component instances or processes. SYNTAX:generate_statement ::= generate_label : generation_scheme generate { concurrent_statement }end generate [ generate_label ] ;generation_scheme ::= for generate_parameter_specification if condition.The for generation scheme describes structures having repeated pattern. The if generation scheme is used to handle exception cases within the structure. For Example:for i in 0 to width-1 generate ls_bit : if i = 0  generate ls_cell : half_adder port map (a(0), b(0), sum(0), c_in(1)); end generate lsbit;middle_bit : if i > 0 and i < width-1 generatemiddle_cell : full_adder port map (a(i), b(i), c_in(i), sum(i), c_in(i+1)); end generate middle_bit;ms_bit : if i = width-1 generatems_cell : full_adder port map (a(i), b(i), c_in(i), sum(i), carry);end generate ms_bit;end generate adder; 1.7 PackagesIt is a collection of functions, procedures, shared variables, constants, files, aliases, types, subtypes, attributes, and components. Components in a Package FileIt is preferable to put all of your component definitions in a single package file, rather than copy and pasting them everywhere the component is instantiated. This way, if the port map changes, only the package file and the actual instantiations need to be updated.Constants and Types in a Package FileConstants and types that appear repeatedly throughout the code should likely be grouped together in a package file.Functions and Procedures in a Package FileFunctions and procedures need to exist both in the declaration section as well as the body section. The declaration contains the prototype for the function or procedure and the body contains the actual implementation of the code. Below is an example package file that shows off some of the situations described above.-- Package Declaration Sectionpackage example_package is constant c_PIXELS : integer := 65536; type t_FROM_FIFO is record wr_full : std_logic; rd_empty : std_logic; end record t_FROM_FIFO; component example_component is port ( i_data : in std_logic; o_rsult : out std_logic); end component example_component; function Bitwise_AND ( i_vector : in std_logic_vector(3 downto 0)) return std_logic; end package example_package; -- Package Body Sectionpackage body example_package is function Bitwise_AND ( i_vector : in std_logic_vector(3 downto 0) ) return std_logic is begin return (i_vector (0) and i_vector (1) and i_vector (2) and i_vector (3)); end; end package body example_package; 1.8 Sub ProgramsSubprograms in VHDL are in the form of functions and procedures. Functions return a value and can be used in signal and variable assignment statements:e.g. A <= abs(-1); -- where abs() returns absolute value Procedures, on the other hand, do not have return values but can manipulate the signals or variables passed to them as parameters:e.g. absolute(A);absolute() here is a procedure that directly assigns A its absolute value The use of functions and procedures enables code compaction, enhances readability, and supports hierarchy by allowing code sequences that are used frequently to be defined and subsequently reused easily. 1.9 AttributeA value, function, type, range, signal, or constant that may be associated with one or more types, objects, subprograms, etc.

generate ls_cell : half_adder port map (a(0), b(0), sum(0), c_in(1)); end generate lsbit;middle_bit : if i > 0 and i < width-1 generatemiddle_cell : full_adder port map (a(i), b(i), c_in(i), sum(i), c_in(i+1)); end generate middle_bit;ms_bit : if i = width-1 generatems_cell : full_adder port map (a(i), b(i), c_in(i), sum(i), carry);end generate ms_bit;end generate adder; 1.7 PackagesIt is a collection of functions, procedures, shared variables, constants, files, aliases, types, subtypes, attributes, and components. Components in a Package FileIt is preferable to put all of your component definitions in a single package file, rather than copy and pasting them everywhere the component is instantiated. This way, if the port map changes, only the package file and the actual instantiations need to be updated.Constants and Types in a Package FileConstants and types that appear repeatedly throughout the code should likely be grouped together in a package file.Functions and Procedures in a Package FileFunctions and procedures need to exist both in the declaration section as well as the body section. The declaration contains the prototype for the function or procedure and the body contains the actual implementation of the code. Below is an example package file that shows off some of the situations described above.-- Package Declaration Sectionpackage example_package is constant c_PIXELS : integer := 65536; type t_FROM_FIFO is record wr_full : std_logic; rd_empty : std_logic; end record t_FROM_FIFO; component example_component is port ( i_data : in std_logic; o_rsult : out std_logic); end component example_component; function Bitwise_AND ( i_vector : in std_logic_vector(3 downto 0)) return std_logic; end package example_package; -- Package Body Sectionpackage body example_package is function Bitwise_AND ( i_vector : in std_logic_vector(3 downto 0) ) return std_logic is begin return (i_vector (0) and i_vector (1) and i_vector (2) and i_vector (3)); end; end package body example_package; 1.8 Sub ProgramsSubprograms in VHDL are in the form of functions and procedures. Functions return a value and can be used in signal and variable assignment statements:e.g. A <= abs(-1); -- where abs() returns absolute value Procedures, on the other hand, do not have return values but can manipulate the signals or variables passed to them as parameters:e.g. absolute(A);absolute() here is a procedure that directly assigns A its absolute value The use of functions and procedures enables code compaction, enhances readability, and supports hierarchy by allowing code sequences that are used frequently to be defined and subsequently reused easily. 1.9 AttributeA value, function, type, range, signal, or constant that may be associated with one or more types, objects, subprograms, etc.

0 matching results found

Browse by Topics