UNIT- 1

Basic Real Time Concepts & Hardware Consideration

Overview:

- A key characteristic of a RTOS is the level of its consistency concerning the amount of time it takes to accept and complete an application's task; the variability is 'jitter'.

- A 'hard' real-time operating system (Hard RTOS) has less jitter than a 'soft' real-time operating system (Soft RTOS).

- The late answer is a wrong answer in a hard RTOS while a late answer is acceptable in a soft RTOS.

- The chief design goal is not high throughput, but rather a guarantee of a soft or hard performance category.

- An RTOS that can usually or generally meet a deadline is a soft real-time OS, but if it can meet a deadline deterministically it is a hard real-time OS.

- The hardware of a computer solves problems by repeated execution of machine - language instructions, collectively known as software.

- Software, on the other hand, is traditionally divided into system programs and Application Programs.

- System:

A system is a mapping of a set of inputs into a set of outputs. - Response Time:

The time between the presentation of a set of inputs to a system and the

realization of the required behaviour, including the availability of all associated outputs, is called the response time of the system. - Real - Time System ( I ):

A real - time system is a computer system that must satisfy bounded response -time constraints or risk severe consequences, including failure. - Real - Time System ( II ):

A real - time system is one whose logical correctness is based on both the

correctness of the outputs and their timeliness. - Failed System:

A failed system is a system that cannot satisfy one or more of the requirements stipulated in the system requirements specification. - Embedded System:

An embedded system is a system containing one or more computers (or

processors) having a central role in the functionality of the system, but the

system is not explicitly called a computer. - Soft Real - Time System:

A soft real - time system is one in which performance is degraded but not

destroyed by failure to meet response - time constraints. - Hard Real - Time System:

A hard real - time system is one in which failure to meet even a single deadline may lead to complete or catastrophic system failure. - Firm Real - Time System:

A firm real - time system is one in which a few missed deadlines will not lead

to total failure, but missing more than a few may lead to complete or catastrophic system failure.

A Sampling of Hard, Firm, and Soft Real - Time Systems:

System | Real Time Classification | Explanation |

Avionics weapons delivery | Hard | Missing the deadline to launch the |

Navigation controller for | Firm | Missing a few navigation deadlines |

Console hockey game | Soft | Missing even several deadlines will |

- Real - Time Punctuality:

Real - time punctuality means that every response time has an average value ,tR, with upper and lower bounds of tR + εU and tR - εL, respectively, and εU,εL → 0+. - Event:

Any occurrence that causes the program counter to change non sequentially is considered a change of flow - of - control, and thus an event. - Release Time:

The release time is the time at which an instance of a scheduled task is

ready to run, and is generally associated with an interrupt. Events that do not occur at regular periods are called aperiodic. Furthermore,

aperiodic events that tend to occur very infrequently are called sporadic.

| Periodic | Aperiodic | Sporadic |

Synchronous | Cyclic Code | Conditional Branch | Divide-by-Zero (trap) Interrupt |

Asynchronous | Clock Interrupt | Regular, But Not Fixed-Period Interrupt | Power Loss Alarm |

Taxonomy of Events and Some Typical Examples:

- Deterministic System:

A system is deterministic, if for each possible state and each set of inputs,

a unique set of outputs and next state of the system can be determined.

- CPU Utilization Factor:

The CPU utilization or time - loading factor, U, is a relative measure of the

no idle processing taking place.

Utilization (%) | Zone Type | Typical Application |

<26 | Unnecessarily Safe | Various |

26-50 | Very Safe | Various |

51-68 | Safe | Various |

69 | Theoretical Limit | Embedded Systems |

70-82 | Questionable | Embedded Systems |

83-99 | Dangerous | Embedded Systems |

100 | Critical | Marginally Stressed Systems |

>100 | Overloaded | Stressed Systems |

Key Takeaways:

- System: A system is a mapping of a set of inputs into a set of outputs.

- Real - Time System (I): A real - time system is a computer system that must satisfy bounded response -time constraints or risk severe consequences, including failure.

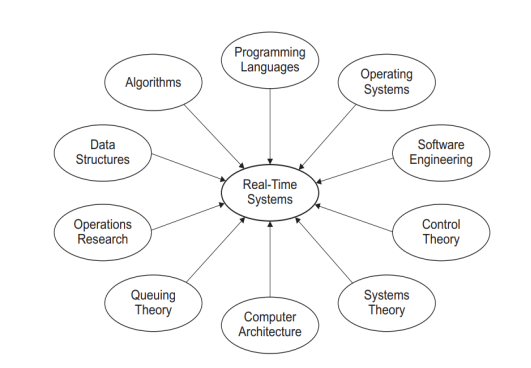

Fig.1: A variety of disciplines that affect real - time systems engineering |

The design and implementation of real - time systems requires attention to

numerous practical issues. These include:

- The selection of hardware and system software, and evaluation of the

trade - off needed for a competitive solution, including dealing with

distributed computing systems and the issues of concurrency and

synchronization. - Specification and design of real - time systems, as well as correct and inclusive representation of temporal behaviour.

- Understanding the nuances of the high - level programming language(s)

and the real - time implications resulting from their optimized compilation

into machine - language code. - Optimizing (with application - specific objectives) of system fault tolerance

and reliability through careful design and analysis. - The design and administration of adequate tests at different levels of

hierarchy, and the selection of appropriate development tools and test

equipment. - Taking advantage of open systems technology and interoperability.

An open system is an extensible collection of independently written applications that cooperate to function as an integrated system.

- For example, several versions of the open operating system, Linux, have emerged for use in various real - time applications (Abbott, 2006 ). Interoperability can be measured in terms of compliance with open system standards, such as the real - time CORBA ( common object request broker architecture ) standard (Fay - Wolfe et al., 2000 ).

- Finally, estimating and measuring response times and (if needed) reducing them. Performing a schedulability analysis, that is, determining and guaranteeing deadline satisfaction, a priori.

Key Takeaways:

- An open system is an extensible collection of independently written applications that cooperate to function as an integrated system.

- Estimating and measuring response times and (if needed) reducing them.

Domain | Applications |

Aerospace |

|

Civilian |

|

Industrial |

|

Medical |

|

Multimedia |

|

- Any application that monitors static or dynamic behaviour of system continuously with respect to time is real time system.

- Traffic control systems or Process control based applications in industries are its appropriate examples.

Key Takeaways:

- Real Time Systems Are Used in Medical Domain for Remote Surgeries and Magnetic Resonance Imaging.

- Real Time Systems Are Used in Multimedia Domain in Home Theatres and Simulators.

Year | Landmark | Developer | Development | Innovations |

1947 | Whirlwind | IBM | Flight Simulator | Ferrite Core Memory(“Fast”)High Level Language |

1957 | SAGE | IBM | Air Defense | Designed for Real Time |

1958 | Scientific 1103A | Univac | General Purpose | Asynchronous Interrupt |

1959 | SABRE | IBM | Airline Reservation | Hub-Go-Ahead Policy |

1962 | Basic Executive | IBM | General Purpose | Diverse Real Time Scheduling |

1963 | Basic Executive-II | IBM | General Purpose | Disk -resident system/User Programs |

1970s | RSX,RTE | DEC,HP | Real-time operating systems | Hosted By Mini-Computers |

1973 | Rate-Monotonic System | Liu & Leyland | Fundamental Theory | Upper bound on utilisation for schedulable systems |

1970s & 1980s | RMX-80,MROS 68K,VRTS,etc. | Various | Real-Time operating systems | Hosted by microprocessors |

1983 | Ada 83 | U.S. DoD | Programming Language | For mission-critical embedded systems |

1995 | Ada 95 | Community | Programming Language | Improved version of Ada 83 |

2000s | - | - | Various Advances in hardware,open-source,and commercial system software & tools | A continuously growing range of innovative applications that can be Real-Time |

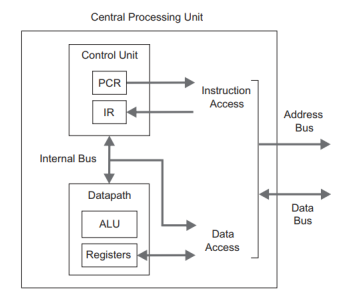

Fig.2: Internal structure of a simplified CPU. The Instruction Access and Data |

- The CPU is the core unit where instruction processing takes place; it consists of a control unit, an internal bus, and a data path, as illustrated in Above Figure.

- The data path contains a multi - function arithmetic - logic unit

(ALU), and a bank of work registers, as well as a status register. - The control unit interfaces to the system bus through a program counter register (PCR) that addresses the external memory location from which the next instruction is going to be fetched to an instruction register ( IR ).

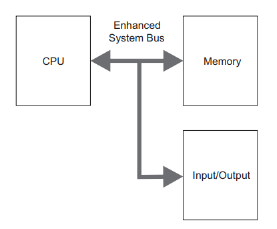

1.5.1 Von-Newman Architecture:

- The traditional von Neumann computer architecture, also known as the

Princeton architecture, is used in numerous commercial processors and can be depicted with only three elements: a central processing unit ( CPU), a system bus, and memory.

Fig.3. Von Neumann architecture with slightly enhanced system bus for programmed input/output. |

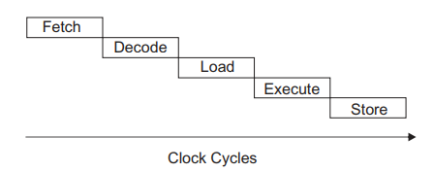

1.5.2 Instruction Processing:

- Instruction processing consists of multiple consecutive phases taking a varying number of clock cycles to complete. These independent phases form jointly an instruction cycle.

- Every instruction is represented by its unique binary code that is stored in the memory, and a stream of such codes forms a machine - language program

Fig.4.Phases of Instruction Processing vs. Clock Cycles |

Key Takeaways:

- The CPU is the core unit where instruction processing takes place; it consists of a control unit, an internal bus, and a data path

- The data path contains a multi - function arithmetic - logic unit (ALU), and a bank of work registers, as well as a status register.

- The fundamental practices for input and output handling are still the same as in the late seventies:

• Polled I/O

• Interrupt - driven I/O

• Direct memory access

- Polled I/O:

In a polled I/O system, the status of the I/O device is checked periodically, or, at least, regularly. Therefore, such I/O activity is software controlled; only accessible status and data registers are needed in the hardware side.

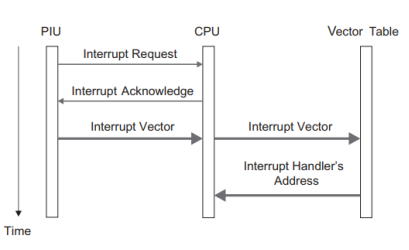

- Interrupt - driven I/O:

Interrupt - driven I/O processing has remarkable advantages over the straightforward polled I/O: the service latency can, in general, be reduced and made less uncertain without increasing the loading of the CPU.

Fig.5: Interrupt - identification procedure between the CPU and PIU using vectored interrupt. |

Analog and Digital Input/Output:

- The core categories are outlined below:

- Analog

- Digital parallel

- Digital pulse

- Digital serial

- Digital waveform

Key Takeaways:

- The fundamental practices for input and output handling are still the same as in the late seventies:

• Polled I/O

• Interrupt - driven I/O

• Direct memory access

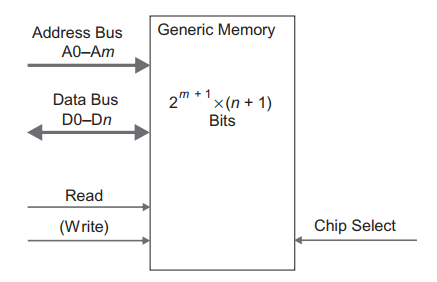

- Volatile RAM versus non-volatile ROM is the traditional distinction between the two principal groups of semiconductor memory, where RAM states for random - access memory and ROM for read - only memory.

- Electrically erasable programmable ROM (EEPROM) and its close relative Flash are based on the dynamic floating - gate principle and they both can be rewritten in a similar way as RAM devices.

- However, the erasing and writing process of those ROM - type devices is much slower than in the case of RAM.

- There are two classes of RAM devices: static RAM (SRAM) and dynamic RAM (DRAM).

- Either or both of these classes are used also in real – time systems. A single SRAM - type memory cell needs typically six transistors to implement a bistate flip - flop structure, while a DRAM cell can be implemented with a single transistor and capacitor only.

- Below is a sampled evolution path of DRAM modules with advanced access modes in their order of appearance (from the late eighties to 2007):

• Fast page mode ( FPM ) DRAM

• Extended data output ( EDO ) DRAM

• Synchronous DRAM ( SDRAM )

• Direct Rambus DRAM ( DRDRAM )

Double data rate 3 synchronous DRAM ( DDR3 SDRAM

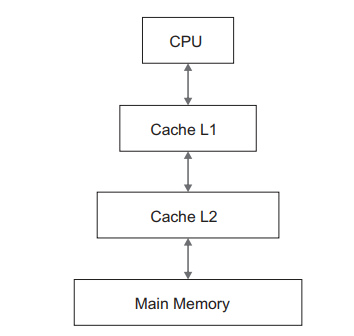

Fig.6: Hierarchical memory organization with two cache levels, L1 and L2, between the CPU and main memory.

Fig.7: Interface lines of a generic memory component |

1.7.1 Cache:

- The basic operation of the cache is as follows. Suppose the CPU requests the content of a DRAM location.

- First, the cache controller checks the address tags to see if the particular location is in the cache. If present, the data is immediately retrieved from the cache, which is significantly faster than a fetch from main memory.

- However, if the needed data is not in the cache, the cache contents must be written back and the required new block loaded from main memory to the cache.

- The needed data is then delivered from the cache to the CPU, and the address tags are updated correspondingly by the cache controller.

Key Takeaways:

- The erasing and writing process of those ROM - type devices is much slower than in the case of RAM.

- There are two classes of RAM devices: static RAM ( SRAM ) and dynamic RAM ( DRAM ).

- In DMA, access to the computer’s memory is given to other devices

in the system without any CPU intervention. - That is, data is transferred directly between main memory and some external device.

- Here, a separate DMA controller is required unless the DMA - handling circuitry is integrated into the CPU itself.

Key Takeaways:

- In DMA, access to the computer’s memory is given to other devices

in the system without any CPU intervention.

References:

- Real- Time Systems Design and Analysis.. Tools for the Practitioner by Phillip A Laplante, Seppo J.Ovaska ,Wiley - 4th Edition

- Embedded Real Time Systems: Concepts, Design and Programming - Dr. K.V.K. Prasad -Black Book, Edition: 2014

- Real Time Systems Theory and Practice , Rajib Mall , Pearson Education