Unit 3

Data Movement Instruction

3.1 PUSH and POP instruction

This is a single byte instruction where the contents of the register pair specified in the operand are copied into the stack.

The stack pointer is decremented and the contents of the higher order register in pair such as B in BC pair , D in DE pair are copied on stack.

The stack pointer is decremented again and the contents of lower order register are copied on the stack. Contents of the register pair are unchanged.

Example

PUSH D

Will push the contents of DE pair

Let D=15H and E =23 H

Let SP = 2300 H

Then after executing PUSH D we get following contents in SP and stack

SP = 22FE | STACK |

22FE | 23H |

22FF | 15H |

2300 |

|

This is a single byte instruction. On execution copies two top bytes on stack to designated register pair in operand

(1) Contents of top most location of stack called stack top are copied into lower register of the pair. SP is incremented by 1.

(2) Contents of stack location pointed by SP are copied into higher register of the pair. The stack pointer SP is incremented by 1. No flags are affected . Contents of stack are unchanged.

Example

Consider SP = 22FE H with the following contents on stack

On exceution of instruction POP H the contents of H , L , SP which is shown as

SP = 22FE | STACK |

22FE | 23H |

22FF | 15H |

2300 |

|

Before Execution

SP = 2300 | STACK |

22FE | 10H |

22FF | 24H |

2300 |

|

H = 24 H

L = 10H

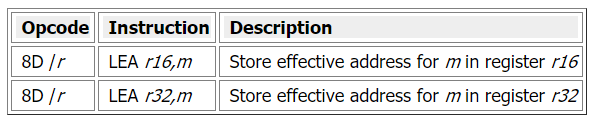

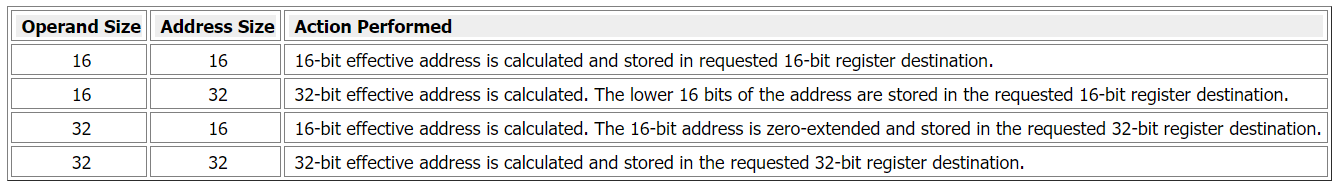

Computes the effective address of the second operand (the source operand) and stores it in the first operand (destination operand). The source operand is a memory address (offset part) specified with one of the processors addressing modes; the destination operand is a general-purpose register. The address-size and operand-size attributes affect the action performed by this instruction, as shown in the following table. The operand-size attribute of the instruction is determined by the chosen register; the address-size attribute is determined by the attribute of the code segment.

Operation

IF OperandSize 16 AND AddressSize 16

THEN

DEST EffectiveAddress(SRC); (* 16-bit address *)

ELSE IF OperandSize 16 AND AddressSize 32

THEN

temp EffectiveAddress(SRC); (* 32-bit address *)

DEST temp[0..15]; (* 16-bit address *)

ELSE IF OperandSize 32 AND AddressSize 16

THEN

temp EffectiveAddress(SRC); (* 16-bit address *)

DEST ZeroExtend(temp); (* 32-bit address *)

ELSE IF OperandSize 32 AND AddressSize 32

THEN

DEST EffectiveAddress(SRC); (* 32-bit address *)

FI;

FI;

a) Addition

b) Subtraction

c) Comparison

d) Multiplication

e) Division

Instructions to perform addition

Instructions to perform subtraction

For example :

Program to add two values.

Rval DWORD ?

Xval DWORD 26

Yval DWORD 30

Zval DWORD 40

.code

mov eax,Xval

neg eax ; EAX = -26, EAX = -Xval

mov ebx,Yval ; EBX = 30, EBX = Yval

sub ebx,Zval ; EBX = -10, EBX = (Yval – Zval)

add eax,ebx ; EAX = -36, EAX = -Xval + (Yval – Zval)

mov Rval,eax ; Rval = -36

Compare:

|

|

|

|

When the first form, CMPS des_string, src_string, is used the assembler will replace it by CMPSB, CMPSW, or CMPSD depending on the size of the operands dest_string and src_string.

The semantics of the instructions CMPSB, CMPSW, and CMPSD are illustrated below:

The CMPSB Instruction

This instruction is used to compare arrays of bytes. It compares the byte addressed by DS:[SI] to the byte addressed by ES:[DI] by performing the subtraction operation DS:[SI] - ES:[DI], setting the arithmetic flags based on the result of the subtraction.. Then, SI and DI are either incremented or decremented by 1 depending on the Direction Flag.

The CMPSW Instruction

This instruction is used to compare arrays of words. It compares the word addressed by DS:[SI] to the word addressed by ES:[DI] by performing the subtraction operation DS:[SI+1:SI] - ES:[DI+1:DI], setting the arithmetic flags based on the result of the subtraction. Then, SI and DI are either incremented or decremented by 2 depending on the Direction Flag.

The CMPSD Instruction

This instruction is used to compare arrays of double words. It compares the double word addressed by DS:[SI] to the double word addressed by ES:[DI] by performing the subtraction operation DS:[SI+3:SI] - ES:[DI+3:DI], setting the arithmetic flags based on the result of the subtraction. Then, SI and DI are either incremented or decremented by 4 depending on the Direction Flag.

Program to compare two strings

str1 db \'GLSICT\',\'$\'

strlen1 db $-str1

str2 db \'GLSICT\',\'$\'

strlen2 db $-str2

streq db \'Strings are Equal\',\'$\'

struneq db \'Strings are Unequal\',\'$\'

Data Ends

Code Segment

Assume cs:code, ds:data

Begin:

mov ax, data

mov ds, ax

mov es, ax

lea si, str1

lea di, str2

mov cx, 6

mov al, strlen1

mov bl, strlen2

cmp al, bl

jne Not_Equal

repe cmpsb

jne Not_Equal

jmp Equal

Not_Equal:

mov ah, 09h

lea dx, struneq

int 21h

jmp Exit

Equal:

mov ah, 09h

lea dx, streq

int 21h

Exit:

mov ax, 4c00h

int 21h

Code Ends

End Begin

Multiplication and Division

Multiplication MUL (unsigned ) IMUL(signed)

MUL INSTRUCTION (UNSIGNED MULTIPLY) Multiplies an 8-, 16-, or 32-bit operand by either AL, AX

Syntax:MUL AL R/M8

Syntax: MUL AX R/M16

MUL INSTRUCTION

The product is stored in a register (or group of registers) twice the size of the operands.

The operand can be a register or a memory operand

MUL INSTRUCTION

EXAMPLES

Mov al, 5h ; AX = 0050h, CF = 0

Mov bl, 10h

Mul bl ;

IMUL INSTRUCTION (SIGNED MULTIPLY)

It uses the same operands as the MUL instruction and preserves the sign of the product.

IMUL INSTRUCTION

Suppose AX contains 1 and BX contains FFFFh

Mov AX, 1h

Mov BX, FFFFh I

MUL BX ; Product =FFFFFFFFh DX = FFFFh, AX=FFFFh CF/OF=0 DX is a sign

IMUL INSTRUCTION

IMUL sets the Carry and Overflow flags if the high-order product is not a sign extension of the low-order product

Mov al, 48

Mov bl, 4

Imul bl ;AX = 00C0h, OF = 1 AH is not a sign extension of AL, so the Overflow flag is set

IMUL INSTRUCTION

Suppose AX contains FFFFh and BX contains FFFFh Mov AX, FFFFH Mov BX, FFFFh IMUL BX Decimal product=1 Hex Product = 00000001 h DX = 0000h, AX=0001h CF/OF=0 DX is a sign extension of AX for this CF/OF=0

DIVIDE DIV(unsinged) IDIV(singed)

DIVIDE AND IDIVIDE When division is performed we obtain two results ,The quotient and the remainder.

Similarly like Multiplication there are separate instructions for unsigned and signed division

Syntax:

DIV divisor IDIV divisor Byte Form:

The divisor is eight- bit register or memory byte The 16 – bit dividend is assumed to be in AX. After division 8-bit quotient is in AL and 8-bit remainder in AH.

Word Form: The divisor is a 16-bit register or memory word The 32-bit dividend is assumed to be in DX:AX After division, the 16-bit quotient is in AX and 16- bit remainder is in DX Effect on flags: All status flags are undefined

Divide Overflow: It is possible that the quotient s too big to fit in the specified destination(AL or AX). This Happens Because the divisor is much smaller than the dividend. When this Happens the program terminates and system displays message “divide overflow”

EXAMPLE

Suppose DX contains 0000h , AX contains 0005h, and BX contains 0002h.

BCD and ASCII Arithmetic

Numbers are stored as a string of ASCII characters

Example: 1234 is stored as 31 32 33 34H

ASCII for 1 is 31H, for 2 is 32H, etc.

BCD representation

∗ Unpacked BCD

Example: 1234 is stored as 01 02 03 04H – Additional byte is used for sign

Sign byte: 00H for + and 80H for –

∗ Packed BCD

Saves space by packing two digits into a byte

– Example: 1234 is stored as 12 34H

There are four instructions

aaa − ASCII adjust after addition

aas − ASCII adjust after subtraction

aam − ASCII adjust after multiplication

aad − ASCII adjust before division

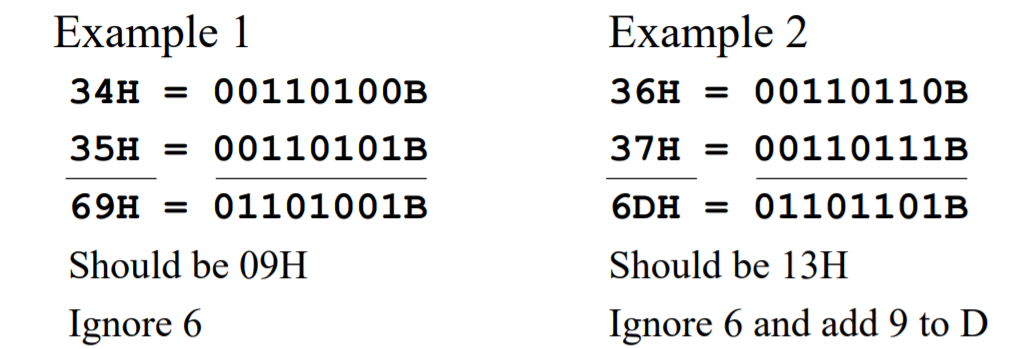

ASCII addition

The aaa instruction works as follows:

∗ If the least significant four bits in AL are > 9 or if AF =1, it adds 6 to AL and 1 to AH.

– Both CF and AF are set

∗ In all cases, the most significant four bits in AL are cleared

∗ Example: sub AH,AH ; clear AH mov AL,'6' ; AL := 36H add AL,'7' ; AL := 36H+37H = 6DH aaa ;

AX := 0103H or AL,30H ; AL := 33H

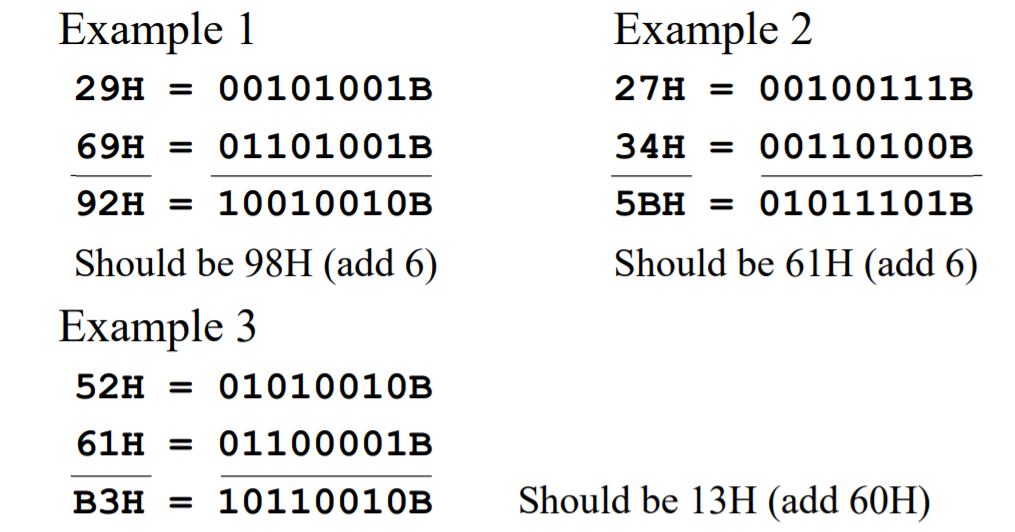

ASCII subtraction

• The aas instruction works as follows:

∗ If the least significant four bits in AL are > 9 or if AF =1, it subtracts 6 from AL and 1 from AH. – Both CF and AF are set

∗ In all cases, the most significant four bits in AL are cleared

• This adjustment is needed only if the result is negative

Example 1:

Positive result sub AH,AH ; clear AH

mov AL,'9' ; AL := 39H

sub AL,'3' ; AL := 39H-33H = 6H

aas ; AX := 0006H or AL,30H ; AL := 36H

Example 2:

Negative result sub AH,AH ; clear AH

mov AL,'3' ; AL := 33H

sub AL,'9' ; AL := 33H-39H = FAH

aas ; AX := FF04H or AL,30H ; AL := 34H

ASCII multiplication

mov AL,3 ; multiplier in unpacked BCD form

mov BL,9 ; multiplicand in unpacked BCD form

mul BL ; result 001BH is in AX

aam ; AX := 0207H or AX,3030H ; AX := 3237H

• Example 2

mov AL,'3' ; multiplier in ASCII

mov BL,'9' ; multiplicand in ASCII

and AL,0FH ; multiplier in unpacked BCD form

and BL,0FH ; multiplicand in unpacked BCD form

mul BL ; result 001BH is in AX aam ; AX := 0207H or AL,30H ; AL := 37H

ASCII Division

Example:

mov AX,0207H ; dividend in unpacked BCD form

mov BL,05H ; divisor in unpacked BCD form

aad ; AX := 001BH div BL ; AX := 0205H

Packed BCD addition

The daa instruction works as follows:

If the least significant four bits in AL are > 9 or if AF =1, it adds 6 to AL and sets AF

If the most significant four bits in AL are > 9 or if CF =1, it adds 60H to AL and sets CF

Example:

mov AL,71H

add AL,43H ; AL := B4H

daa ; AL := 14H and CF := 1

The das instruction works as follows:

∗ If the least significant four bits in AL are > 9 or if AF =1, it subtracts 6 from AL and sets AF

∗ If the most significant four bits in AL are > 9 or if CF =1, it subtracts 60H from AL and sets CF

Example:

mov AL,71H

sub AL,43H ; AL := 2EH

das ; AL := 28H

Assembler Details

References

1. Microprocessor Architecture, Programming, and Applications with the 8085 Textbook by Ramesh S. Gaonkar

2. Microprocessor Book by A.P.Godse and D.A.Godse

3. Microprocessor And Microcontroller Book by A.P.Godse