Unit 6

Pentium ProMicroprocessor

Silent features of Pentium Pro Architecture:

Dynamic Execution:

Intel Pro microprocessor can anticipate jumps in the flow of instructions.

While the program is being executed processor looks at instructions further ahead in the program and decides in which order to execute the instructions.

If the instructions can be executed independently it will execute these instructions in optimal order rather than in original program order.

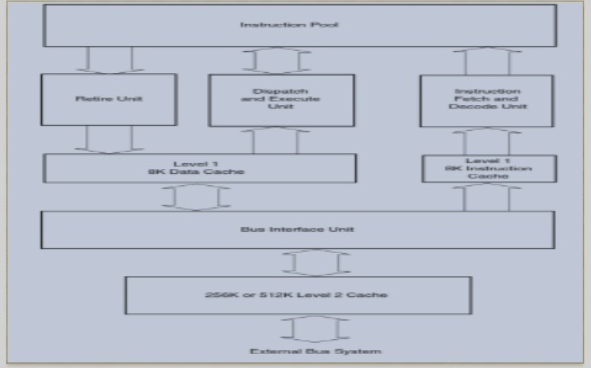

Pentium Pro Architecture:

Memory:

Pentium Pro microprocessor has 8-bit byte memory. Two consecutive bytes form a word, four consecutive bytes form a double word. All the address in the memory are of byte formats. Programmers usually view Pentium Pro (x86) memory as a collection of segments.

Register:

There are 8 general-purpose registers present in the Pentium Pro architecture. Each register is 32-bit long. First four register are used for data manipulation and next four register are used to hold address. There are some special-purpose registers in the x86 architecture such as Segment register, FLAGS register and EIP register.

Data Formats:

Instruction Formats:

The basic format for Pentium Pro Instructions is:

The Opcode is the only element that is present in every instruction. Other elements may or may not present or may be of different lengths depending on the operations of instructions.

5. Addressing Modes:

Pentium Pro Architecture has large number of Addressing modes. Operands value is specified either by using Immediate mode or by using register mode. Operands stored in memory are specified using variation of the Target address (TA) calculation:

TA = (base register) + (index register) * (scale factor) + displacement

Instruction Set:

Pentium Pro Architecture has a large and complex instruction set having more than 400 different machine instructions. An instruction may have zero, one, two, or three operands.

There are Register-to-Register instructions, Register-to-Memory instructions and Memory-to-Memory instructions.

In Pentium Pro Architecture there are some special-purpose registers to perform operations required in the high-level programming languages.

Input and Output:

Input instruction transfer one byte, word or doubleword at a time from an I/O port into register EAX. Output instructions transfer one byte, word or doubleword from EAX to an I/O port. Entire string can be transferred using single operation.

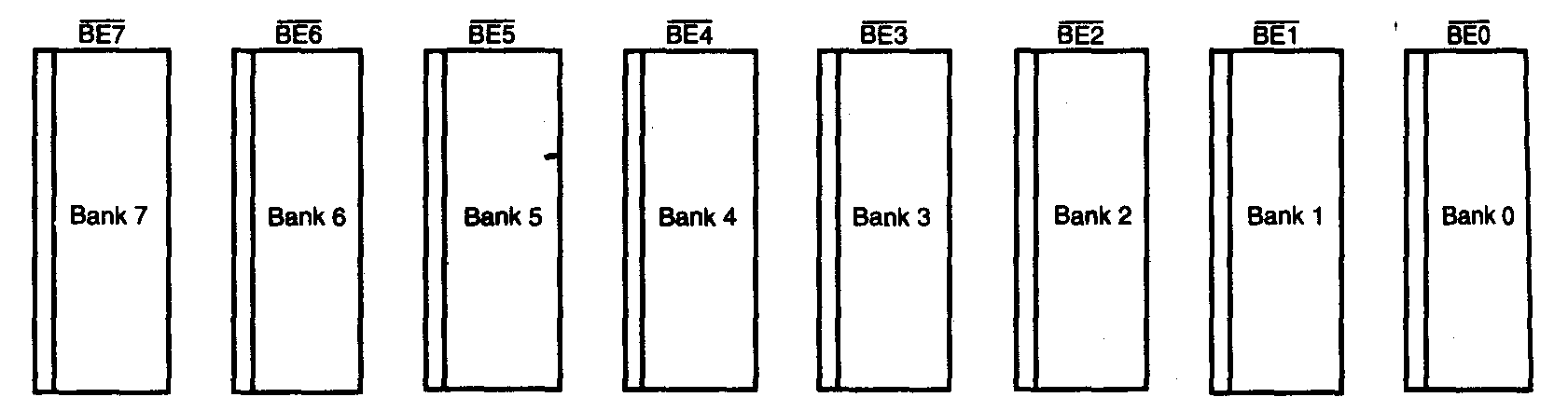

The memory system for the Pentium microprocessor is 4G bytes in size, just as in the 8O386DX and 80486 microprocessors. The difference lies in the width of the memory data bus. The Pentium uses a 64-bit data bus to address memory organized in eight banks that each contains 512Mbytes of data. The figure shows the organization of the Pentium physical memory system.

The Pentium memory system is divided into eight banks that each stores a byte of data with a parity bit. The Pentium employs internal parity generation and checking logic for the memory system’s data bus information. The 64-bit wide memory is important to double-precision floating-point data. Because of the change to a 64-bit wide data bus, the Pentium is able to retrieve floating-point data with one read cycle, instead of two as in the 80486.

The 8-byte wide memory banks of the Pentium microprocessor.

Memory selection is accomplished with the bank enable signals ( —

— ). These separate memory banks allow the Pentium to access any single byte, word, doubleword, or quadword with one memory transfer cycle..

). These separate memory banks allow the Pentium to access any single byte, word, doubleword, or quadword with one memory transfer cycle..

A new feature added to the Pentium is its capability to check and generate parity for the address bus (A3 1—A5) during certain operations. The AP pin provides the system with parity information and the  indicates a bad parity check for the address bus. The Pentium takes no action when an address parity error is detected. The error must be assessed by the system and the system must take appropriate action (an interrupt), if so desired.

indicates a bad parity check for the address bus. The Pentium takes no action when an address parity error is detected. The error must be assessed by the system and the system must take appropriate action (an interrupt), if so desired.

The Pentium can function with a 32-bit wide memory system by using a multiplexer to convert the 64-bit data bus to a 32-bit data bus. A set of bi-directional multiplexers bi-directional buffers are used as multiplexers are used to convert the Pentium’s 64-bit data bus into a 32-bit data bus.

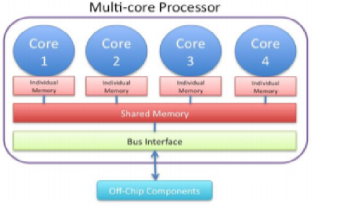

Multicore processors work on multiple instructions and multiple data. Multiple cores execute multiple threads (multiple processes/instructions) while using different parts of memory (multiple data). This enhances TLP. The main memory is shared by all cores. Each core is associated with its own cache and they all share the system bus.

References

1. Microprocessor Architecture, Programming, and Applications with the 8085 Textbook by Ramesh S. Gaonkar

2. Microprocessor Book by A.P.Godse and D.A.Godse

3. Microprocessor And Microcontroller Book by A.P.Godse