Unit 6

Design for Testability

A fault model is an engineering model that could go wrong in the construction or operation of a piece of equipment.

From the model, the designer or user can then predict the consequences of this particular fault.

Fault models can be used in almost all branches of engineering.

Basic fault models in digital circuits include:

- The stuck-at fault model.

In this, a signal, or gate output, is stuck at a 0 or 1 value, independent of the inputs to the circuit.

Here, two signals are connected together when they should not be. Depending on the logic circuitry employed, this may result in a wired-OR or wired-AND logic function. Since there are O(n2) potential bridging faults, they are normally restricted to signals that are physically adjacent in the design.

This model describes faults for CMOS logic gates. At transistor level, a transistor maybe stuck-short or stuck-open. In stuck-short, a transistor behaves as it is always conducts (or stuck-on), and stuck-open is when a transistor never conducts current (or stuck-off). Stuck-short will produce a short between VDD and VSS.

Here a wire is assumed broken, and one or more inputs are disconnected from the output that should drive them. As with bridging faults, the resulting behavior depends on the circuit implementation.

- The transition delay fault (or transition fault) model, where the signal eventually assumes the correct value, but more slowly (or rarely, more quickly) than normal.

Small-delay-defect mode

The basic principle of the path sensitization method is to choose some path from the origin of the fault to the circuit output. A path is sensitized if the inputs to the gates along the path are assigned values such that the effect of the fault can be propagated to the output.

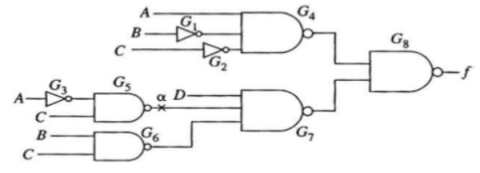

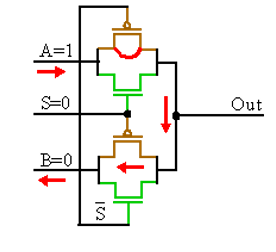

Figure 1. Path Sensitizing

From the above fig. Assume that the line α is s-a-1.

Hence to test for α, both G3 = C = 1. Also D = G6 =1 so that G7 =1 if the fault is absent. To propagate the fault from G7 to output f via G8 requires G4 = 1.

This is because if G4 = 0 then output f will be forced to be 1.

The process of propagating the effect of the fault from its original location to the circuit output is known as forward trace.

Similar is the process of backward trace.

Random pattern testing has been a common practice in industry for a long time. It was recognized quite early in the development of test generation strategies that there is a lot to be gained if a short random test precedes the long and laborious deterministic test.

A random test is defined as a random selection of input vectors. The input vectors may or may not be equally likely. A random test is said to be uniform if all input vectors are equally probable, and said to be biased otherwise. It is important to note that no test is truly random. The reason is that no ideal random number generator exists.

Key takeaways:

A random test is defined as a random selection of input vectors. The input vectors may or may not be equally likely.

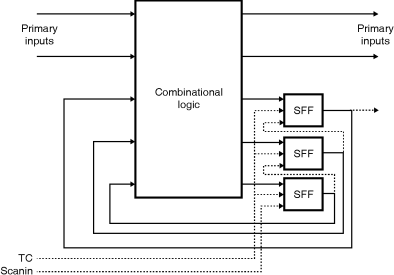

As the complexity of VLSI circuits increases, test generation and application becomes an expensive and not always very effective means of testing. Built-in Self Test (BIST) is another solution.

It is a mechanism that permits a machine to test itself. Engineers design BISTs to meet requirements such as:

or constraints such as:

The main purposeof BIST is to reduce the complexity, and thereby decrease the cost and reduce reliance upon external (pattern-programmed) test equipment.

It reduces cost in two ways:

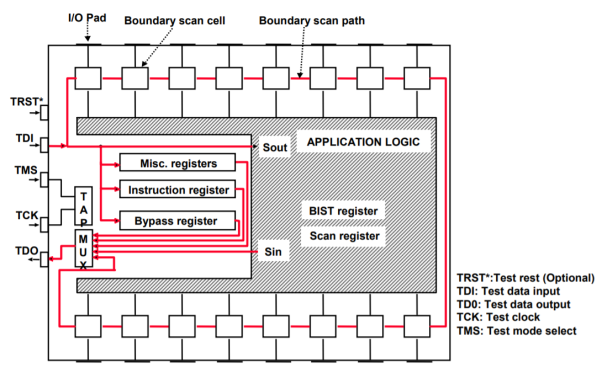

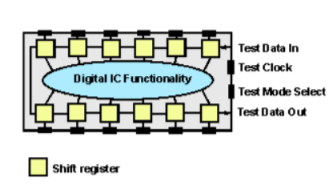

Figure below shows the Built-in Self Test system.

Figure 2. BIST

Advantages :

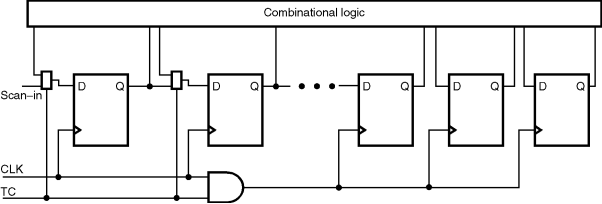

In boundary scan test we design the chip to increase observability and controllability

If each register could be observed and controlled, test problem reduces to testing combinational logic between registers.

The logic blocks enter the test mode where they generate test patterns and report the results automatically.

Figure 3. Boundary scan

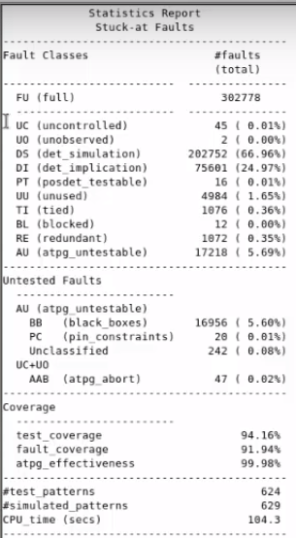

Fault Coverage contains the percentage of faults detected from all the faults of the test patterns generated by the tool

FC = DT + (PD * posdet_credit) / Total faults x 100

where DT is the detected faults class which includes all the faults that the ATPG identifies as detected and this are classified into two groups

PD – posdet or possible detected fault class includes all the faults that fault simulation identifies as possible detected but not hard to detect

Figure 4. Report_statistics of faults

From the report Total no of faults are given as 302778

Faults due to unused pins (UU), Tied pins (TI), Blocked Pins (BL), and redundant logic (RE) are untestable by tool and this faults must be excluded from the total number of faults while calculating the Test Coverage and considered while calculating the Fault Coverage.

UU+TI+BL+RE => 4984+1076+12+1072 = 7144

Thus Testable faults are given asTotal Faults – (UU+TI+BL+RE)

Total faults detected during simulation (DS) and implication (DI) are

DS +DI => 202752+75601+16 = 278369

In generalposdet_credit will be set to zero and with this above faults numbers we can have Test Coverage and Fault Coverage

TC = DT +0 / Testable faults x 100

TC = 278369/ 302778-7144 x 100

TC = 94.16 %

FC = DT +0/ Total faults x 100

FC = 278369/302778 x 100

FC = 91.94%

In this process TC and FC are calculated and we need to achieve 99 % Test Coverage for Stuck At fault model and 95% Test Coverage for At Speed fault model.

The increasing capability of being able to fabricate a very large number of transistors on a single integrated-circuit chip and the complexity of the possible systems has increased the importance of being able to test such circuits in an acceptable way and in an acceptable time. The time difficulties of tests are primarily due to the limited number of input/output connections on a chip which is the only means of access to the circuit, the ratio of the number of gates on a chip to the number of accessible I/Os increasing with chip size.

6.8.1 Design for Testability concept

Controllability: The ability to set some circuit nodes to a certain states or logic values.

• Observability: The ability to observe the state or logic values of internal nodes.

Some of the concepts include:

Speed up test generation

• Improve the design testability

• Guide the DFT insertion

With a stuck at fault model we apply a structural test approach. Instead of testing all combination of 1’s and 0’s to a VLSI device, we test with a reduced set of test vectors.

Stuck at Fault Models operate at the logic model of digital circuits. An input or an output can be Stuck at Zero (S@0) or Stuck at One (S@1).

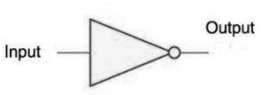

Its use three digital circuits to illustrate: Inverter, NAND, NOR. In CMOS technology, these logic gates can be found in most logic functions.

Figure 5. Not Gate

Logic table

A | D |

0 | 1 |

1 | 0 |

Inverter Stuck faults list: A S@0,A S@1, D S@0, D S@1

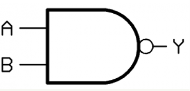

Figure 6. AND gate

A | B | Y |

1 | 0 | 1 |

1 | 1 | 0 |

0 | 0 | 1 |

0 | 1 | 1 |

NAND Stuck faults list: A S@0,A S@1, BS@0, B S@1, CS@0, C S @1

Figure 7. NOR gate

NOR Logic Table

A | B | Y |

1 | 0 | 1 |

1 | 1 | 0 |

0 | 0 | 1 |

0 | 1 | 1 |

NOR Stuck faults list: A S@0, A S@1, B S@0, B S@1, C S@0, C S@1

Testing with Stuck at Fault Model

With a stuck at fault you apply a pattern (set of 1’s and 0’s) to the inputs of the logic gate such that you get a faulty response. So,let’s start with the inverter. Suppose A is S@1. Easy test, you need to apply a 0. Now lets’ look at the output D stuck at 0, you need to apply a 0 to A. Table below tabulates the test pattern per S@ fault.

S@ Fault | Test A | Pass D | Failing D |

A S@1 | 0 | 1 | 0 |

A S@0 | 1 | 0 | 1 |

DS@1 | 1 | 0 | 1 |

D S@0 | 0 | 1 | 0 |

Now there are 4 faults to test you need 2 tests as shown in the table below. This is called as fault collapsing.

Inverter S@ Fault Coverage of Tests

A | Stuck @ Faults Detected |

1 | A-S@0, D-S@1 |

0 | A-S@1, D-S@0 |

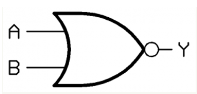

6.9.1 Stuck Open and Stuck short faults

Figure8. SOP model

First pattern initializes the output node, second pattern checks for the presence of the fault.

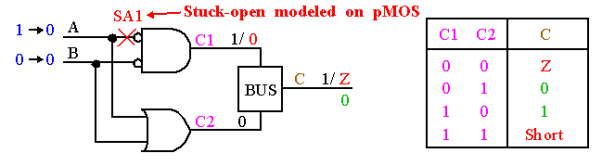

Figure 9. Stuck open model

In fault free circuit, this must be true rsince complementary logic functions drive BUS.

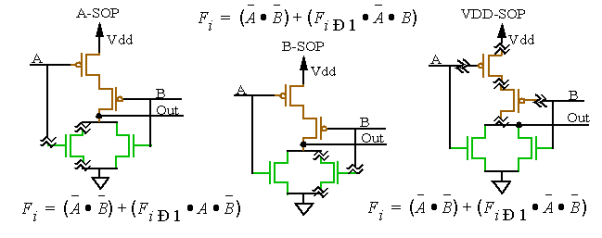

Stuck-short (Stuck-on) Faults

A transistor that is permanently stuck-on will, for some input combination(s), compete with its complementary transistors for control of the output.

Sometimes this competition does not result in a catastrophic failure.

Figure 10. Stuck ON

The output value depends on driving transistor resistances. Strength of upstream drivers. Delay fault is likely if functional behaviour is preserved. IDDQ test guarantees detection.

Stuck-short faults modeled as SA0 on pMOS in gate-level equivalent model.

Boundary-scan cells in a device can capture data from integrated circuit line, or force data onto them. In this way a test system that can input a data stream to the shift register chain can set up states on the board, and also monitor data. By setting up one serial data stream, latching this into place, and then monitor the returning data stream, it is possible to gain access to the circuits on the board and check that a returning data stream is what is expected. If it is, then the test can pass, but if not the boundary scan system has detected and problem that can be further investigated.

Figure 12. JTAG technology

Under normal operating conditions the cell is set so that it has no effect and it becomes invisible. However when the device is set to test mode, it permits a serial data stream (test vector) to be passed from one shift register latch cell to the next.

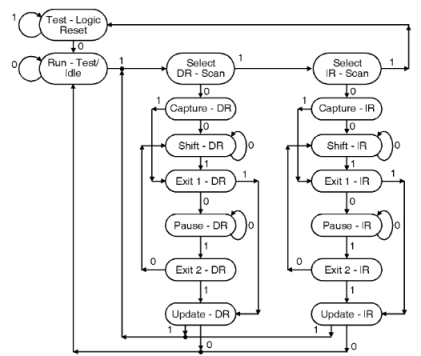

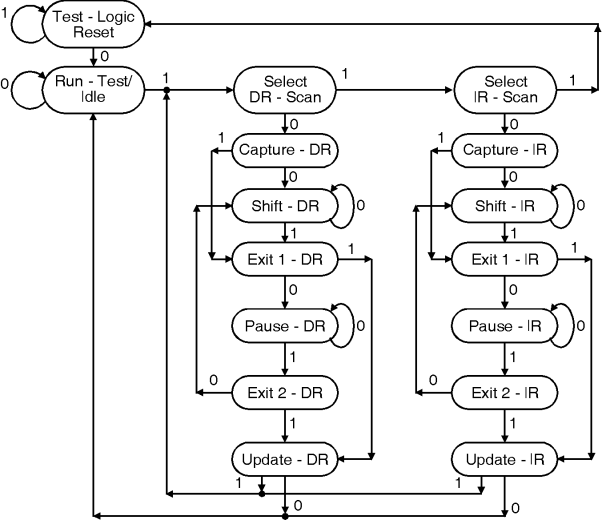

JTAG Interface

There are a number of JTAG control and data lines that form the test access port, TAP. These lines known as TCK, TMS and the optional TRST line are connected in parallel to the chips in the boundary scan chain. Connections designated TDI (input) and TDO (output) are daisy chained together to provide a path around the boundary scan chips for the data. Data is sent into the TDI of the first chip, and then TDO from the first chip is connected to TDI of the next and so forth. Finally the data is taken from the TDO of the last IC in the daisy chain.

Key Take Aways

It is used in a variety of other test scenarios, including product development and debugging as well as field service

Figure13. TAP controller

6.12.1 TAP controller state diagrams

The TAP controller is a finite state machine that responds to changes at the TMS and TCK signals of the TAP and controls the sequence of operations of the circuitry defined by standard. It also controls the scanning of data into the various registers of the JTAG architecture. Two state transition paths for scanning the signal at TDI, one for shifting to the instruction register and one for shifting data into the active data register. The state diagram is shown in figure below. All state transitions of the TAP controller shall occur based on the value of TMS at the time of a rising edge of TCK. Actions of the test logic shall occur on either the rising or the falling edge of TCK in each controller state. The behavior of the TAP controller and other test logic in each of the controller states is briefly described as follows.

Figure 14. JTAG TAP controller states flow

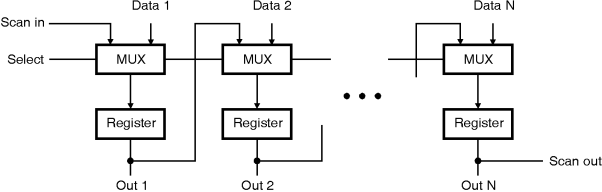

scan path can be created by the logic designers who are designing the circuit, or it can be created by software during the synthesis process. when scan is designed into the ICs, it is designed for optimal testing of the IC, without efforts. During test the flip-flops are configured for serial shift mode. In serial shift mode, logic values are loaded by serially shifting in the desired values. Figure below shows a simple technique for creating the scan path which consists of placing a multiplexer just ahead of each flip-flop. One input to the 2:1 multiplexer is driven by normal operational while the other input with one exception is driven by the output of another flip-flop. The multiplexer control line, connected to a primary input pin in mode control. Mode control gives the parallel load for normal operation and selects serial shift. The scan path can be tested by shifting a special pattern through the scan path before even beginning to address stuck-at faults in the combinational logic.

Figure 15. Scan Path

During the generation of test patterns, the automatic test pattern generation considers the flip-flops as I/O pins. When circuit with scan path is operated in the normal mode, the mode control, or test control, is set for parallel load. when the device is to be tested, the mode control alternates between parallel load and serial shift. During the operation that data are compared to expected data to determine whether the faults are present in the circuit.

6.13.1 Full and partial scan path

The importance of full scan lies in high-fault coverage for structural defects. Full scan testing of scan circuits is carried out in two phases. The first phase tests the scan register by a shift test. The shift test is used in both single-clock and two-clock designs. On the other hand in second phase, stuck-at faults in the combinational logic are considered and a program is used to generate the test vectors. Further, combinational test vectors are converted into scan sequences and applied to the circuit. The expected output response at primary outputs is specified at clock. Figure below shows full scan testing.

Figure 16. Full scan path

Partial scan path

Partial scan is mainly used to test the circuit in which some of the flip-flops are stitched into a scan path. The partial scan chain includes flip-flops from status registers, counters, and state machines. A drawback to partial-scan is if a complete scan-path exists, automatic test pattern generation is simplified and there is no need for an automatic test pattern generation for sequential test patterns. The benefits of partial scan are, if the automatic test pattern generation handle latches, combinational loops, and loop-free sequential logic it is possible to achieve acceptable fault coverage. Figure below shows the partial scan in which the values in the flip-flops on the right side of the circuit are fixed when the test control is 0, whereas the partial scan flip-flops on the left side are loaded by means of the scan-in input.

Figure17. Partial scan path

References:

Fundamentals of Modern VLSI Devices Book by Tak H. Ning and Yuan Taur

Introduction to VLSI systems Book by Carver Mead

VLSI physical design automation Textbook by Sadiq Sait

Cmos Digital Integrated Circuits Book by Sung-Mo Kang and Yusuf Leblebici