Unit - 1

Semiconductor Diodes

Intrinsic and Extrinsic Semiconductors

Semiconductors

Semiconductors are materials that have conductivity between conductors and insulators.

Semiconductors can be pure elements, such as silicon or germanium, or compounds such as gallium arsenide or cadmium selenide.

They are not good conductors nor good insulators as their name “semi”-conductors.

These materials such as silicon (Si), germanium (Ge), and gallium arsenide (GaAs), have electrical properties somewhere in the middle, between those of a “conductor” and an “insulator”.

They have very few “free electrons” because their atoms are closely grouped in a crystalline pattern called a “crystal lattice” but electrons are still able to flow, but only under special conditions.

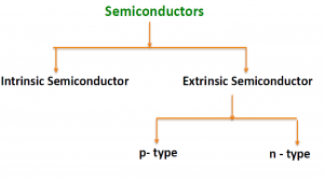

There are two basic groups or classifications that can be used to define the different semiconductor types:

- Intrinsic Semiconductor

- Extrinsic Semiconductor

Figure 1: Type of semiconductor

The semiconductor is divided into two types. One is an Intrinsic Semiconductor and the other is an Extrinsic semiconductor. The pure form of the semiconductor is known as the intrinsic semiconductor and the semiconductor in which intentional impurities are added for making it conductive is known as the extrinsic semiconductor.

The conductivity of the intrinsic semiconductor becomes zero at room temperature while the extrinsic semiconductor is very little conductive at room temperature. The detailed explanation of the two types of the semiconductor is given below.

Intrinsic Semiconductor

An intrinsic type of semiconductor material made to be very pure chemically. As a result, it possesses a very low conductivity level having very few charge carriers, namely holes and electrons, which it possesses in equal quantities.

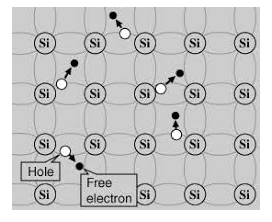

Figure 2: Intrinsic Semiconductor

The most commonly used semiconductor basics material by far is silicon. Silicon has four valence electrons in its outermost shell which it shares with its neighbouring silicon atoms to form a full orbital of eight electrons. The structure of the bond between the two silicon atoms is such that each atom shares one electron with its neighbour making the bond very stable.

As there are very few free electrons available to move around the silicon crystal, crystals of pure silicon (or germanium) are therefore good insulators. Silicon atoms are arranged in a definite symmetrical pattern making them a crystalline solid structure. A crystal of pure silica (silicon dioxide or glass) is generally said to be an intrinsic crystal (it has no impurities) and therefore has no free electrons.

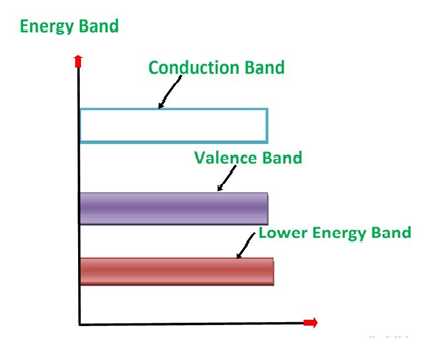

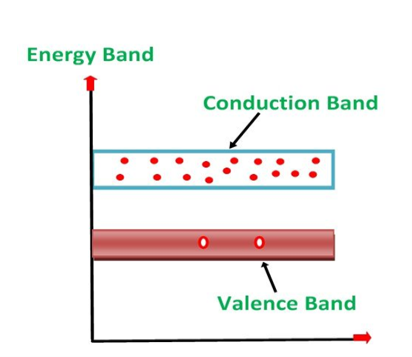

An extremely pure semiconductor is called an Intrinsic Semiconductor. Based on the energy band phenomenon, an intrinsic semiconductor at absolute zero temperature is shown below.

Figure 3: Intrinsic semiconductor at absolute zero temperature.

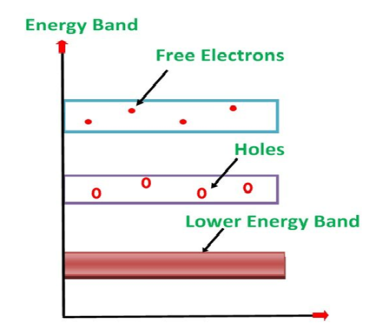

Its valence band is filled and the conduction band is empty. When the temperature is raised and some heat energy is supplied to it, some of the valence electrons are lifted to the conduction band leaving behind holes in the valence band as shown below.

Figure 4: Intrinsic semiconductor at T >0

A hole is the absence of an electron in a particular place in an atom. Although it is not a physical particle in the same sense as an electron, a hole can be passed from atom to atom in a semiconductor material. It is considered to have a positive charge. Holes are positive charge carriers.

The electrons reaching the conduction band move randomly. The holes created in the crystal also free to move anywhere.

This behaviour of the semiconductor shows that they have a negative temperature coefficient of resistance. This means that with the increase in temperature, the resistivity of the material decreases, and the conductivity increases.

But simply connecting a silicon crystal to a battery supply is not enough to extract an electric current from it. To do that we need to create a “positive” and a “negative” pole within the silicon allowing electrons and therefore electric current to flow out of the silicon. These poles are created by doping the silicon with certain impurities.

Doping

The process by which an impurity is added to a semiconductor is known as Doping. The amount and type of impurity which is to be added to the material have to be closely controlled during the preparation of extrinsic semiconductor. Generally, one impurity atom is added to 108 atoms of a semiconductor.

The purpose of adding impurity in the semiconductor crystal is to increase the number of free electrons or holes to make it conductive.

If a Pentavalent impurity, having five valence electrons is added to a pure semiconductor a large number of free electrons will exist. Which makes an n-type extrinsic semiconductor.

If a trivalent impurity having three valence electrons is added, a large number of holes will exist in the semiconductor. Which makes a p-type extrinsic semiconductor.

Extrinsic Semiconductor

Extrinsic types of semiconductors are those where a small amount of impurity has been added to the basic intrinsic material. This 'doping' uses an element from a different periodic table group and in this way, it will either have more or fewer electrons in the valence band than the semiconductor itself. This creates either an excess or shortage of electrons. In this way two types of semiconductors are available: Electrons are negatively charged carriers. Holes are positively charged carriers.

Depending upon the type of impurity added the extrinsic semiconductor may be classified as an n-type semiconductor and p-type semiconductor.

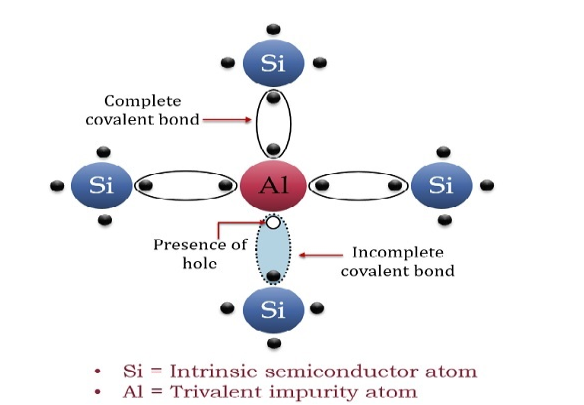

P-Type Extrinsic Semiconductor

The extrinsic p-Type Semiconductor is formed when a trivalent impurity is added to a pure semiconductor in a small amount, and as a result, a large number of holes are created in it. A large number of holes are provided in the semiconductor material by the addition of trivalent impurities like Gallium and Indium. Such type of impurities which produce a p-type semiconductor is known as an Acceptor Impurities because each atom of them creates one hole which can accept one electron.

In a P-type semiconductor material, there is a shortage of electrons, i.e. there are 'holes' in the crystal lattice. Electrons may move from one empty position to another and in this case, it can be considered that the holes are moving. This can happen under the influence of a potential difference and the holes can be seen to flow in one direction resulting in an electric current flow. It is harder for holes to move than for free electrons to move and therefore the mobility of holes is less than that of free electrons. Holes are positively charged carriers.

A trivalent impurity like Aluminium, having three valence electrons is added to Silicon crystal in a small amount. Each atom of the impurity fits in the Silicon crystal in such a way that its three valence electrons form covalent bonds with the three surrounding Silicon atoms as shown in the figure below.

Figure 5: P-Type Semiconductor

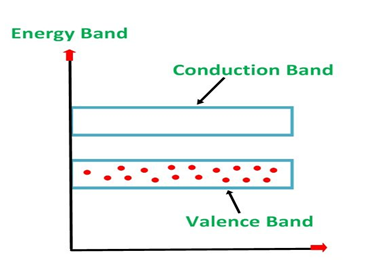

Energy Band Diagram of P-Type Semiconductor

The energy band diagram of a p-Type Semiconductor is shown below.

Figure 6: Energy band diagram of a p-Type Semiconductor

A large number of holes or vacant space in the covalent bond is created in the crystal with the addition of the trivalent impurity. A small or minute quantity of free electrons is also available in the conduction band.

They are produced when thermal energy at room temperature is imparted to the Silicon crystal-forming electron-hole pairs. But the holes are more in number as compared to the electrons in the conduction band. It is because of the predominance of holes over electrons that the material is called a p-type semiconductor. The word “p” stands for positive material.

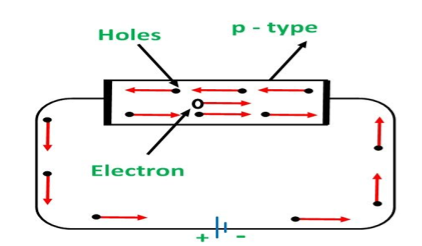

Conduction through P Type Semiconductor

In p-type semiconductors, a large number of holes are created by the trivalent impurity. When a potential difference is applied across this type of semiconductors.

Figure 7: Conduction through p type semiconductor

The holes are available in the valence band are directed towards the negative terminal. As the current flow through the crystal is by holes, which are a carrier of positive charge, therefore, this type of conductivity is known as positive or p-type conductivity. In a p-type conductivity, the valence electrons move from one covalent to another.

The conductivity of an n-type semiconductor is nearly double that of a p-type semiconductor. The electrons available in the conduction band of the n-type semiconductor are much more movable than holes available in the valence band in a p-type semiconductor. The mobility of holes is poor as they are more bound to the nucleus.

Even at room temperature, the electron-hole pairs are formed. These free electrons which are available in minute quantity also carry a little amount of current in the p-type semiconductors.

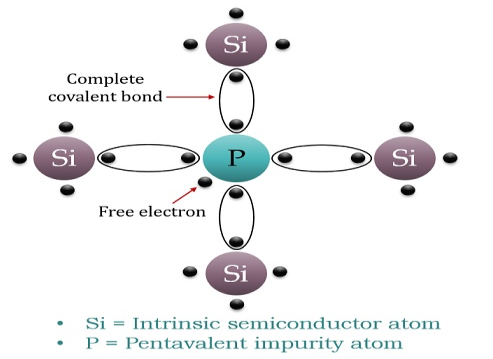

N-Type Extrinsic Semiconductor

When a few Pentavalent impurities such as Phosphorus whose atomic number is 15, which is categorized as 2, 8, and 5. It has five valence electrons, which are added to silicon crystals. Each atom of the impurity fits in four silicon atoms as shown in the figure below.

Hence, each Arsenic atom provides one free electron in Silicon crystal. Since an extremely small amount of Phosphorus, impurity has a large number of atoms; it provides millions of free electrons for conduction.

Figure 8: N-type semiconductor

An N-type semiconductor material has an excess of electrons. In this way, free electrons are available within the lattices, and their overall movement in one direction under the influence of a potential difference results in an electric current flow. This is an N-type semiconductor, the charge carriers are electrons.

Energy Diagram of N-Type Semiconductor

A large number of free electrons are available in the conduction band because of the addition of the Pentavalent impurity. These electrons are free electrons that did not fit in the covalent bonds of the crystal. However, a minute quantity of free electrons is available in the conduction band forming hole- electron pairs.

The Energy diagram of the n-type semiconductor is shown in the figure below.

Figure 9: Energy diagram of the n-type semiconductor

- The addition of pentavalent impurity results in a large number of free electrons.

- When thermal energy at room temperature is imparted to the semiconductor, a hole-electron pair is generated and as a result, a minute quantity of free electrons is available. These electrons leave behind holes in the valence band.

- Here n stands for negative material as the number of free electrons provided by the pentavalent impurity is greater than the number of holes.

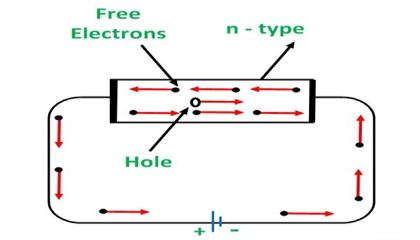

Conduction Through N-Type Semiconductor

In the n-type semiconductor, a large number of free electrons are available in the conduction bands which are donated by the impurity atoms. The figure below shows the conduction process of an n-type semiconductor.

When a potential difference is applied across this type of semiconductor, the free electrons are directed towards the positive terminals. It carries an electric current. As the flow of current through the crystal is constituted by free electrons which are carriers of a negative charge, therefore, this type of conductivity is known as negative or n-type conductivity.

Figure 10: Conduction through n-type semiconductor

The electron-hole pairs are formed at room temperature. These holes which are available in small quantities in the valence band also consist of a small amount of current. For practical purposes, this current is neglected.

Key Takeaways

- Semiconductors are materials that have conductivity between conductors and insulators.

- The semiconductor is divided into two types. One is an Intrinsic Semiconductor and the other is an Extrinsic semiconductor.

- The pure form of the semiconductor is known as the intrinsic semiconductor

- The semiconductor in which intentional impurities are added for making it conductive is known as the extrinsic semiconductor.

- A hole is the absence of an electron in a particular place in an atom.

- The process by which an impurity is added to a semiconductor is known as Doping.

- Depending upon the type of impurity added the extrinsic semiconductor may be classified as an n-type semiconductor and p-type semiconductor.

- The extrinsic p-Type Semiconductor is formed when a trivalent impurity is added to a pure semiconductor in a small amount, and as a result, a large number of holes are created in it.

- The extrinsic n-Type Semiconductor is formed when a Pentavalent impurity is added to a pure semiconductor in a small amount, and as a result, a large number of electrons are created in it.

1.2.1 Conductivity

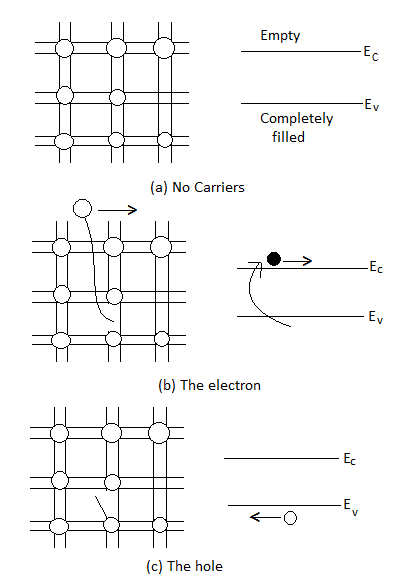

We already know that that there are no carriers or possible current flow if the bonding model has no broken bonds. Equivalently, in the energy band model, if the valence band is completely filled with electrons and the conduction band is devoid of electrons. There are no carriers or possible current flow. This lack of carriers and associated current flow is easy to understand in terms of the bonding model where the shared electrons are viewed as being tied to the atomic cores.

As accurately portrayed in the energy band model, however, the valence band electrons actually move about in the crystal. How is it then that no current can arise from this group of electrons? As it turns out, the momentum of the electrons is quantized in addition to their energy. Moreover, for each and every possible momentum state in a band, there is another state with an oppositely directed momentum of equal magnitude. Thus, if a band is completely filled with electrons, the net momentum of the electrons in the band is always identically zero. It follows that no current can arise from the electrons in a completely filled energy band.

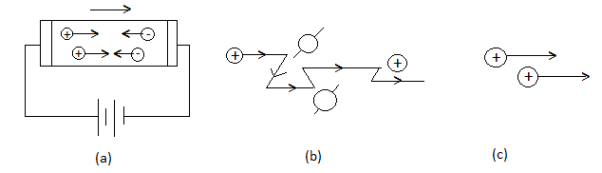

Figure 11: Visualization of carriers using the bonding model (left) and the energy band model (left) (a) No-carrier situation (b) Visualization of electrons (c) Visualization of hole.

The electrons that do give rise to charge transport are visualized in Figure above. When a Si—Si bond is broken and the associated electron is free to wander about the lattice, the released electron is a carrier. Equivalently, in terms of the energy band model, excitation of valence band electrons into the conduction band creates carriers; that is, electrons in the conduction band are carriers.

Note that the energy required to break a bond in the bonding model and the band gap energy are one and the same thing. Likewise. Freed bonding-model electrons and conduction band electrons are just different names for the same electrons.

In addition to releasing an electron the breaking of a Si-Si bond also creates a missing bond or void in the bonding structure.

By bonding modelled one can visualize the movement of this missing bond from place to place in the lattice as a result of nearby bound electrons jumping into the void

By the energy band model one can visualize the removal of an electron from the valence band creates an empty state in vast sea of filled stales. The empty slate in the valence band. Is the second type of carnet found in semi-conductors—the hole. Both electrons and holes participates in the operation of most semiconductor devices.

Drift current and diffusion currents

In case of semiconductors we observe two kinds of currents.

- Drift current

- Diffusion current

Drift current Definition: The flow of electric current due to the motion of charge carriers under the influence of external electric field is called drift current.

When an electric field E is applied across a semiconductor material, the charge carriers attain a drift velocity vd

So drift velocity vd =μ.E

The relation between current density J and drift velocity vd is

J = Nqvd

Where N is the carrier concentration

q is the charge of electron or hole

From equations (1) and (2), we get

Jdrift = NqμE

μ is the mobility of charge carrier.

The above equation shows the general expression for drift current density. Drift current density due to electrons is

Je(drift) = neμeE

Where n is the electrons carrier concentration

And μe is the mobility of electrons.

Drift current density due to holes is

Jh(drift) = peμhE

Where p is the carrier concentration of holes.

μh is the mobility of holes

So Total drift current density

Jdrift (total) = Je(drift) + Jh(drift) = neμeE + peμhE

= eE (nμe+pμh )

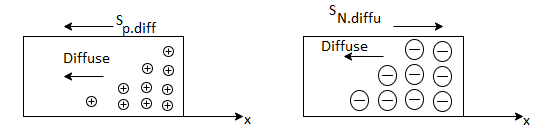

Diffusion current

Diffusion is a process whereby particles tend to spread out or redistribute as a result of their random thermal motion, migrating on a macroscopic scale from regions of high particle concentration into regions of low particle concentration. If allowed to progress unabated.

The diffusion process operates so as to produce a uniform distribution of particles. The diffusing entity, it should be noted, need not be charged; thermal motion, not interparticle repulsion, is the enabling action behind the diffusion process.

In semiconductors the diffusion process on a microscopic scale in similar so that occurring in the hypothetical system, the random motion of the diffusing particles is three-dimensional and not “compartmentalised.” On a macroscopic scale the net effects of diffusion is precisely she same within both the hypothetical system and semiconductors; there is an overall migration of particles from a region of concentration to the region of low particle concentration Within semiconductors the electrons and holes are charged, and diffusion-current carrier transport therefore given rise to particle currents as shown in figure.

Figure 12: Diffusion at macroscopic level

Definition: The flow of electric current due to the motion of charge carriers under concentration gradient is called diffusion current

Or

The motion of charge carriers from the region of higher concentration to lower concentration leads to a current called diffusion current.

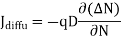

Let ∆N be the excess electron concentration. Then according to Fick’s law, the rate of diffusion of charge carriers is proportional to concentration gradient

Rate of diffusion of charge ∝ -

=

Where D is the diffusion coefficient of charge carriers.

The negative sign indicates decrease of N with increase of x So,

The diffusion current density Jdiffu is

Where q is the charge of the charge carrier

Diffusion current density due to holes is

Jdiffu (hole) = - eDh

Diffusion current density due to electrons is (as electron carry negative charge so we will get +sign here.

Jdiffu (electrons) = eDe

Jdiffu (total) = Jdiffu (hole) + Jdiffu (electrons)

Jdiffu (total) = - eDh + eDe

+ eDe

The expression for total current density due to holes is

Jh (total) = Jh(drift) + Jdiffu (hole) = peμhE - eDh

The expression for total current density due to electrons is

Je (total) = Je(drift) + Jdiffu (electrons) = neμeE + eDe

1.2.2 Mobility

The drift velocity produced per unit electric field is called 'mobility' , Thus Mobility is obviously a central parameter in characterizing electron and hole transport due to drift.

μ =  or μE =

or μE =

The word mobility refers to freedom of movement. Analogously, in semiconductor work the mobility parameter is a measure of the ease of carrier motion in a crystal. Increasing the motion-impeding collisions within a crystal decreases the mobility of the carriers.

In other words, the carrier mobility varies inversely with the amount of scattering taking place within the semiconductor.

Lattice scattering involving collisions with thermally agitated lattice atoms, and ionized impurity (i.e., donor-site and/or acceptor-site) scattering. Relative to lattice scattering, it should be emphasized that it is the thermal vibration, the displacement of lattice atoms from their lattice, positions, that leads to carrier scattering. The internal field associated with the stationary array of atoms in a crystal is already taken into account in the effective mass formulation.

μ = q /m*

/m*

Where  is the mean free time between collisions and m* is the conductivity effective mass.

is the mean free time between collisions and m* is the conductivity effective mass.

However, μ is also noted to vary inversely with the carrier effective mass—lighter carriers move more readily.

The carrier mobilities are essentially independent of the doping concentration. For dopings in excess of l015/cm3, the mobilities monotonically decrease with increasing NA or ND.

The mobilities of carrier depend upon temperature as μ

. For Electrons μe

. For Electrons μe

and for holes μp

and for holes μp

1.2.3 Concept of drift

Drift is charged-particle motion in response to an applied electric field.

Within semiconductors the drifting motion of the carriers on a microscopic scale can be described as follows: When an electric field (Si) is applied across a semiconductor as visualized in figure 13(a) the resulting force on the carriers tends to accelerate the +q charged holes in the direction of the electric field and the — q charged electrons in the direction opposite to the electric field. Because of collisions with ionized impurity atoms and thermally agitated lattice atoms, however, the carrier acceleration is frequently interrupted (the carriers are d to be scattered). The net result, pictured in Figure 13(b), is carrier motion generally along the direction of the electric field, but in a disjointed fashion involving repeated periods of acceleration and subsequent decelerating collisions.

Figure 13: Visualization of carrier drift: (a) motion of carriers within a biased semiconductor bar (b) drifting hole on microscopic or atomic state (c) carrier drift on a macroscopic state.

The microscopic drifting motion of a single carrier is difficult to analyse as it is complex however the measurable quantities are macroscopic observables that gives the average or overall motion of the carriers.

Averaging over all electrons or holes at any given time, we find that the resultant motion of each carrier type can be described in terms of a constant drift velocity, vd

In other words, on a macroscopic scale, drift may be visualized as nothing more than all carriers of a given type moving along at a constant velocity in a direction parallel or antiparallel to the applied electric field.

It is important to point out that the drifting motion of the carriers arising in response to an applied electric field is actually superimposed upon the always-present thermal motion of the carriers. Electrons in the conduction band and holes in the valence band gain and lose energy via collisions with the semiconductor lattice and are nowhere near stationary even under equilibrium conditions. In fact under equilibrium conditions the thermally related carrier velocities average  1/1000 the speed of light at room temperature.

1/1000 the speed of light at room temperature.

However, the thermal motion of the carriers is completely random. Thermal motion therefore averages out to zero on a macroscopic scale, does not contribute to current transport, and can be conceptually neglected.

Key Takeaways

- When a Si—Si bond is broken and the associated electron is free to wander about the lattice, the released electron is a carrier.

- Note that the energy required to break a bond in the bonding model and the band gap energy are one and the same thing.

- The empty slate in the valence band. Is the second type of carnet found in semi-conductors—the hole.

- Both electrons and holes participates in the operation of most semiconductor devices.

- Drift is charged-particle motion in response to an applied electric field.

- The drift velocity produced per unit electric field is called 'mobility'

- Resistivity is a measure of a material's inherent resistance to current flow—a "normalized" resistance that does not depend on the physical dimensions of the material.

- In case of semiconductors we observe two kinds of currents; Drift current and Diffusion current.

- The flow of electric current due to the motion of charge carriers under the influence of external electric field is called drift current. Total drift current density is given by Jdrift (total) = Je(drift) + Jh(drift) = eE (nμe+pμh )

- The flow of electric current due to the motion of charge carriers under concentration gradient is called diffusion current. Total current density due to electrons is given by Je (total) = Je(drift) + Jdiffu (electrons) = neμeE + eDe

- Drift is charged-particle motion in response to an applied electric field.

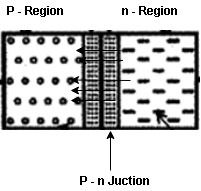

1.3.1 P-N Junction

A P-N Junction Diode is formed by doping one side of a piece of sili54con with a P-type dopant (Boron) and the other side with a N-type dopant (phosphorus). Ge can be used instead of Silicon. The P-N junction diode is a two-terminal device. This is the basic construction of the P-N junction diode. It is one of the simplest semiconductor devices as it allows current to flow in only one direction.

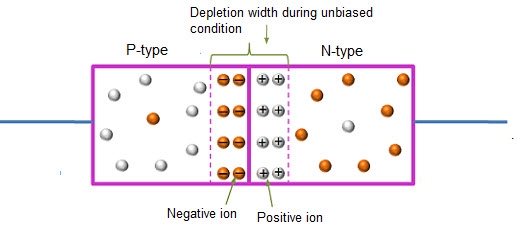

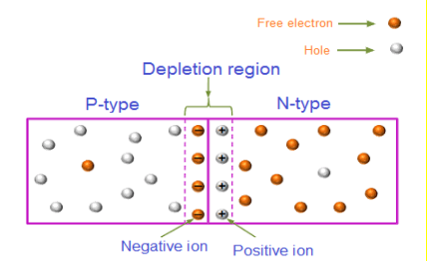

Zero Biased Condition

In this case, no external voltage is applied to the P-N junction diode; and therefore, the electrons diffuse to the P-side and simultaneously holes diffuse towards the N-side through the junction, and then combine with each other. Due to this an electric field is generated by these charge carriers. The electric field opposes further diffusion of charged carriers so that there is no movement in the middle region. This region is known as depletion width or space charge.

Figure 14: Unbiased or zero biased PN Junction Diode

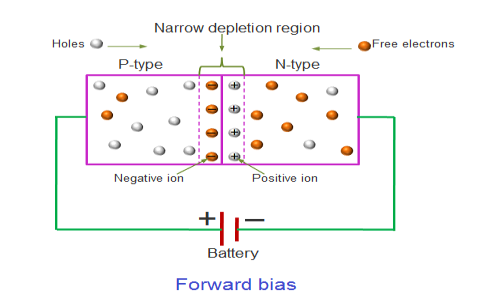

Forward Bias

In the forward bias condition, the positive terminal of the battery is connected to the P-Type material and the negative terminal of the battery is connected to the N-type material. This connection is also called as giving positive voltage.

Figure 15: Forward bias

Electrons from the N-region cross the junction and enters the P-region. Due to the attractive force that is generated in the P-region the electrons are attracted and move towards the positive terminal. Simultaneously the holes are attracted to the negative terminal of the battery. By the movement of electrons and holes current flows. In this condition, the width of the depletion region decreases due to the reduction in the number of positive and negative ions.

If this external voltage Vf becomes greater than the value of the potential barrier, approx. 0.7 volts for silicon and 0.3 volts for germanium, the potential barriers opposition will be overcome and current will start to flow.

This is because the negative voltage pushes or repels electrons towards the junction giving them the energy to cross over and combine with the holes being pushed in the opposite direction towards the junction by the positive voltage. This results in a characteristics curve of zero current flowing up to this voltage point, called the “knee” on the static curves and then a high current flow through the diode with little increase in the external voltage as shown in I-V characteristics.

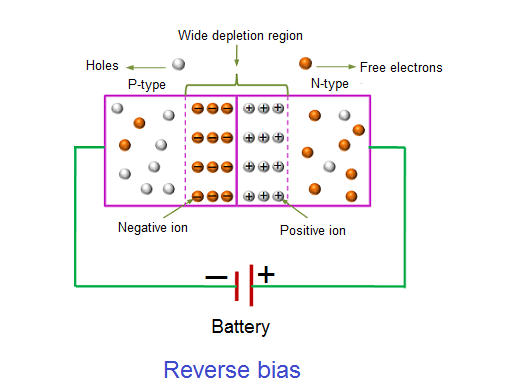

Reverse Bias

In the reverse bias condition, the negative terminal of the battery is connected to the P-type material and the positive terminal of the battery is connected to the N-type material. This connection is also known as giving negative voltage.

Figure 16: Reverse bias

The positive voltage applied to the N-type material attracts electrons towards the positive electrode and away from the junction, while the holes in the P-type end are also attracted away from the junction towards the negative electrode.

The net result is that the depletion layer grows wider due to a lack of electrons and holes and presents a high impedance path, almost an insulator. The result is that a high potential barrier is created thus preventing current from flowing through the semiconductor material.

This condition represents a high resistance value to the PN junction and practically zero current flows through the junction diode with an increase in bias voltage. However, a very small leakage current does flow through the junction which can be measured in micro-amperes, ( μA ).

If the reverse bias voltage Vr applied to the diode is increased to a sufficiently high enough value, it will cause the diode’s PN junction to overheat and fail due to the avalanche effect around the junction. This may cause the diode to become shorted and will result in the flow of maximum circuit current, and this shown as a step downward slope in the reverse static characteristics curve in I-V characteristics.

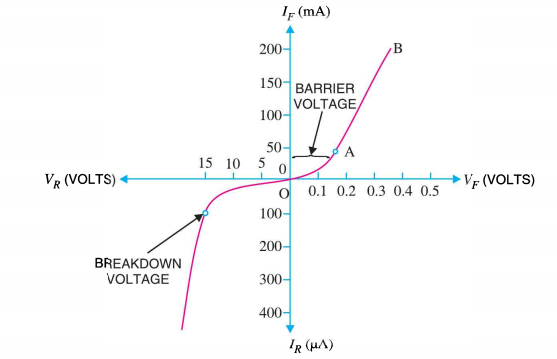

I-V Characteristics of PN Junction Diode

The I-V Characteristic Curves, which is short for Current-Voltage Characteristic Curves or simply I-V curves of an electrical device

The application of a forward biasing voltage on the junction diode results in the depletion layer becoming very thin and narrow which represents a low impedance path through the junction thereby allowing high currents to flow. The point at which this sudden increase in current takes place is represented on the static I-V characteristics curve above as the “knee” point. The current starts increasing with increase in voltage. At knee voltage current shows a sharp increment in its magnitude. This behaviour is mentioned above. As large current flow in forward biasing so we measure this current in mA.

When a junction diode is Reverse Biased, the thickness of the depletion region increases and the diode acts like an open circuit blocking current flow. So only a very small leakage current will flow.

Figure 17: I-V characteristics

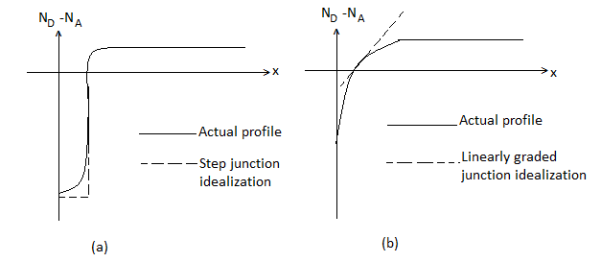

Step Junction

Fortunately, only the doping variation in the immediate vicinity of the metallurgical junction is of prime importance. Surprisingly accurate results can be obtained using rather idealized doping profiles.

Figure 18: Idealized doping profiles (a) Step junction (b) linearly graded junction.

The two most common idealizations are Step junction and linearly graded junction. The more appropriate of the two idealizations depends on the slope of the actual doping profile at the metallurgical junction and the background doping of the starting wafer.

The step junction is an acceptable approximation to an ion-implantation or shallow diffusion into starting wafer, whereas the linearly graded profile would be more appropriate for deep diffusions into a moderate to heavily doped starting wafer. In most pn junction analyses we are dealing with; we arbitrarily invoke the step junction idealization to minimize the mathematical complexity of the analysis.

Depletion Width

Depletion region or depletion layer is a region in a P-N junction diode where no mobile charge carriers are present. Depletion layer acts like a barrier that opposes the flow of electrons from n-side and holes from p-side.

Figure 19: Depletion region

At the instant of junction formation , free electrons in the N-region near the p-n junction being to diffuse across the junction and fall into holes near the junction in the P-region. The width of depletion region depends on the amount of impurities added to the semiconductor.

Figure 20: Depletion region

The Depletion region acts as a barriers to the farther movement of electrons across the junction

As positive ion & -ve ion across the junction produces a electric field across the junction -according to coulombs law.

The potential difference of the electric field across the depletion region is the amount of voltage required to move electronics through the electric field, this potential difference is called the barrier potential & is expressed in volt

The typical barrier potential is approximately 0.7 v for silicon & 0.3 v for germanium at 25c.

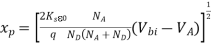

Depletion width of two sided abrupt junction can be calculated by the following formula

For one sided abrupt junction it is given by the following formula

Static and Dynamic Resistance

Static Resistance (DC Resistance) is the resistance that diode offered when the applied voltage is DC voltage. If the operating voltage and currents are fixed, then the value of this DC resistance remains constant and because of this it is called static resistance.

But if the value of operating voltage and currents are changed, then the value of this DC or the static resistance will also change.

When a DC voltage is applied to a circuit that includes a diode, its characteristic curve will have an operating point that will not change with time. The diode’s DC resistance is not sensitive to the shape of the curve and can be simply determined through the ratio of the voltage and current of the diode at the point of interest. As you’ll notice with the equation, the DC resistance of a diode will decrease if there’s an increase with the diode current or voltage.

Dynamic Resistance (AC Resistance) is the resistance of the diode when the applied voltage is AC voltage.

Ac or Dynamic Resistance the resistance of the diode is known as either AC resistance or the dynamic resistance.

We assume Diode Resistance is present before applying AC signals to the diode. Some finite DC voltage has been already applied.

If an AC voltage is applied to a diode, it becomes sensitive to the shape of the characteristic curve. The AC voltage applied will move the instantaneous operating point up and down in a region of the characteristic curve. Instead of sketching tangent lines, this equation simplifies the process of determining the AC or dynamic resistance of a diode.

Key Takeaways

- A P-N Junction Diode is formed by doping one side of a piece of silicon with a P-type dopant (Boron) and the other side with a N-type dopant (phosphorus). Ge can be used instead of Silicon.

- Zero biased condition is the case when no external voltage is applied to the P-N junction diode.

- In the forward bias condition, the positive terminal of the battery is connected to the P-Type material and the negative terminal of the battery is connected to the N-type material. This connection is also called as giving positive voltage.

- In the reverse bias condition, the negative terminal of the battery is connected to the P-type material and the positive terminal of the battery is connected to the N-type material. This connection is also known as giving negative voltage.

- The two most common idealizations are Step junction and linearly graded junction.

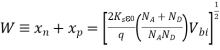

Electrostatic Relationships

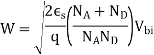

The development of quantitative relationships for the electrostatic variables deals with the step junction and is presented in detail not only to obtain the desired relationships but also to establish the derivational procedures that can be applied to other doping profiles.

Figure 21: (a) Sketch of o physical diode. (b) One-dimensional diode subjected to the applied voltage, coordinates, and contact specifications.

Assumptions

Major features of the pn junction diode subject to analysis are identified in Figure 21.

- All variables are taken to be functions only of x, the coordinate normal to the semiconductor surface.

- The device is thus said to be "one-dimensional"; obvious two-dimensional effects associated with the lateral ends of a real device are assumed to be negligible.

- For the electrostatic analysis, x = 0 is positioned at the metallurgical boundary.

- External contacts to the ends of the diode are specified to be "ohmic" in nature.

- By definition, a negligible portion of an externally applied voltage appears across an ohmic contact.

- Symbol VA is used for the applied voltage. The subscript A distinguishes the applied voltage from the internal junction voltage.

- In the initial development VA is set equal to zero, or equivalently, the device is assumed to be in equilibrium.

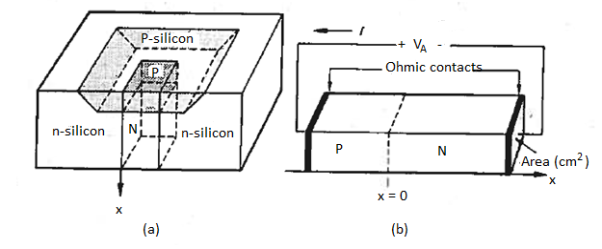

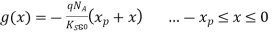

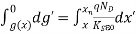

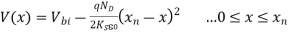

Step Junction with VA = 0

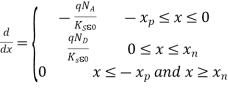

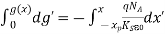

Solution for ρ

We consider a step junction under equilibrium conditions. NA is drawn greater than ND in the Figure 22(a) sketch of the doping profile for the sake of illustration. As summarized in Figure 22(b), invoking the depletion approximation yields the charge density solution

……….(1)

……….(1)

The values of xn and xp are not known at this point but will be determined later in the analysis.

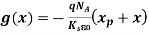

Solution for ξ

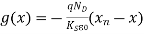

Substituting the charge density solution into Poisson's equation gives the equations to be solved for the electric field.

……….(2)

……….(2)

ξ = 0 far from the metallurgical boundary and therefore ξ = 0 everywhere outside of the depletion region. Since must also vanish right at the edges of the depletion region, ξ = 0 at x = — xp and ξ = 0 at x = xn respectively become the boundary conditions for the differential equations (1).

Separating variables and integrating from the depletion region edge to an arbitrary point x, one obtains for the p-side of the depletion region

……….(3)

……….(3)

……….(4)

……….(4)

Figure 22. Step Junction solution: Depletion approximation based quantitative solution for the electrostatic variables in pn step junction at equilibrium condition (VA= 0) (a) Step junctions profile. (b) Charge density, (c) electric field, and (d) electric potential as a function of position x.

Similarly for the n-side

……….(5)

……….(5)

……….(6)

……….(6)

The electric field solution is plotted in Figure 22(c). It is clear that

- Within the depletion region the field is always negative and exhibits a linear variation with position.

- The electric field was taken to be continuous at x = 0; the p- and n-side solutions were simply matched at the metallurgical boundary.

From Electricity and Magnetism, we know the electric field will be continuous across a boundary as long as a sheet of charge does not lie along the interface between the two regions. If the equations (4) and (6) expressions for the electric field are evaluated at x = 0 and equated, the continuity of the electric field is found to require

NAXp = NDXn ……….(7)

For those familiar with Gauss' law, the fact that ξ = 0 outside the depletion region means the total charge within the depletion region must sum to zero, or the minus charge on the p-side of the junction must balance the plus charge on the n-side of the junction.

Applied to the step junction ρ versus x plot in Figure 22(b), the balance of charge requires the rectangular areas on the p- and n-sides of the junction to be equal, or (qNAXp = qNDXn)

Thus Equation (7) gives the fact that the total charge within the depletion region must sum to zero.

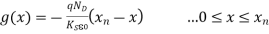

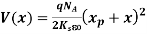

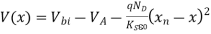

Solution for V

Since ξ = — dV/dx, the electrostatic potential is obtained by solving

…….(8)

…….(8)

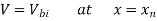

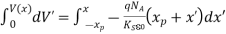

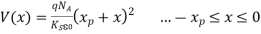

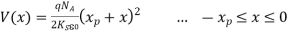

With the arbitrary reference potential set equal to zero at x = —xp, and remembering the voltage drop is Vbi across the depletion region under equilibrium conditions, Equation (8) are respectively subject to the boundary conditions given as

……….(9)

……….(9)

Separating variables and integrating from the depletion region edge to an arbitrary point x, one obtains for the p-side of the depletion region

……….(10)

……….(10)

……….(11)

……….(11)

For n side

……….(12)

……….(12)

……….(13)

……….(13)

The electrostatic potential solution given by Equations (11) and (13) is plotted in Figure 22(d). The V versus x dependence is quadratic in nature, with a concave curvature on the p-side of the junction and a convex curvature on the n-side of the junction.

Paralleling the ξ -field procedure, Fig. 5.9(d) was constructed simply by matching the p- and n-side solutions at x = 0. The assumed continuity of the electrostatic potential at x = 0 is justified because there is no dipole layer (closely spaced sheets of plus and minus charge) along the metallurgical boundary.

The Equations (11) and (13) expressions for the potential are evaluated at x =0 and equated, one obtains

…………(14)

…………(14)

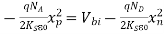

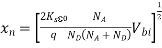

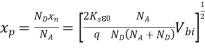

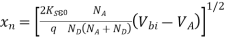

Solution for xp and xn

The electrostatic solution is not complete until the values of xp and xn are determined. Specifically, xp and xn are the only unknowns in Equations (7) and (14). Using (7) in (14) we can found xn.

…………(15)

…………(15)

And after solving further the value of xp comes to be

…………(16)

…………(16)

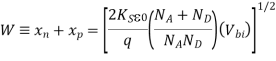

Thus we get

…………(17)

…………(17)

W is the total width of the depletion region, better known simply as the depletion width.

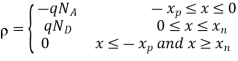

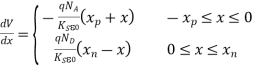

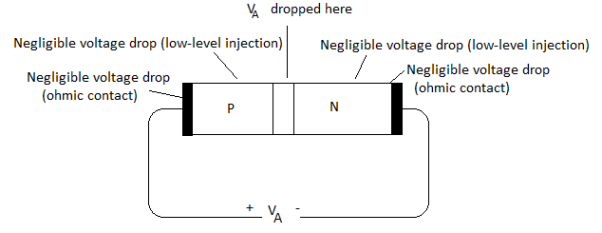

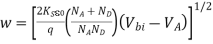

Electrostatic Relationship (Charge Density, Depletion Width, Potential, Electric Field) for VA  , VA

, VA  0 and VA

0 and VA  0,

0,

Step Junction with VA

For the practical purpose the solution for the electrostatic variables must be extended to VA  .

.

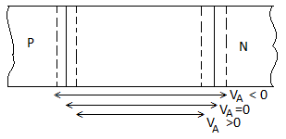

Consider the diode in Figure 23 with a voltage VA  applied to the diode terminals. This voltage must be dropped somewhere inside the diode. However, in a well-made device a negligible portion of the applied voltage appears across the contacts to the device.

applied to the diode terminals. This voltage must be dropped somewhere inside the diode. However, in a well-made device a negligible portion of the applied voltage appears across the contacts to the device.

More-over, under low-level injection conditions (reasonable current levels) the resistive voltage drop across the quasineutral p- and n-regions extending from the contacts to the edges of the depletion region will also be negligible.

The applied voltage must therefore be dropped across the depletion region. When VA> 0. This externally imposed voltage drop lowers the potential on the n-side of the junction relative to the p-side of die junction. Conversely, when VA < 0, the potential on the n-side increases relative to the p-side.

Figure 23: Voltage drops internal to a diode resulting from external applied voltage.

In other words, the voltage drop across the depletion region, and hence the boundary condition at x = xn, becomes Vbi - VA.

Since the only modification to the formation of the problem is a change in one boundary condition, the VA  electrostatic relationships can be extrapolated from the VA = 0 relationships by simply replacing all explicit appearances of Vbi by Vbi - VA.

electrostatic relationships can be extrapolated from the VA = 0 relationships by simply replacing all explicit appearances of Vbi by Vbi - VA.

Making the indicated substitution yields the VA  solution for the electrostatic variables given in Equations.

solution for the electrostatic variables given in Equations.

For -xp  x

x 0

0

…………(18)

…………(18)

…………(19)

…………(19)

…………(20)

…………(20)

For  x

x xn

xn

…………(21)

…………(21)

…………(22)

…………(22)

…………(23)

…………(23)

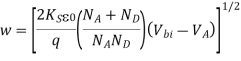

Thus depletion width become

…………(24)

…………(24)

To prevent so imaginary result, VA is obviously restricted to VA  Vbi in Equations (20), (23) and (24). The formulation fails because a large current begins to flow, and quasi-neutral region voltage drops cannot he neglected, when VA approaches Vbi.

Vbi in Equations (20), (23) and (24). The formulation fails because a large current begins to flow, and quasi-neutral region voltage drops cannot he neglected, when VA approaches Vbi.

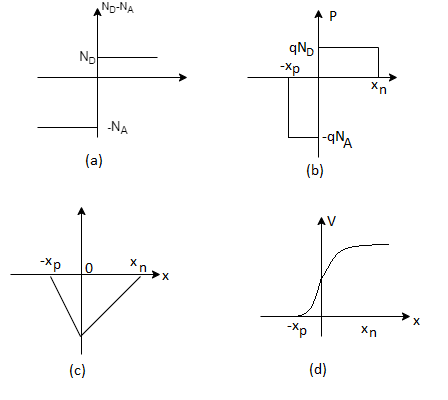

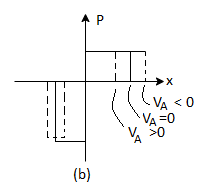

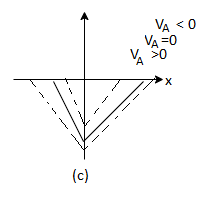

Let us see how the electrostatic variables change as a function of the applied bias. Examining the (20) and (23) relationships for xp and xn, we conclude these widths decrease under forward biasing (VA > 0) and increase under reverse biasing ( VA < 0).

The changes in xp and xn likewise translate into changes in the electric field. As deduced from Equations (18) and (21), a smaller xp and xn under forward biases cause the ξ -field to decrease everywhere inside the depletion region while-the larger xp and xn associated with reverse biases give rise to a larger ξ -field.

This conclusion is also reasonable from a physical standpoint. A decreased depletion width when VA > 0 means less charge around the junction and a correspondingly smaller ξ-field. On the other hand VA<0, creates a larger space charge region and a bigger electric field,

The potential given by Equations (19) and (22) decreases at all points when VA > 0 and increases at all points when VA < 0. The potential hill shrinks in both size and x-extent under forward biasing, whereas reverse biasing gives rise to a wider and higher potential hill.

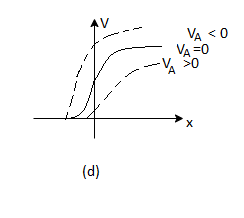

This is summarized graphically in figure 24.

|  |

|  |

Figure 24: Effect of forward and reverse biasing on the (a) depletion width, (b) charge density (c) electric field and (d) electric potential inside a pn junction diode.

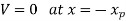

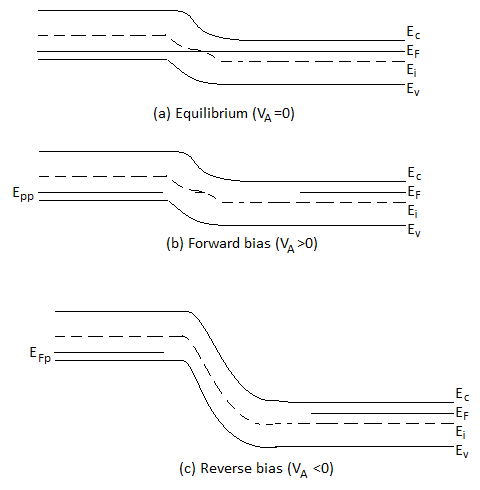

Figure 25: pn junction energy band diagrams. (a) Equilibrium (VA = 0), (b) forward bias (VA>0), and (c) reverse bias (VA< 0).

We come across that the energy band diagram under equilibrium condition. Conceptually taking the upside-down of the potential plots and appropriately modifying the equilibrium energy band diagram—smaller depletion width and smaller hill for forward bias, larger depletion width and larger hill for reverse bias—yields the diagrams for forward and reverse bias respectively pictured in Figure 25(b) and (c).

From figure it is clear the Fermi level is omitted from the depletion region because the device is no longer in equilibrium and a single level cannot be used to describe the carrier concentrations in this region. In fact, the levels labelled EFn and EFp occupying the former position of the Fermi level in the quasineutral regions, are actually majority-carrier quasi-Fermi levels.

However, the deviation from equilibrium in the non-depleted portions of the diode is normally small, especially far from the junction, and it is therefore acceptable to continue using the EF designation.

EFp - EFn = qVA

Key Takeaways

- The development of quantitative relationships for the electrostatic variables deals with the step junction

- In the initial development VA is set equal to zero, or equivalently, the device is assumed to be in equilibrium.

- Depletion width For VA =0 is given by

- With a voltage VA

applied to the diode terminals. This voltage must be dropped somewhere inside the diode.

applied to the diode terminals. This voltage must be dropped somewhere inside the diode. - Thus depletion width become With a voltage VA

- A smaller xp and xn under forward biases cause the ξ -field to decrease everywhere inside the depletion region while-the larger xp and xn associated with reverse biases give rise to a larger ξ -field.

- A decreased depletion width when VA > 0 means less charge around the junction and a correspondingly smaller ξ-field.

- On the other hand VA<0, creates a larger space charge region and a bigger electric field,

- The potential decreases at all points when VA > 0 and increases at all points when VA < 0.

- The Fermi level is omitted from the depletion region because the device is no longer in equilibrium and a single level cannot be used to describe the carrier concentrations in this region.

- The levels labelled EFn and EFp occupying the former position of the Fermi level in the quasineutral regions, are actually majority-carrier quasi-Fermi levels.

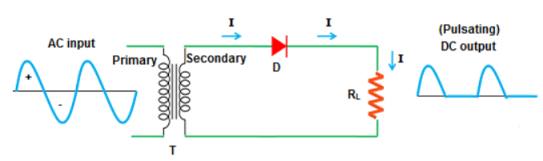

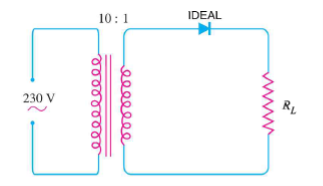

1.5.1 Half Wave Rectification

- It is the simplest form of the rectifier. Here, a single diode is used.

- It consists of an AC source, transformer (step-down), diode, and resistor (load).

- The diode is placed between the transformer and resistor (load).

Figure 26: Half Wave Rectifier

Current

Current

Diode

Diode

Load resistor

Load resistor

+=Positive half cycle

-=Negative half cycle

Operation:

- It allows only half cycle and blocks the other half cycle.

- When it allows positive half cycles and blocks negative half cycles, it is called a positive half wave rectifier. The output DC current or DC signal produced by a positive half wave rectifier is a series of positive half cycles or positive sinusoidal pulses.

- When it allows electric current during the negative half-cycle of input AC signal and blocks electric current during the positive half-cycle of the input AC signal.

- A negative half wave rectifier produces a series of negative sinusoidal pulses.

- For an ideal diode, the positive half cycle or negative half cycle at the output is exactly same.

Characteristics of half wave rectifier

Ripple factor

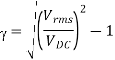

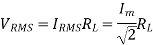

The ripple factor is given as

Finally, we get

γ = 1.21

Hence, the DC voltage is 121% of the DC magnitude.

DC current

The DC current is given by,

Where,

Imax = maximum DC load current

Output DC voltage (VDC)

The output DC voltage is given by,

Where, VSmax = Maximum secondary voltage

Rectifier efficiency

It is defined as the ratio of output DC power to the input AC power.

The rectifier efficiency of a half wave rectifier is 40.6%

Root mean square (RMS)

The root mean square (RMS) value of load current in a half wave rectifier is

The root mean square (RMS) value of output load voltage in a half wave rectifier is

Form factor

It is defined as the ratio of RMS value to the DC value given by,

F.F = RMS value / DC value

The form factor of a half wave rectifier is F.F = 1.57

Advantages:

- Very few component

- Ts are used. So, the cost is very low.

- Easy to construct

Disadvantages:

- Loss of power

- Pulsating direct current

- Produces low output voltage.

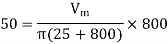

Example: A half-wave rectifier is used to supply 50V d.c. To a resistive load of 800 Ω. The diode has a resistance of 25 Ω. Calculate a.c. Voltage required.

Solution:

Output d.c. Voltage

Diode resistance

Load resistance

Let  be the maximum value of a.c. Voltage required

be the maximum value of a.c. Voltage required

Hence a.c. Voltage of maximum value 162 V is required

Example: In a half-wave rectifier applied input a.c. Power is 100 Watts. The d.c. Output power obtained is 40 watts. (i) What is the rectification efficiency? (ii) What happens to remaining 60 watts?

Solution:

(i) Rectification efficiency = (d.c. output power / a.c. Input power) 100 = 40%

100 = 40%

(ii) 40% efficiency of rectification does not mean that 60% of power is lost in the rectifier circuit. In fact, a crystal diode consumes little power due to its small internal resistance.

The 100 Watts a.c. Power consist of 50 Watts positive cycle and 50 Watts negative cycle. However, negative cycle is not of any use in half wave rectifier. Thus

Power Efficiency =(40/50)  100 = 80%

100 = 80%

Rectification efficiency is 40% and Power Efficiency is 80%.

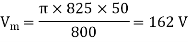

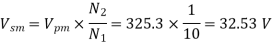

Example: In a half-wave rectifier applied input a.c. Voltage supplied is 230 V transformer ratio is 10:1. Find (i) The d.c. output voltage (ii) Peak inverse voltage. Assume the diode is ideal

Solution:

Primary to secondary turns = N1 /N2 = 10

R.M.S. Primary Voltage = 230V

Max. Primary Voltage Vpm =

R.M.S. Primary Voltage =

R.M.S. Primary Voltage =

230 = 325.3 V

230 = 325.3 V

Max. Secondary Voltage =

(i)

(ii) During negative half cycle of a.c. Supply. Diode does not conduct. Max. Secondary Voltage across diode =

Peak inverse voltage = 32.53 V

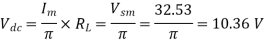

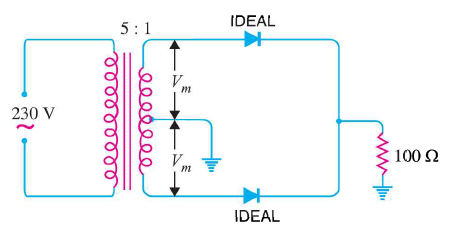

1.5.2 Full Wave Rectification

Types on the basis of construction:

- Center-taped transformer

It consists of two power diodes connected to a single load resistance (RL) and each diode supply current to the load one by one. When point A of the transformer becomes positive, diode D1 conducts in the forward direction.

When point B becomes positive (for the negative half of the cycle) with respect to point C, diode D2 conducts and the current starts flowing through resistor R is in the same direction for both half-cycles.

As the output voltage across the resistor R is the sum of the two waveforms combined, this type of circuit is also called as a “bi-phase” circuit.

The spaces present between the frequency response of each half-wave developed by each diode is now being filled in by the other therefore, the average DC output voltage across the load resistor becomes double that of the single half-wave rectifier circuit.

Figure 27 : Center-taped

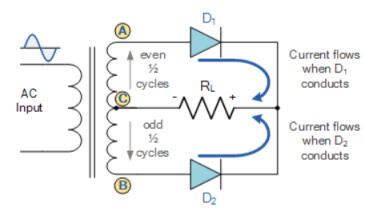

2. Bridge Rectifier

It uses four individual rectifying diodes which are connected in a closed loop called “bridge” configuration to produce the desired output.

It does not require a special centre tapped transformer, hence reducing its size and cost. The single secondary winding is connected one side to the diode bridge network and the other side to the load.

The four diodes D1 to D4 are arranged in “series pairs” and only two diodes conduct current during each half cycle.

During the positive half cycle, diodes D1 and D2 conduct in series while diodes D3 and D4 are reverse biased producing current through the load.

During the negative half cycle, diodes D3 and D4 conduct in series and diodes D1 and D2 are switched “OFF” as they become reverse biased producing current through the load.

During each half cycle the current flows through two diodes instead of just one. The ripple frequency is now twice the supply frequency.

Figure 28: Bridge Rectifier

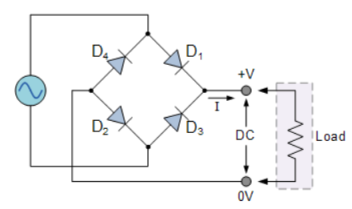

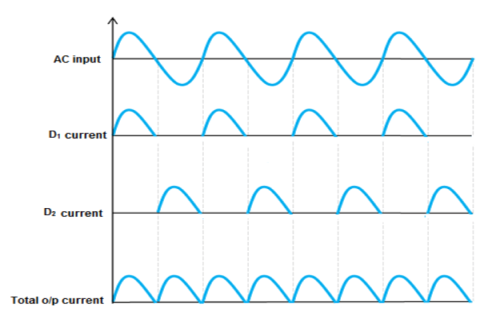

Output Waveform:

Figure 29 : Output Waveform

Characteristics of full wave rectifier

Ripple factor

The ripple factor is given by

Finally, we get γ = 0.48

Rectifier efficiency

It is defined as the ratio of DC output power to the AC input power.

It can be mathematically written as

η = output PDC / input PAC

The rectifier efficiency of a full wave rectifier is 81.2%.

Peak inverse voltage (PIV)

It is the maximum voltage a diode can withstand in the reverse bias condition.

The peak inverse voltage (PIV) = 2Vsmax

DC output current

The current produced by D1 is Imax / π and the current produced by D2 is Imax / π.

So, the output current IDC = 2Imax / π

Where, Imax = maximum DC load current

DC output voltage

The DC output voltage appeared at the load resistor RL is given as

VDC = 2Vmax /π

Where,

Vmax = maximum secondary voltage

Root mean square (RMS) value of load current IRMS

The root mean square (RMS) value of load current in a full wave rectifier is

The root mean square (RMS) value of output load voltage in a full wave rectifier is

Form factor

It is the ratio of RMS value of current to the DC output current

F.F = RMS value of current / DC output current

The form factor of a full wave rectifier is F.F = 1.11

Advantages:

- High rectifier efficiency

- Low power loss

- Low ripples

- It has fewer ripples than the half wave rectifier.

Disadvantages:

- High cost

- The center tapped transformers are expensive and occupy a large space.

Example: A full-wave rectifier uses two diodes, the internal resistance of each diode may be assumed constant at 20 Ω. The transformer r.m.s. Secondary voltage from center tap to each end of secondary is 50 V and load resistance is 980 Ω. Find: (i) the mean load current (ii) the r.m.s. value of load current.

Solution:

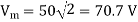

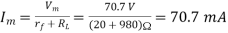

Max a.c. Voltage

Max. Load current

(i) Mean load current

(ii) R.M.S value of load current is

Example: In a center tap full-wave rectifier is shown in figure. Find (i) The d.c. Output voltage (ii) Peak inverse voltage (iii) Rectification efficiency. Assume the diode is ideal

Solution:

Primary to secondary turns = N1 /N2 = 5

R.M.S. Primary Voltage = 230V

R.M.S. Secondary Voltage = R.M.S. Primary Voltage  1/5 =

1/5 =  V

V

Max. Voltage across secondary =46

=

=  V

V

Max. Voltage across half secondary windings = Vm = 65/2 =  V

V

(i) Average Current Output

d.c. Output Voltage

(ii) Peak inverse voltage = 65V

(iii) Rectification efficiency =

Since rf =0

Thus Rectification efficiency = 81.2

1.5.3 L and C Filters

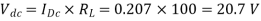

Here, inductor L is in series and shunt capacitor C is connected with load.

The choke (L) i.e. inductor allows the dc component to pass through it because its dc resistance R is very small.

It acts as open circuit and the capacitive reactance Xc is very high for dc.

All dc current that passes through dc output voltage is obtained.

The inductive reactance XL = 2pfL is high for ac components.

Therefore, the ripples are reduced.

Figure 30: L and C Filters

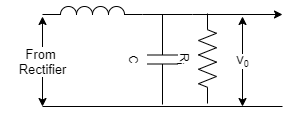

Waveform:

Figure 31: Waveform

Advantages:

- In choke input filter, current flows continuously. Therefore, the transformer is used more efficiently.

- Ripple content at the output is low.

- It is less dependent on the load current.

- DC voltage drop across L is much smaller because its de resistance R is very small.

Disadvantages:

- Large size and weight of inductors,

- More cost,

- External hold is produced by inductor.

Key Takeaways

- It allows only half cycle and blocks the other half cycle.

- When it allows positive half cycles and blocks negative half cycles, it is called a positive half wave rectifier and vice-versa.

- The process of converting the AC current into DC current is called rectification.

- When an additional wire is connected across the exact middle of the secondary winding of a transformer, it is known as a center tapped transformer.

- Bridge rectifier uses four individual rectifying diodes connected in a closed loop “bridge” configuration to produce the desired output.

- The inductive reactance XL = 2pfL is high for ac components.

- Inductor L is in series and shunt capacitor C is connected with load.

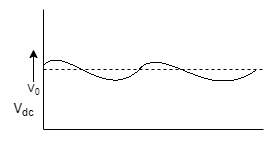

1.6.1 Zener Diode

The satisfactory explanation of this breakdown of the junction was first given by the American scientist C. Zener. A zener diode is a special type of diode that is designed to operate in the reverse breakdown region.

An ordinary diode operated in this region will usually be destroyed due to excessive current. This is not the case for the zener diode.

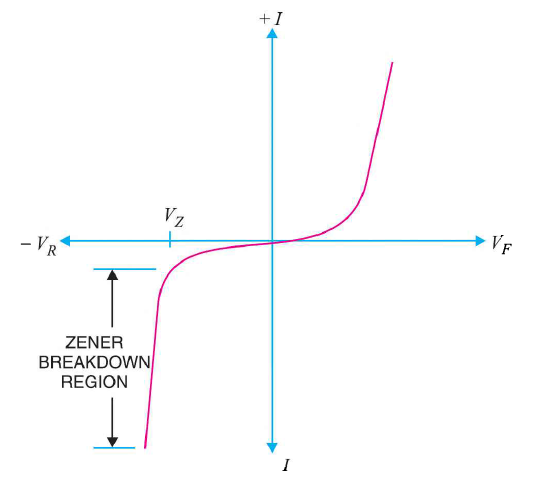

It has already been discussed that when the reverse bias on a crystal diode is increased, a critical voltage, called breakdown voltage is reached where the reverse current increases sharply to a high value. The breakdown region is the knee of the reverse characteristic as shown in Figure 32.

The breakdown voltage is sometimes called zener voltage and the sudden increase in current is known as zener current.

The breakdown or zener voltage depends upon the amount of doping. If the diode is heavily doped, depletion layer will be thin and consequently the breakdown of the junction will occur at a lower reverse voltage.

On the other hand, a lightly doped diode has a higher breakdown voltage. When an ordinary crystal diode is properly doped so that it has a sharp breakdown voltage, it is called a zener diode. A properly doped crystal diode which has a sharp breakdown voltage is known as a zener diode.

Figure 32shows the symbol of a zener diode. It may be seen that it is just like an ordinal, diode except that the bar is turned into z-shape.

Figure 32: Symbol of a Zener diode

Figure 33: I-V characteristics of zener diode

As the curve reveals, two things happen when Vz is reached:

- The diode current increases rapidly.

- The reverse voltage Vz across the diode remains almost constant.

The following points may be noted

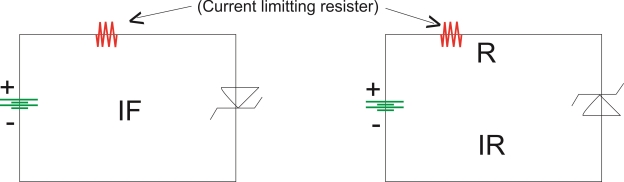

(i) A zener diode is like an ordinary diode except that it is properly doped so as to have a sharp breakdown voltage.

(ii) A zener diode is always reverse connected i.e. it is always reverse biased.

(iii) A zener diode has sharp breakdown voltage, called zener voltage Vz.

(iv) When forward biased, its characteristics are just those of ordinary PN junction diode.

(v) The zener diode is not immediately burnt just because it has entered the breakdown region. As long as the external circuit connected to the diode limits the diode current to less than burn out value, the diode will not burn out.

In other words, the zener diode operated in this region will have a relatively constant voltage across it, regardless of the value of current through the device. This permits the zener diode to be used as a voltage regulator or voltage stabiliser.

- Zener diode is a special type of p-n junction semiconductor diode. In this diode, the reverse breakdown voltage is adjusted precisely between 3 V to 200 V.

- Its applications are based on this principle hence Zener diode is called as a breakdown diode.

- The doping level of the imparity added to manufacture the Zener diode is controlled in order to adjust the precise value of breakdown voltage.

Principle of Operation:

A Zener diode can be forward biased or reverses biased. Its operation in the forward biased mode is same as that of a p-n junction diode but its operation in the reverse biased mode is sustainably different.

Figure 34: Zener diode

Figure 35: Zener diode

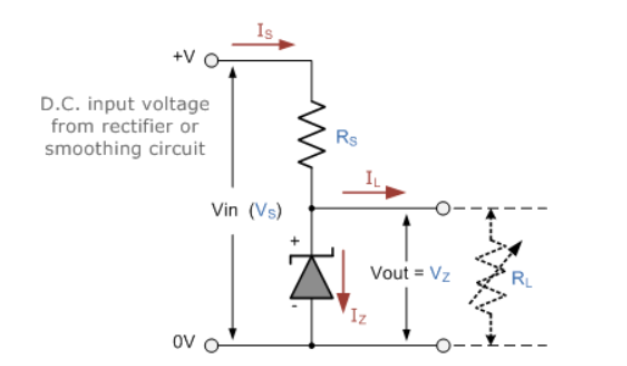

- The resistor, RS is connected in series with the Zener diode to limit the current flow through the diode with the voltage source, VS being connected across the combination. The stabilised output voltage Vout is taken from across the Zener diode.

- The Zener diode is connected with its cathode terminal connected to the positive rail of the DC supply so it is reverse biased and will be operating in its breakdown condition. Resistor RS is selected so to limit the maximum current flowing in the circuit.

- The load is connected in parallel with the Zener diode, so the voltage across RL is always the same as the Zener voltage, (VR = VZ).

- There is a minimum Zener current for which the stabilisation of the voltage is effective, and the Zener current must stay within the value operating under load within its breakdown region at all times.

- The upper limit of current is of course dependent upon the power rating of the device. The supply voltage VS must be greater than VZ.

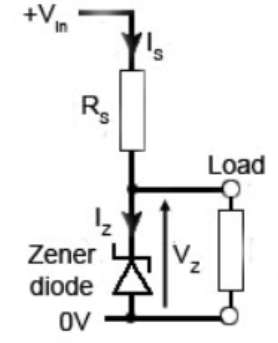

- A Zener diode is always operated in its reverse biased condition. As such a simple voltage regulator circuit can be designed using a Zener diode to maintain a constant DC output voltage across the load despite variations in the input voltage or changes in the load current.

- The Zener voltage regulator consists of a current limiting resistor RS connected in series with the input voltage VS with the Zener diode connected in parallel with the load RL in this reverse biased condition.

- The stabilised output voltage is always selected to be the same as the breakdown voltage VZ of the diode.

Example: A 5.0V stabilised power supply is required to be produced from a 12V DC power supply input source. The maximum power rating PZ of the Zener diode is 2W. Using the Zener regulator circuit above calculate:

a). The maximum current flowing through the Zener diode.

Maximum current = Watts/ Voltage = 2w/ 5V = 400mA

b). The minimum value of the series resistor, RS

Rs = Vs – Vz/ Iz = 2 – 5 / 400mA = 17.5 Ω

c). The load current IL if a load resistor of 1kΩ is connected across the Zener diode.

IL = Vz / RL = 5v/ 1000Ω = 5mA

d). The Zener current IZ at full load.

IZ = Is – IL = 400 mA – 5mA = 395mA

1.6.2 Voltage Regulators

They are used more due to less cost and are effective. Zener diode is used for voltage regulation in the circuit. At maximum load current the shunt regulator draws virtually no current and at minimum load current, the shunt voltage regulator passes the full current. Zener diode a shunt regulator is shown below.

Figure 36: Voltage Regulators

There is voltage drop across the resistor in series to the source. The voltage across the Zener diode is maintained irrespective of the change in current. It takes up the current variations required to ensure the correct drop across the series resistor. In this way it shunts sufficient current to maintain the voltage across its terminals and hence the load.

It is an open loop connection. Shunt voltage regulators are not particularly effective or efficient in high current situations. The simple Zener diode voltage regulator, when used as a low current voltage reference is widely used, and its inefficiency can be tolerated in view of the low current.

Key Takeaways

- A zener diode is a special type of diode that is designed to operate in the reverse breakdown region.

- The breakdown region is the knee of the reverse characteristic

- The breakdown voltage is sometimes called zener voltage and the sudden increase in current is known as zener current.

- The breakdown or zener voltage depends upon the amount of doping.

- Because of its special characteristics zener diode used as voltage stabiliser

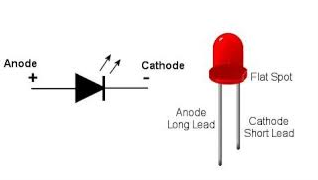

LED or Light emitting diode

Light emitting diode is a pn junction device. It is always operated in forward biased condition. LED converts electrical energy into light energy.

Figure 37: LED

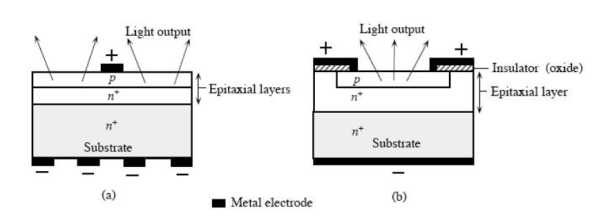

Device Structure:

The LED structure plays a crucial role in emitting light from the LED surface. The LEDs are structured to ensure most of the recombination takes place on the surface by the following two ways.

- By increasing the doping concentration of the substrate, so that additional free minority charge carriers electrons move to the top, recombine and emit light at the surface.

- By increasing the diffusion length L =√Dτ, where D is the diffusion coefficient and τ is the carrier life time.

But when increased beyond a critical length there is a chance of reabsorption of the photons into the device. The LED has to be structured so that the photons generated from the device are emitted without being reabsorbed.

Figure 38: A schematic illustration of typical planar surface emitting LED devices. (a) p-layer grown epitaxially on an n+ substrate. (b) First n+ is epitaxially grown and then p region is formed by dopant diffusion into the epitaxial layer.

One solution is to make the p layer on the top thin, enough to create a depletion layer. Following picture shows the layered structure. There are different ways to structure the dome for efficient emitting

LEDs are usually built on an n-type substrate, with an electrode attached to the p-type layer deposited on its surface. P-type substrates, while less common, occur as well. Many commercial LEDs, especially GaN/InGaN, also use sapphire substrate.

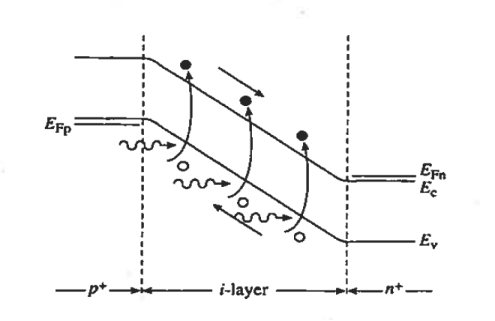

In the fabrication of LED’s direct band gap semiconductors like GaP, GaAsP are used. In direct band gap semiconductors most of the energy is emitted in the form of light when hole and electron recombination takes place.

When an LED is forward biased the electrons and holes move in towards the junction and recombination takes place. As a result of recombination the electrons lying in the conduction band of an n- region fall into the holes lying in the valence band of a p –region. The difference of energy in the valence band and conduction band is radiated in the form of light energy. Here their excess energy is transferred to the emitted photon. The brightness of emitted light is directly proportional to the forward bias current.

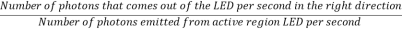

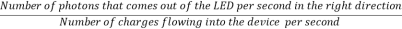

Figures of Merit

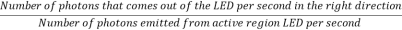

A very important metric of an LED is the external quantum efficiency ηext. It quantifies the efficiency of the conversion of electrical energy into emitted optical energy.

Not all the photons emitted from the active region of an LED make it out of the device. Some are reabsorbed, some go in the wrong direction, some are reflected back. The light extraction efficiency of a LED is,

ηextraction

The external quantum efficiency ext of a LED is,

ηextraction

It is defined as the light output divided by the electrical input power. It is also defined as the product of Internal radiative efficiency and Extraction efficiency. ηext = Pout(optical) / IV

For indirect bandgap semiconductors ηext is generally less than 1%, whereas for a direct band gap material it could be substantial.

ηint = rate of radiation recombination/ Total recombination

The internal efficiency is a function of the quality of the material and the structure and composition of the layer.

LED materials

LEDs are comprised of compound semiconductor materials, which are made up of elements from group III and group V of the periodic table (these are known as III-V materials). Examples of III-V materials commonly used to make LEDs are gallium arsenide (GaAs) and gallium phosphide (GaP).

Ternary alloys based on alloying GaAs and GaP which are denoted by GaAs1-yPy. InGaAlP is an example of a quarternary (four elements) III-V alloy with a direct band gap. The LEDs realized using two differently doped semiconductors that are the same material is called a homojunction. When they are realized using different bandgap materials they are called a heterostructure device. A heterostructure LED is brighter than a homoJunction LED.

The main semiconductor materials used to manufacture LEDs are:

- Indium gallium nitride (InGaN): blue, green and ultraviolet high-brightness LEDs

- Aluminum gallium indium phosphide (AlGaInP): yellow, orange and red high-brightness LEDs

- Aluminum gallium arsenide (AlGaAs): red and infrared LEDs

- Gallium phosphide (GaP): yellow and green LEDs

Characteristics of LED

LEDs are solid-state devices. The advantages are:

1) Light Generated by LED is Directional

2) LED can Generate Different Light Color

3) Temperature will Affect LED Efficacy

4) Low Energy Consumption

5) Long Life

The usage of LED is advantageous as it consumes less power and produces less heat. LEDs last longer than incandescent lamps.

Colour of the Emitted Light

Material Use Color of Emitted Light

i)Gallium Arsenide (GOAS) In fared (IR)

Ii) GaASP(gallium arsenide Red or Yellow

Phosphide)

Iii) Gallium phosphide (GAP) Red or Green

Applications LEDs are used in

- For instrument display

- In calculators

- Digital clocks

- For indicating power ON/ OFF

- For optical switching application

- In optical communication system

- Medical devices

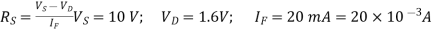

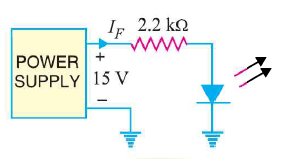

Example: What value of series resistor is required to limit the current through LED 20mA. Forward voltage drop is 1.6V when 10V Supply is connected.

Solution:

Series resistor

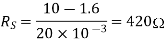

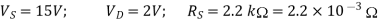

Example: What value current through LED in following figure. Forward voltage drop is 2V.

Solution:

Current through LED,

Here

Key Takeaways

- Light emitting diode is a pn junction device. It is always operated in forward biased condition. LED converts electrical energy into light energy.

- When an LED is forward biased the electrons and holes move in towards the junction and recombination takes place.

- The light extraction efficiency of a LED is,

ηextraction

- LEDs are comprised of compound semiconductor materials, which are made up of elements from group III and group V of the periodic table (these are known as III-V materials). Examples of III-V materials commonly used to make LEDs are gallium arsenide (GaAs) and gallium phosphide (GaP).

P-I-N AND AVALANCHE

p-i-n Diode

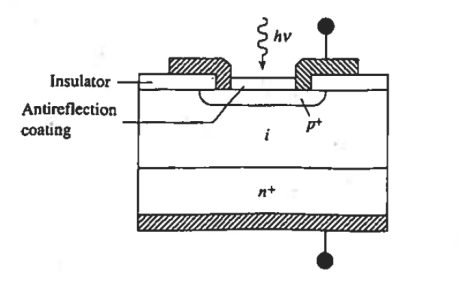

In p-i-n diode an “intrinsic” (actually lightly doped) I region is sandwiched between heavily doped p- and n-regions. It is p-i-n diode is a three-region structure

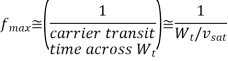

In the p-i-n photodiode shown schematically in Figure 39. An opening is made in the surface metallization to admit light, the top semiconductor region is kept very thin no minimize absorption in the region and the i-layer width is specifically tailored so achieve the desired response characteristics. Because of the low doping the i-layer is totally depleted under zero bias or becomes depleted at small reverse biases.

Furthermore, the heavy doping of the outer p and n regions causes the depletion widths in these regions to be very narrow. Thus as pictured in a Figure 40.

The depletion width inside the device is effectively equal to the i-layer width independent of the applied reverse bias. The energy bands (in Figure 40) are linear functions of position and the ξ-field is approximately constant in the i-region because of the low semiconductor doping.

Figure 39: p-i-n photodiode Cross section.

Figure 40: p-i-n photodiode Reverse bias energy band diagram.

It should also be noted than the heavy doping of the outer p and n regions causes the depletion means the minority carriers diffusion lengths in these regions will be relatively small. As a result, the greater part of the photocurrent flowing in a p-i-n photodiode arises from carriers generated in the central depletion region.

Operational advantages of the p-i-n photodiode that have made it one of the most widely employed photodetectors stem, from the existences and tailor ability of the i-region.

For one, the diode con be optimized for response at a given wavelength by making the layer width equal to the inverse of the absorption coefficient (1/ ) of the specified wavelength Second, with one of the most photocurrent arising from light absorption to the i-region. Frequency response is greatly enhanced over that of a pn junction photodiode. The large ‘ξ-field is the depleted i-region leads to the rapid collection of photo generated carriers and a maximum frequency response.

) of the specified wavelength Second, with one of the most photocurrent arising from light absorption to the i-region. Frequency response is greatly enhanced over that of a pn junction photodiode. The large ‘ξ-field is the depleted i-region leads to the rapid collection of photo generated carriers and a maximum frequency response.

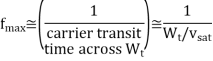

Where WI is the width of the I region

Vsat is the saturation drift velocity

If WI = 5 then fmax =20GHz

then fmax =20GHz

The WI cannot be made arbitrary small to improve frequency.

The RC time constant associated with the internal series resistance (Rs)and the junction capacitance (CJ = Ks 0A/ WI) increases with decreasing WI and eventually limits the response time of the diode.

0A/ WI) increases with decreasing WI and eventually limits the response time of the diode.

The excellent frequency response of the p-i-n photodiode makes it important for use as the photo detector in optical fiber telecommunication.

Avalanche Photodiode

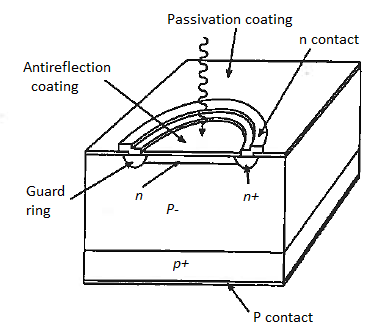

Avalanche Photodiode are specially constructed p-i-n, pn, or even metal-semiconductor photodiodes that are operated near the avalanche breakdown point. A standard Si avalanche photodiode configuration is shown in figure.

One obvious special structural feature is the guard ring around the junction periphery. As noted in junction curvature leads to early breakdown about the junction periphery. The guard ring minimization of defect creation during device processing is also required to achieve uniform breakdown across the face of the junction. The primary advantage of the avalanche photodiode is a photo-signal gain leading to improvement in the signal-to-noise (S/N) ratio.

Figure 41: Avalanche Photodiode

As a general rule, amplification of signals is accompanied by amplification of the noise and added noise from the amplifier. Signal pain therefore typically loads to a reduction in the S/N ratio. Inside an avalanche photodiode, however, avalanche multiplication amplifies the photo-signal without amplifying the typically dominant receiver circuit noise. Thus there is an improvement in the S/N ratio until the added avalanche-related noise becomes comparable to the circuit noise.

Avalanche photodiodes made from lnGaAs on lnP and from Ge provide alternatives to the p-i-n photodiode for use in fiber optic telecommunication.

Key Takeaways

- In p-i-n diode an “intrinsic” (actually lightly doped) I region is sandwiched between heavily doped p- and n-regions. It is p-i-n diode is a three-region structure

- A maximum frequency response is given by

- Avalanche Photodiode are specially constructed p-i-n, pn, or even metal-semiconductor photodiodes that are operated near the avalanche breakdown point.

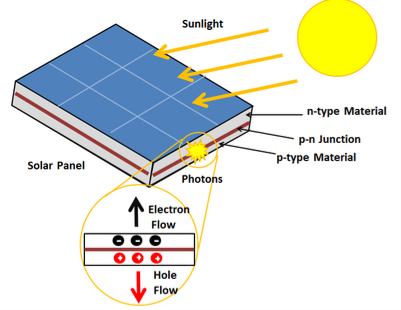

A solar cell or photo-voltaic cell is an electronic device that directly converts sun’s energy into electricity. When sunlight falls on a solar cell, it produces both a current and a voltage to produce electric power.

Sunlight, which is composed of photons, radiates from the sun. When photons hit the silicon atoms of the solar cell, they transfer their energy to lose electrons; and then, these high-energy electron flow to an external circuit.

Figure 42: Solar Cell

The solar cell is composed of two layers which are struck together. The first layer is loaded with electrons, so these electrons are ready to jump from the first layer to the second layer. The second layer has some electrons taken away, and therefore, it is ready to take more electrons.

The advantages of solar cells are that, there is no fuel supply and cost problem. These are very dependable and require little maintenance.

A key issue with solar cells is conversion efficiency—convening the maximum amount of available solar energy into electrical energy. The higher the efficiency of the cells, the lower the cost and collection area required to achieve a desired electrical output.

A number of factors enter into the overall efficiency exhibited by a cell and involve both material and design considerations. Any discussion of conversion efficiency logically begins with the output from the sun.

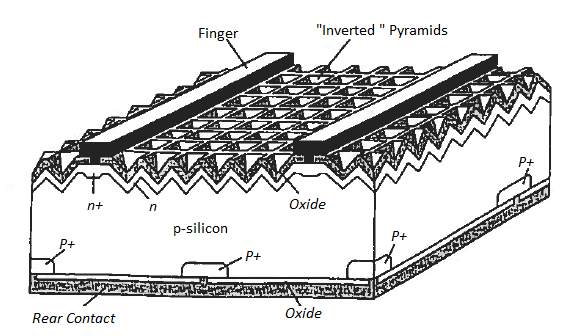

Given a specific semiconductor material, it is the task to design and fabricate the solar cell to minimize further energy losses. In discussing device-related loss mechanisms, we will refer to the high-efficiency Si solar cell pictured in Figure 25.