Unit - 5

IC Logic Families

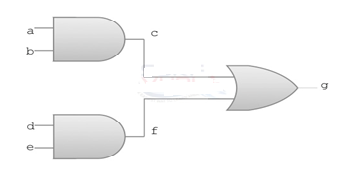

Q1) Write a code for

A1)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity and_or is

port (

a: in std_logic;

b: in std_logic;

d: in std_logic;

e: in std_logic;

g: out std_logic);

end and_or;

architecture and_or_a of and_or is

-- declarative part: empty

begin

g <= (a and b) or (d and e);

end and_or_a;

Q2) Write a code for 4:1 MUX.

A2)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity MUX_SOURCE is

Port (S: in STD_LOGIC_VECTOR (1 downto 0);

I: in STD_LOGIC_VECTOR (3 downto 0);

Y: out STD_LOGIC);

end MUX_SOURCE;

architecture Behavioral of MUX_SOURCE is

begin

process (S, I)

begin

if (S <= "00") then

Y <= I (0);

elsif (S <= "01") then

Y <= I (1);

elsif (S <= "10") then

Y <= I (2);

else

Y <= I (3);

end if;

end process;

end Behavioral;

Q3) Write code for Half Subtractor

A3)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity half_sub is

port (a, b: in std_logic;

dif, bo: out std_logic

);

end half_sub;

architecture sub_arch of half_sub is

begin

dif <= a xor b;

bo <= (not a) and b;

end sub_arch;

Q4) Write a code for full adder.

A4)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity FULLADDER_BEHAVIORAL_SOURCE is

Port (A: in STD_LOGIC_VECTOR (2 downto 0);

O: out STD_LOGIC_VECTOR (1 downto 0));

end FULLADDER_BEHAVIORAL_SOURCE;

architecture Behavioral of FULLADDER_BEHAVIORAL_SOURCE is

begin

process (A)

begin

—for SUM

if (A = “001” or A = “010” or A = “100” or A = “111”) then

O (1) <= ‘1’;

—single inverted commas used for assigning to one bit

else

O (1) < = ‘0’;

end if;

—for CARRY

if (A = “011” or A = “101” or A = “110” or A = “111”) then

O (0) <= ‘1’;

else

O (0) <<= ‘0’;

end if;

end process;

end Behavioral;

Q5) Write a code for JK flip-flop.

A5)

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity jk is

port(

j : in STD_LOGIC;

k : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

q : out STD_LOGIC;

qb : out STD_LOGIC

);

end jk;

architecture jk_flip_flop of jk is

begin

jkff : process (j,k,clk,reset) is

variable m : std_logic := '0';

begin

if (reset='1') then

m := '0';

elsif (rising_edge (clk)) then

if (j/=k) then

m := j;

elsif (j='1' and k='1') then

m := not m;

end if;

end if;

q <= m;

qb <= not m;

end process jkff;

end jk_flip_flop;

Q6) Write a code for RS latch.

A6)

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity SR_Latch is

port(

enable : in STD_LOGIC;

s : in STD_LOGIC;

r : in STD_LOGIC;

reset : in STD_LOGIC;

q : out STD_LOGIC;

qb : out STD_LOGIC );

end SR_Latch;

architecture SR_Latch_arc of SR_Latch is

begin

latch : process (s,r,enable,reset) is

begin

if (reset='1') then

q <= '0';

qb <= '1';

elsif (enable='1') then

if (s/=r) then

q <= s;

qb <= r;

elsif (s='1' and r='1') then

q <= 'Z';

qb <= 'Z';

end if;

end if;

end process latch;

end SR_Latch_arc;

Q7) Write a program for 1-bit comparator

A7)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity comparator_1bit is

Port (A, B: in std_logic;

G, S, E: out std_logic);

end comparator_1bit;

architecture comp_arch of comparator_1bit is

begin

G <= A and (not B);

S <= (not A) and B;

E <= A xnor B;

end comp_arch;

Q8) Write a program for 8-bit comparator

A8)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity comparator_8bit is

Port (A, B: in std_logic_vector (0 to 7);

G, S, E: out std_logic);

end comparator_8bit;

architecture comp_arch of comparator_8bit is

begin

process

begin

if A=B then

G <= ‘0’;

S <= ‘0’;

E <= ‘1’;

elsif A>B then

G <= ‘1’;

S <= ‘0’;

E <= ‘0’;

elsif A<B then

G <= ‘0’;

S <= ‘1’;

E <= ‘0’;

end if;

end process;

end comp_arch;

Q9) Write a program for 3:8 Decoder

A9)

Q10) Write program for 4-bit binary counter

A10) library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity counter is

Port (rst, clk: in std_logic;

o: out std_logic_vector (0 to 3));

end counter;

architecture count_arch of counter is

signal count: std_logic_vector (0 to 3);

begin

process (rst, clk)

begin

if (rst = ‘1’) then count <= “0000”;

elsif (clk ’event and clk = ‘1’) then count <= count + 1;

end if;

end process;

o <= count;

end count_arch;

Q11) Write VHDL code for 4-bit synchronous up/down counter with asynchronous active-low reset

A11) library ieee;

use ieee.std_logic_1164.all;

entity my_bcd_ud_count is

port (clock, resetn, ud: in std_logic;

Q: out integer range 0 to 15);

end my_bcd_ud_count;

architecture bhv of my_bcd_ud_count is

signal Qt: integer range 0 to 15;

begin

process (resetn, clock, ud)

begin

if resetn = '0' then

Qt <= 0;

elsif (clock ‘event and clock='1') then

if ud = '0' then

Qt <= Qt - 1;

else

Qt <= Qt + 1;

end if;

end if;

end process;

Q <= Qt;

end bhv;

Q12) Write VHDL code for Parallel in Parallel Out Shift Register

A12) library ieee;

use ieee.std_logic_1164.all;

entity pipo is

port (

clk: in std_logic;

D: in std_logic_vector (3 downto 0);

Q: out std_logic_vector (3 downto 0)

);

end pipo;

architecture arch of pipo is

begin

process (clk)

begin

if (CLK ‘event and CLK='1') then

Q <= D;

end if;

end process;

end arch;

Q13) Write VHDL Code for Serial In Parallel Out Shift Register

A13) library ieee;

use ieee.std_logic_1164.all;

entity sipo is

port (

clk, clear: in std_logic;

Input_Data: in std_logic;

Q: out std_logic_vector (3 downto 0));

end sipo;

architecture arch of sipo is

begin

process (clk)

begin

if clear = '1' then

Q <= "0000";

elsif (CLK ‘event and CLK='1') then

Q (3 downto 1) <= Q (2 downto 0);

Q (0) <= Input_Data;

end if;

end process;

end arch;

Q14) Write VHDL code for 8-bit register with enable and asynchronous reset

A14) library ieee;

use ieee.std_logic_1164.all;

entity reg8 is port (clock, resetn, E: in std_logic;

D: in std_logic_vector (7 downto 0);

Q: out std_logic_vector (7 downto 0));

end reg8;

architecture bhv of reg8 is

begin

process (resetn, E, clock)

begin

if resetn = '0' then

Q <= (others => '0');

elsif (clock ‘event and clock = '1') then

if E = '1' then

Q <= D;

end if;

end if;

end process;

end bhv;

Q15) Write VHDL code for 8-bit register with enable and asynchronous reset

A15) library ieee;

use ieee.std_logic_1164.all;

entity my_rege is

generic (N: INTEGER: = 4);

port (clock, resetn: in std_logic;

E, sclr: in std_logic;

D: in std_logic_vector (N-1 downto 0);

Q: out std_logic_vector (N-1 downto 0));

end my_rege;

architecture Behavioral of my_rege is

signal Qt: std_logic_vector (N-1 downto 0);

begin

process (resetn, clock)

begin

if resetn = '0' then Qt <= (others => '0');

elsif (clock ‘event and clock = '1') then

if E = '1' then

if sclr='1' then Qt <= (others =>'0');

else Qt <= D;

end if;

end if;

end if;

end process;

Q <= Qt;

end Behavioral;

Q16) Draw the circuit and explain RTL logic family?

A16) The resistor-transistor logic, also termed as RTL, was most popular kind of logic before the invention of IC fabrication technologies.

As its name suggests, RTL circuits mainly consists of resistors and transistors that comprises RTL devices. The basic RTL device is a NOR gate, shown in figure.

Fig: RTL logic

Inputs to the NOR gate shown above are ‘input1’ & ‘input2’. The inputs applied at these terminals represent either logic level HIGH (1) or LOW (0). The logic level LOW is the voltage that drives corresponding transistor in cut-off region, while logic level HIGH drives it into saturation region.

If both the inputs are LOW, then both the transistors are in cut-off i.e., they are turned-off. Thus, voltage Vcc appears at output i.e., HIGH. If either transistor or both of them are applied HIGH input, the voltage Vcc drops across Rc and output is LOW.

RTL family is characterized by poor noise margin, poor fan-out capability, low speed and high-power dissipation. Due to these undesirable characteristics, this family is now obsolete.

Q17) Explain DTL logic family?

A17) The diode-transistor logic, also termed as DTL, replaced RTL family because of greater fan-out capability and more noise margin. As its name suggests, DTL circuits mainly consists of diodes and transistors that comprises DTL devices.

The basic DTL device is a NAND gate, shown aside. Three inputs to the gate are applied through three diodes viz. D1, D2 and D3. The diode will conduct only when corresponding input is LOW.

If any of the diode is conducting i.e., when at least one input is LOW, the voltage at cathode of diode DA is such that it keeps transistor T in cut-off and subsequently, output of transistor is HIGH.

If all inputs are HIGH, all diodes are non-conducting, transistor T is in saturation, and its output is LOW.

Fig: DTL Logic

Due to number of diodes used in this circuit, the speed of the circuit is significantly low. Hence this family of logic gates is modified to transistor-transistor logic i.e., TTL family.