Unit 3

Analysis and synthesis of Combinational logic circuits

Q1) Explain Comparator in detail.

A1)

A comparator is a logic circuit, used to compare the magnitude of two binary numbers.

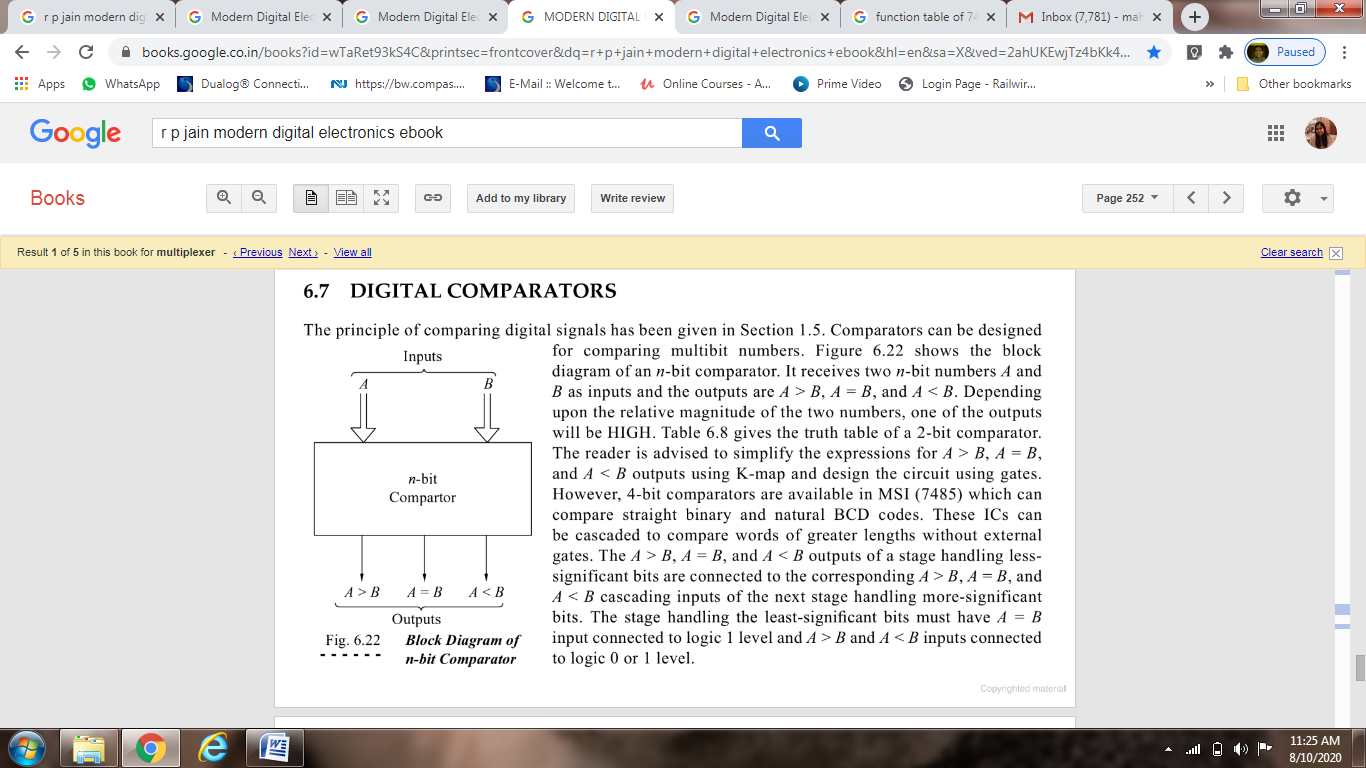

The following figure shows the block diagram of a n-bit comparator.

Fig.1: Comparator

It receives two n-bit numbers A and B as inputs and the outputs are A>B,A=B and A<B. Depending upon the relative magnitude of the two numbers, one of the outputs will be high.

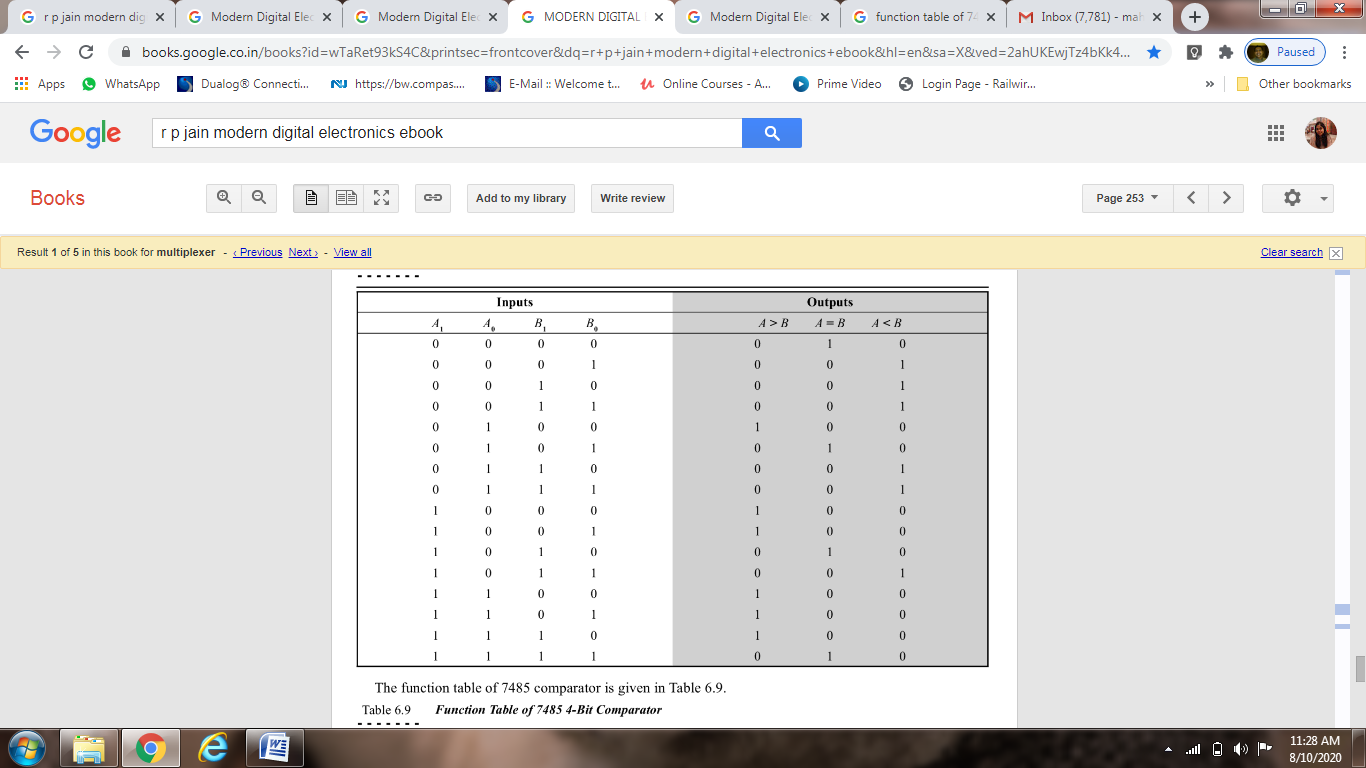

The following is the truth table of a 2-bit comparator.

Q2) Explain Nx1 MUX.

A2)

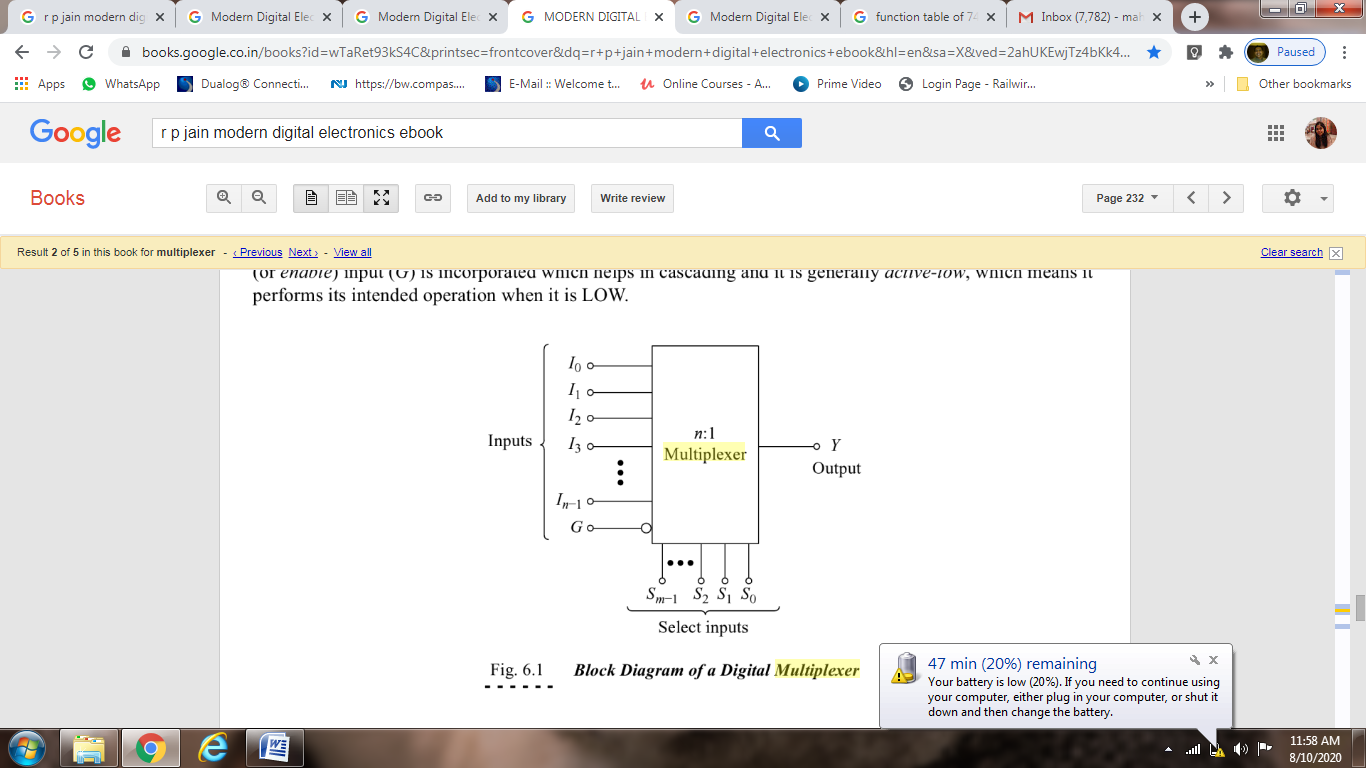

Multiplexing means sharing. A multiplexer (MUX) or data selector is a logic circuit that accepts several data inputs and allows only one of them at a time to get through to the output. The routing of the desired data input to the output is controlled by SELECT lines. Block diagram of a MUX with n inputs and one output is shown below:

Fig.2: Nx1 MUX

For selecting one out of n inputs for connection to the output, a set of m select inputs is required, where 2m =n. Depending upon the digital code applied at the select inputs, one out of the n-data sources is selected and transmitted to a single output channel.

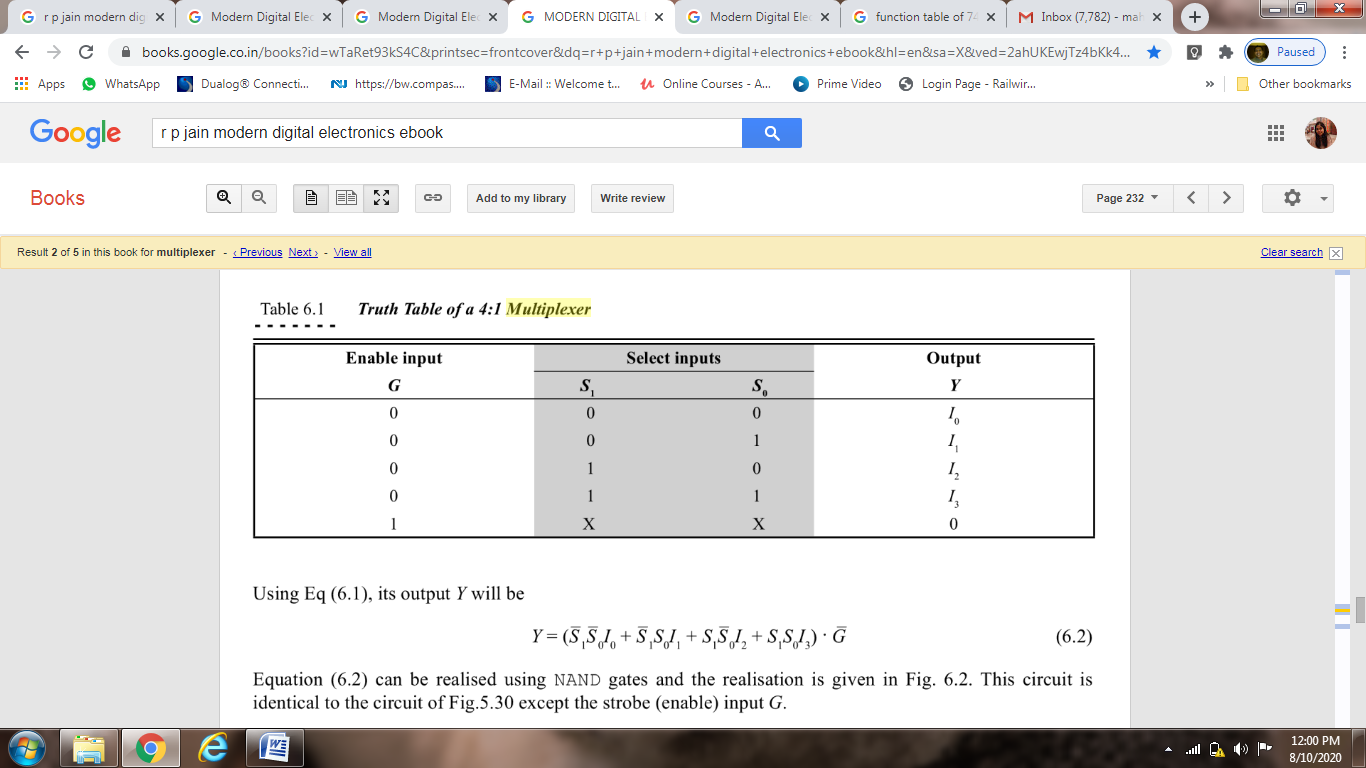

Normally, an ENABLE input G is incorporated which helps in cascading and is generally active-low. The following is the truth table of a 4:1 MUX with active low enable input G:

Its output Y can be expressed as:

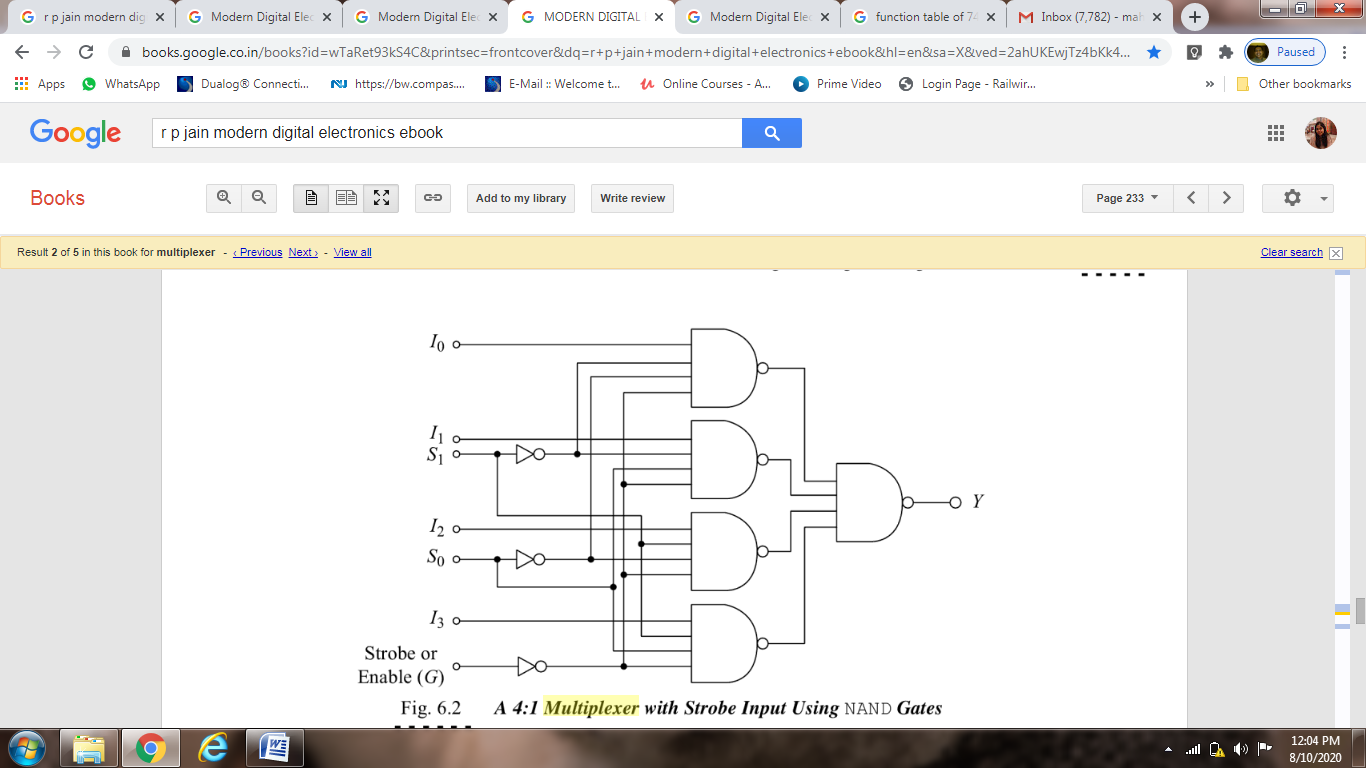

The above equation can be realized using NAND Gates as shown below:

Fig.3: MUX using logic gates

Q3) Explain Encoder.

A3)

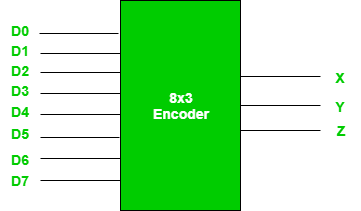

- It is a combinational circuit that converts binary information in the form of a 2N input lines into N output lines, which represent N bit code for the input.

- For simple encoders, only one input line is active at a time.

- For example: Octal to Binary encoder takes 8 input lines and generates 3 output lines.

Fig.4 : 8X3 Encoder (ref. 2)

Truth Table –

D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | X | Y | Z |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

- From the above truth table it is seen that the output is 000 when D0 is active; 001 when D1 is active; 010 when D2 is active and so on.

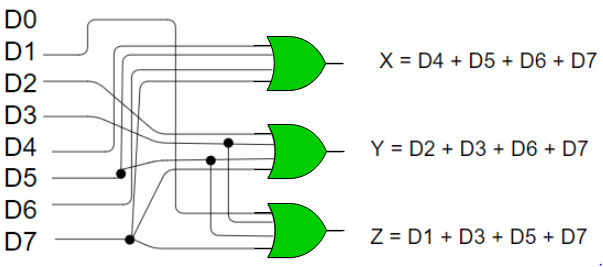

Implementation –

- From the above truth table, the output Z is active when the input octal digit is 1, 3, 5 or 7.

- Y is active when input octal digit is 2, 3, 6 or 7 and X is active when input octal digits 4, 5, 6 or 7.

- Hence, the Boolean functions would be:

X = D4 + D5 + D6 + D7

Y = D2 +D3 + D6 + D7

Z = D1 + D3 + D5 + D7

- Hence, the encoder is realised with OR gates as follows:

Fig: 5 8:3 encoder (ref.2)

- Limitation of the encoder is that only one input is active at a time.

- If more than one input are active, then the output of encoder is undefined.

- For example, if D6 and D3 are both active, then, our output would be 111 which is the output for D7.

- Problem arises when all inputs are 0.

- The encoder gives output 000 which actually is the output for D0. To avoid this, an extra bit is added to the output which is called the valid bit whose value is 0 when all inputs are 0 or 1.

Q4) Explain 7 segment display.

A4)

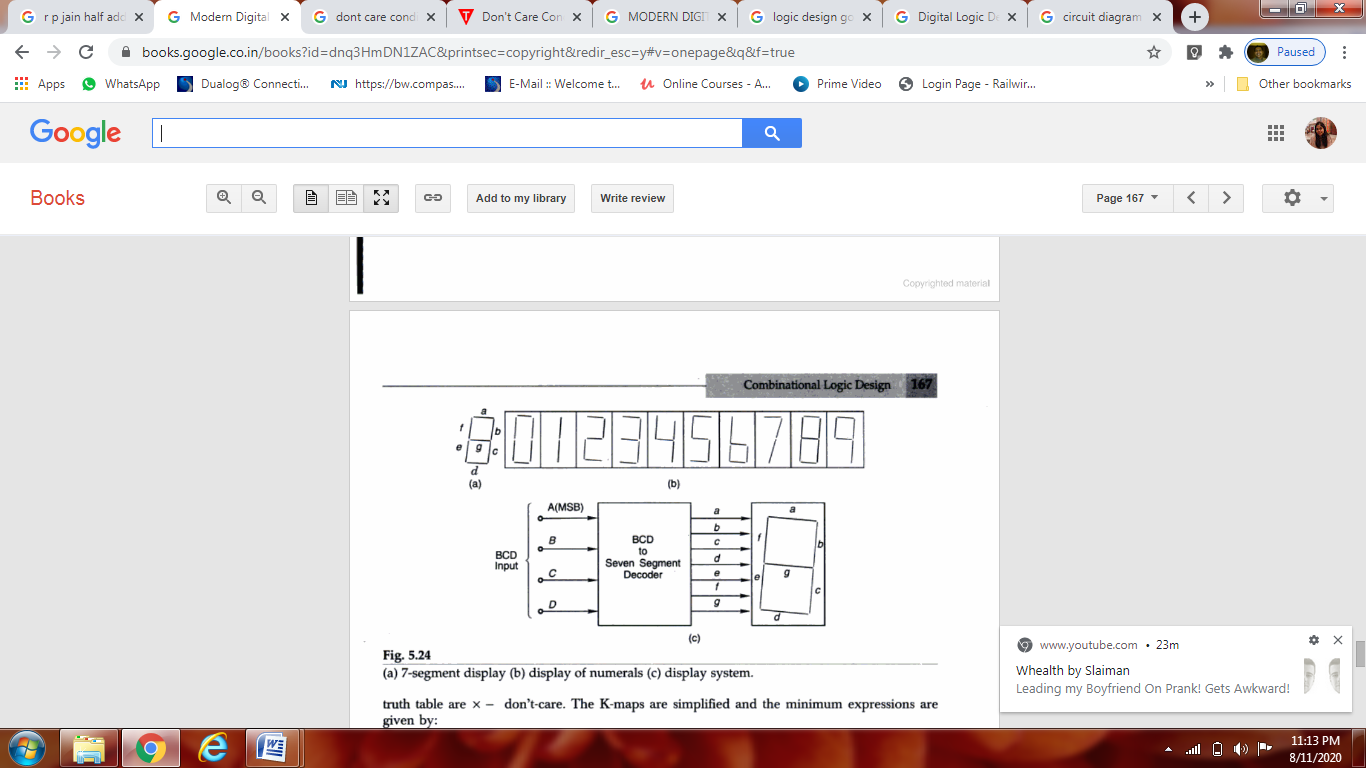

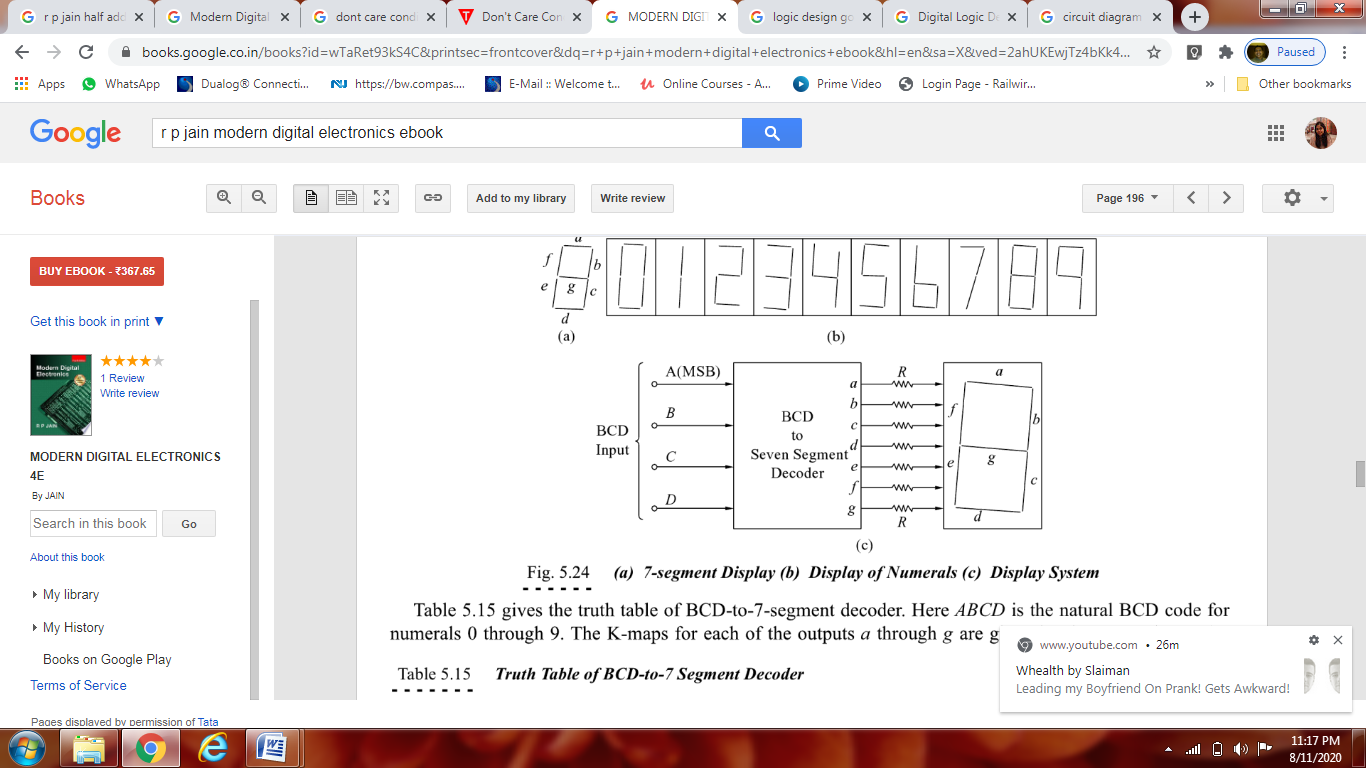

In most practical applications, seven segment displays are used to give a visual indication of the output states of digital IC’s such a decade counters, latches etc. For using this display device, the data has to be converted from some binary code to the code required for the display. Usually, the binary code used is natural BCD.

The following figure shows the display device and the segments which must be illuminated for each of the numerals.

The display system can be connected as follows:

Fig.7: seven segment display

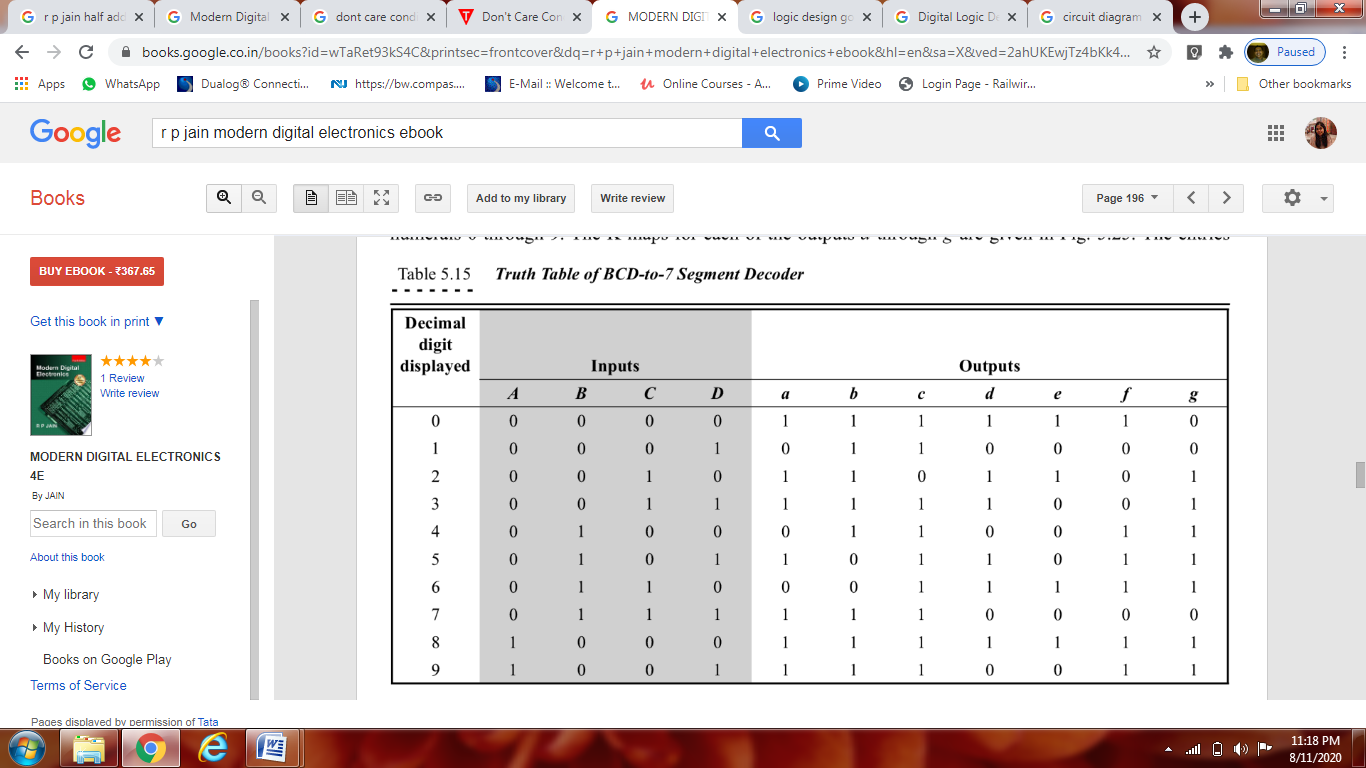

Here, ABCD is the natural BCD code for numerals 0 through 9. Following is the truth table of BCD to 7-segment decoder

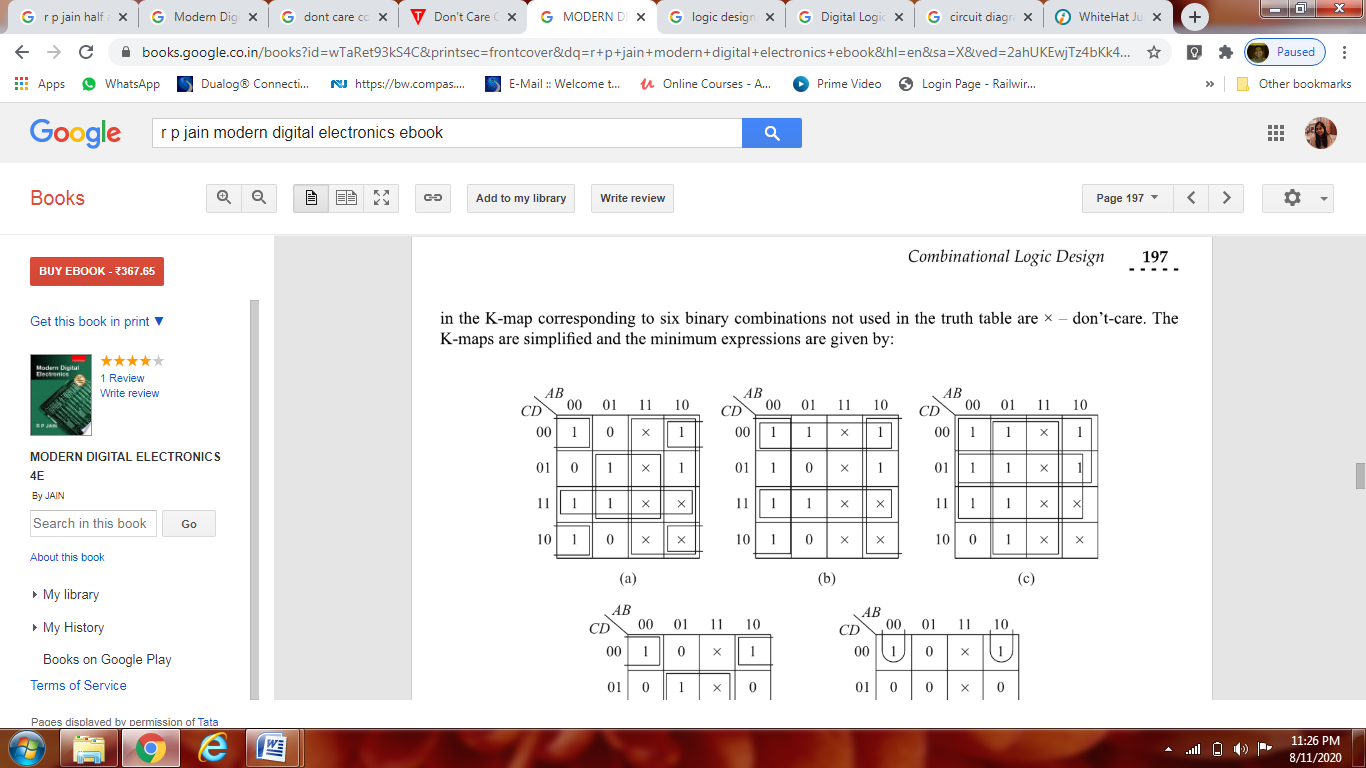

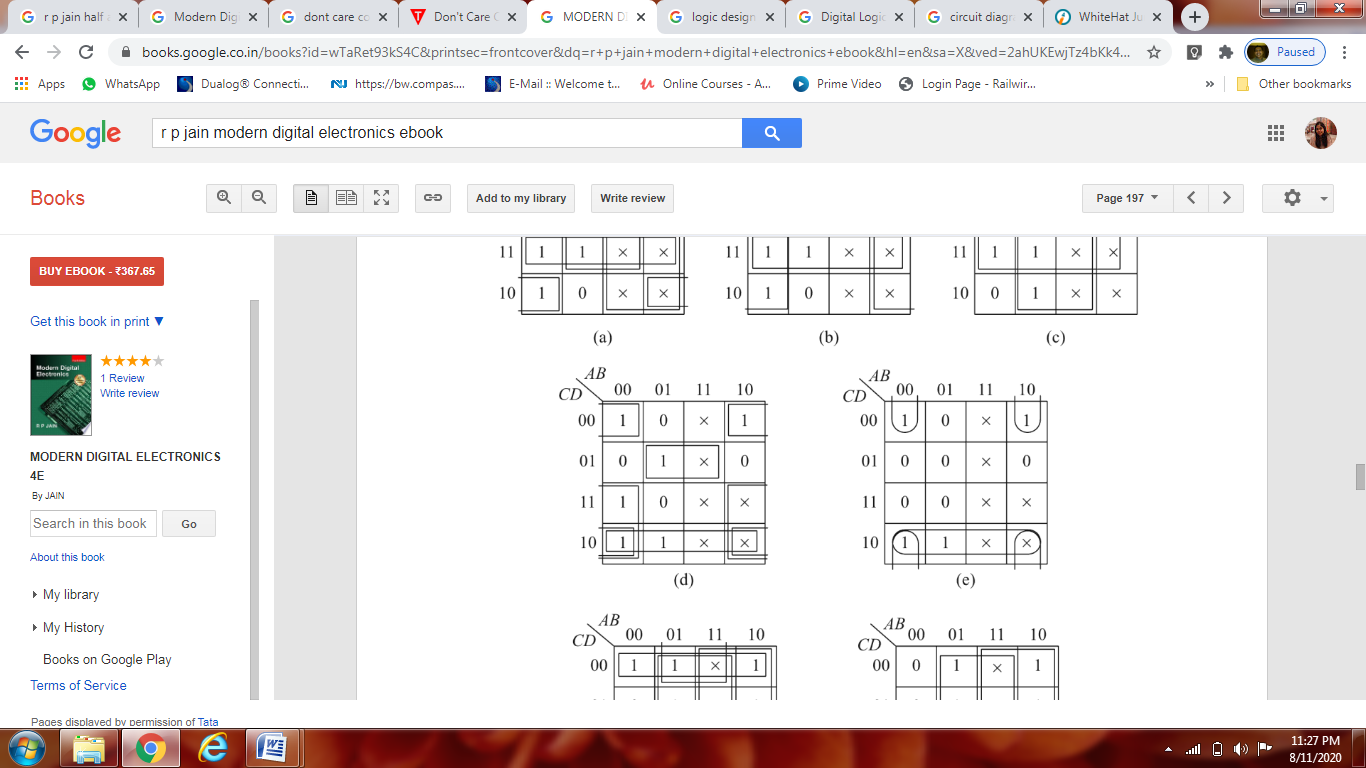

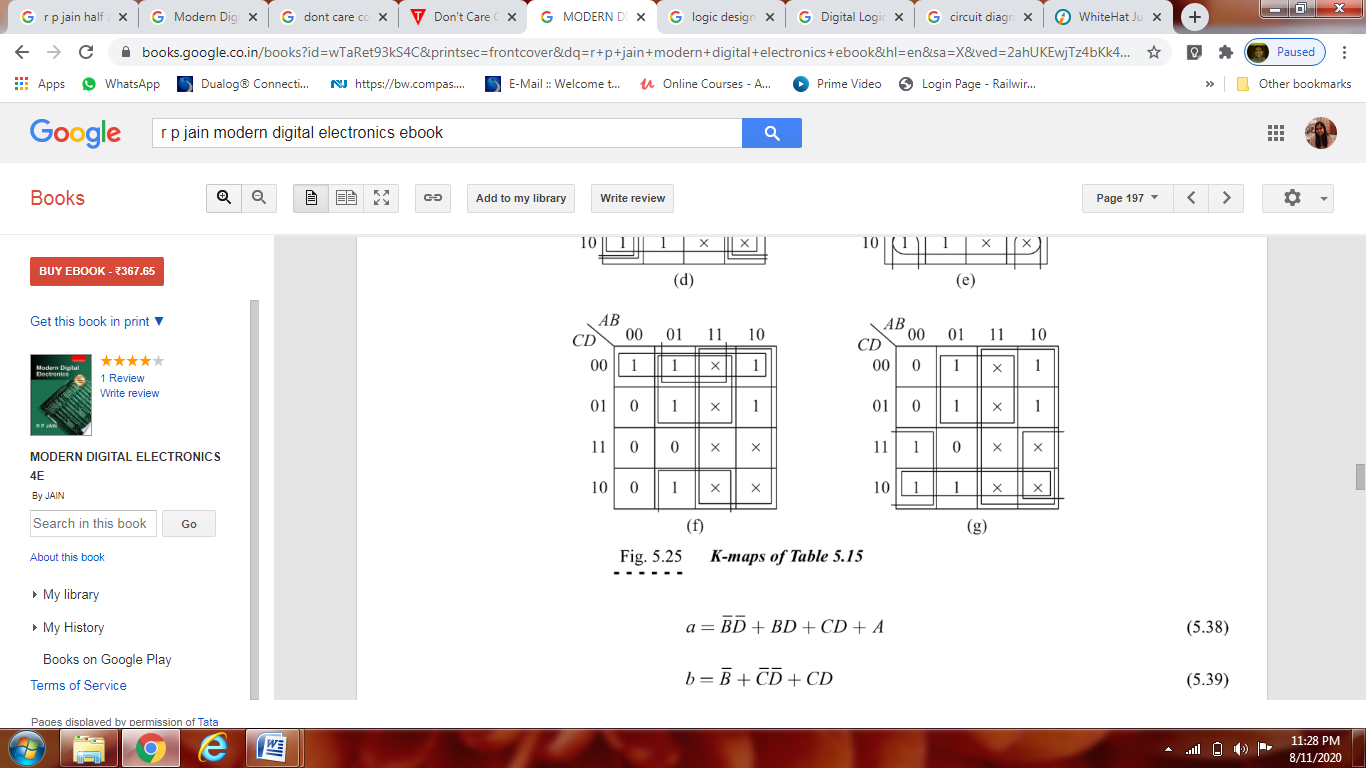

The K-Maps for each of the outputs A through G are given below:

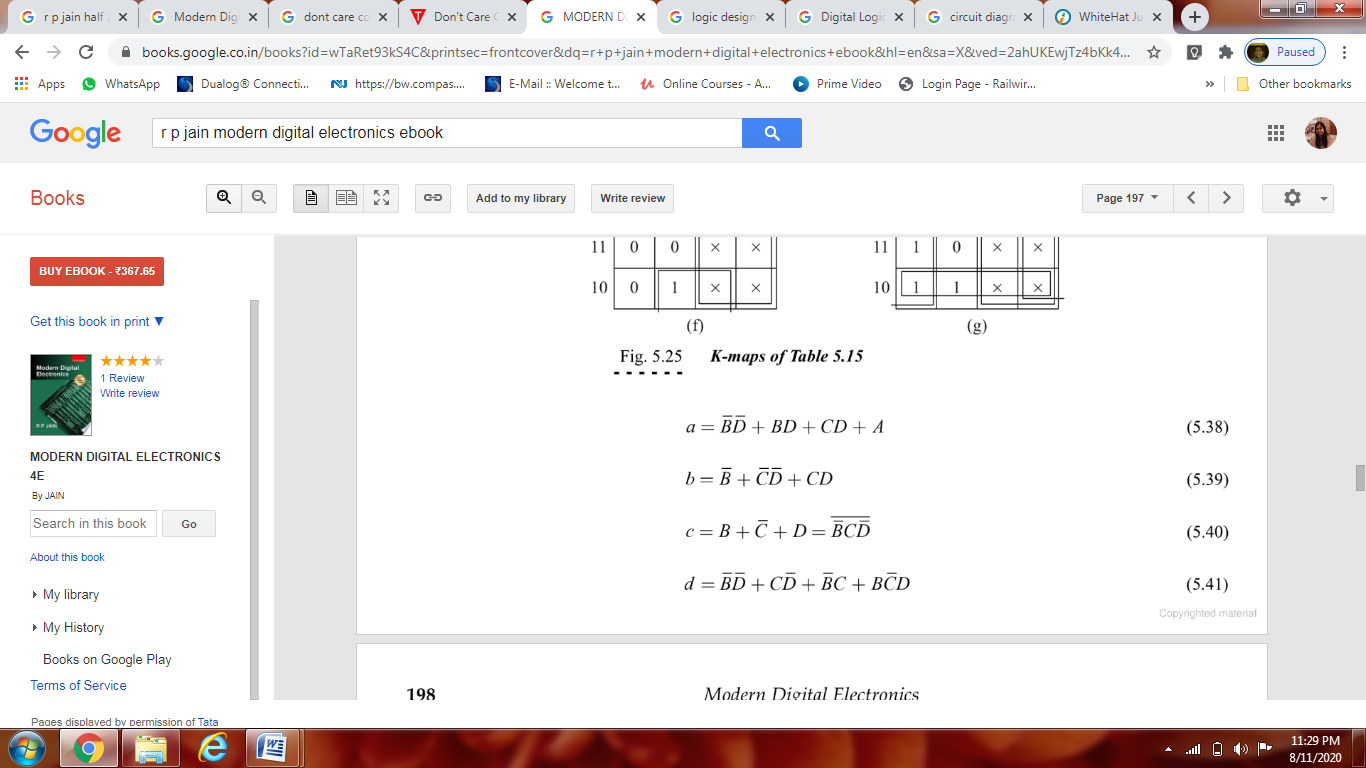

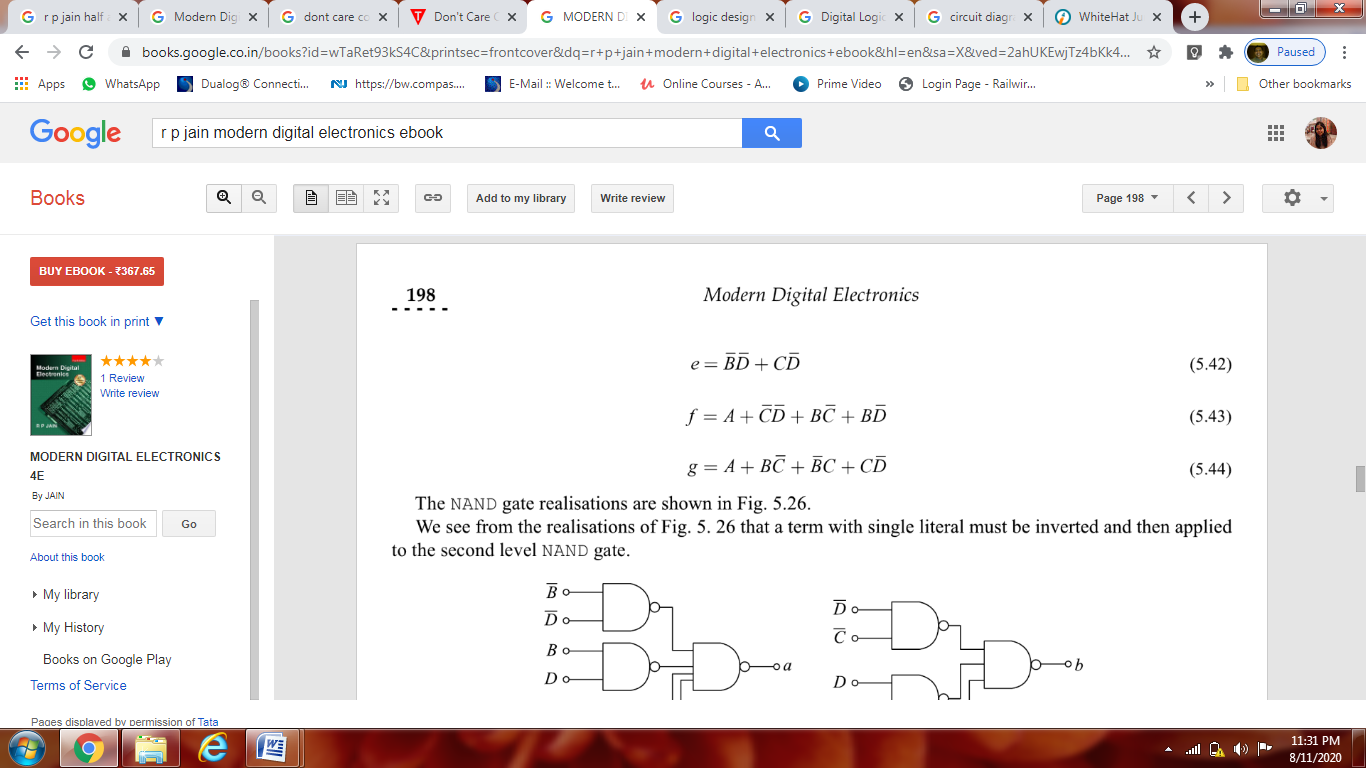

The simplified expressions obtained from the k-maps are:

Logic diagram:

Fig.8: Circuit of 7 segment display

Q5) Explain half and full adder.

A5)

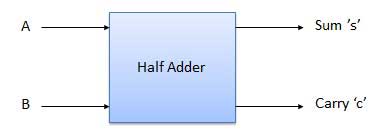

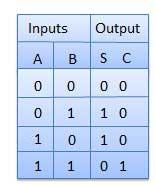

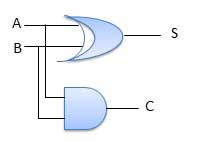

It is a combinational circuit which has two inputs and two outputs.

It is designed to add two single bit binary number A and B.

It has two outputs carry and sum.

Block diagram

Fig. 9: Half adder (ref. 2)

Truth Table

Circuit Diagram

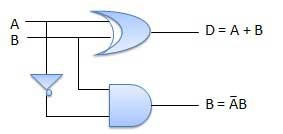

Fig.10: Half adder (ref. 2)

Full Adder

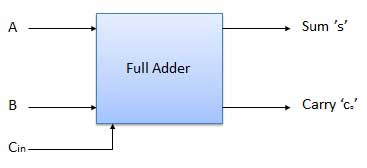

It is developed to overcome the drawback of Half Adder circuit.

It can add two one-bit numbers A and B and a carry C.

It is a three input and two output combinational circuit.

Block diagram

Fig.11: Full adder (ref. 2)

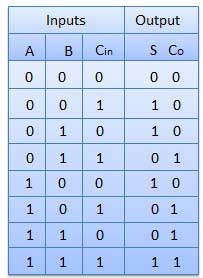

Truth Table

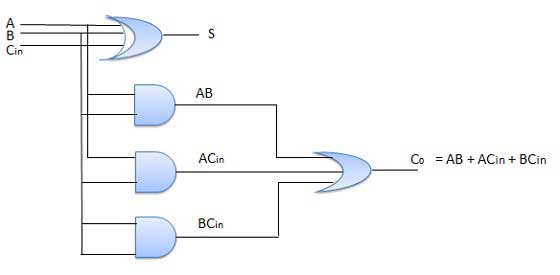

Circuit Diagram

Fig.12: Full adder (ref. 2)

Q6) Explain Half and full subtractor.

A6)

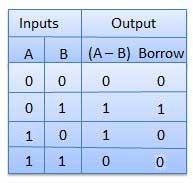

Half Subtractors

It is a combination circuit with two inputs and two outputs.

The difference between the two binary bits is obtained at the output and an output (Borrow) indicates if a 1 has been borrowed.

Here A is called Minuend bit and B is called a Subtrahend bit.

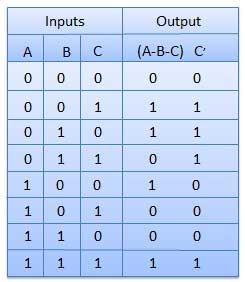

Truth Table

Circuit Diagram

Fig.13: Half subtractor (ref. 2)

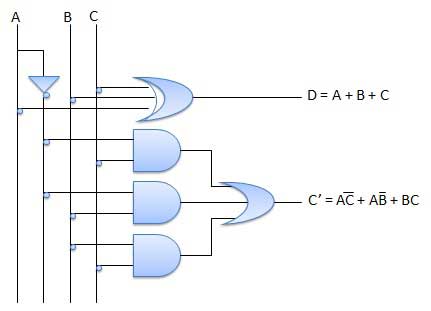

Full Subtractors

It is a combinational circuit which has three inputs A, B, C, and two output D and C'.

A is the 'minuend', B is 'subtrahend', C is the 'borrow' which is produced by the previous stage, difference output D and C' is the borrow output.

Truth Table

Circuit Diagram

Fig.14: Full subtractor (ref. 2)

Q7) Compare Serial and parallel adder.

A7)

- Serial Adder:

A serial adder is used to add two binary numbers in serial form. The two binary numbers to be added serially are stored in two shift registers. The circuit adds one pair at a time with the help of one full adder. The carry output from the full adder is applied to a D flip-flop, the output of which is then used as a carry input for the next pair of significant bits. However the sum bit S from the output of the full adder can be transferred into a third shift register.

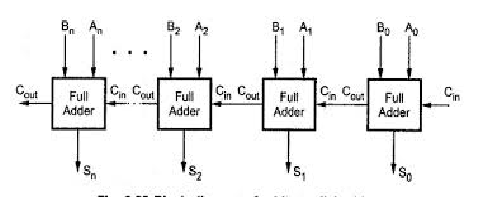

2. Parallel Adder:

A parallel adder is a combinational digital circuit that adds two binary numbers in parallel form. It consists of full adders connected in cascade, with the output carry from each full adder connected to the input carry of the next full adder.

Fig.15: Parallel Adder

Q8) For Input : A = 0101 B = 1001 find output using BCD adder.

A8)

Output:

Y = 1 0100

Explanation: We are adding A(=5) and B(=9).

The value of the binary sum will be 1110(=14).

But, the BCD sum will be 1 0100,

Where 1 is 0001 in binary and 4 is 0100 in binary.

Now, let's move to the table and find out the logic when we are going to add “0110”.