Question Bank

Unit 5

Question Bank

Unit 5

Basic Electronics

- Explain Number systems & their conversion used in digital electronics.

Answer:

Number system and conversions

A digital system understands positional number system where there are few symbols called digits and this symbol represents different values depending on their position in the number.

A value of the digit is determined by using

- The digit

- Its position

- The base of the number system

Decimal Number System

- It’s the system that we use in our daily life. It has a base 10 and uses 10 digits from 0 to 9.

- Here, the successive positions towards the left of the decimal point represent units, tens, hundreds, thousands and so on.

- Each and every position represents a specific power of the base (10). For example, the decimal number 4321 consists of the digit 1 in the units position, 2 in the tens position, 3 in the hundreds position, and 4 in the thousands position, and its value can be written as

(1×1000) + (2×100) + (3×10) + (4×l)

(1×103) + (2×102) + (3×101) + (4×l00)

1000 + 200 + 30 + 1

1234

- As a computer programmer, we should understand the following number systems used in computers.

S.N. | Number System & Description |

1 | Binary Number System Base 2. Digits used: 0 and 1 |

2 | Octal Number System Base 8. Digits used: 0 to 7 |

3 | Hexa Decimal Number System Base 16. Digits used: 0 to 9, Letters used: A- F |

2. What are Binary number system and octal number system?

Answer:

Binary number system their conversion

- It uses two digits 0 and 1.

- It is also called as base 2 number system.

- Here, each position in any binary number represents a power of the base (2). Example: 23

- The last position represents a y power of the base (2). Example: 2y where y represents the last position.

Example

Binary Number: 101112

Calculating the Decimal Equivalent of binary number −

Step | Binary Number | Decimal Number |

Step 1 | 101012 | ((1 × 24) + (0 × 23) + (1 × 22) + (1 × 21) + (1 × 20))10 |

Step 2 | 101012 | (16 + 0 + 4 + 2 + 1)10 |

Step 3 | 101012 | 2310 |

Note: 101112 is normally written as 10111.

Octal Number System

- It consists of eight digits 0, 1,2,3,4,5,6,7.

- It is also named as base 8 number system.

- Here each position represents a power of the base (8). Example: 82

- The last position represents a y power of the base (8). Example: 8y where y represents the last position .

Example

Octal Number − 125758

Calculating Decimal Equivalent −

Step | Octal Number | Decimal Number |

Step 1 | 125758 | ((1 × 84) + (2 × 83) + (5 × 82) + (7 × 81) + (5 × 80))10 |

Step 2 | 125758 | (4096 + 1024 + 320 + 56 + 5)10 |

Step 3 | 125758 | 550010 |

Note: 125758 is normally written as 12575 in octal.

3. What is hexadecimal number system and their conversion?

Answer:

Hexadecimal Number System

- It uses 10 digits starting from 0,1,2,3,4,5,6,7,8,9 and 6 letters A,B,C,D,E,F.

- These letters represents numbers as A = 10, B = 11, C = 12, D = 13, E = 14, F = 15.

- It is also known as base 16 number system.

- Here each position represents a power of the base (16). Example 161.

- The last position represents a y power of the base (16). Example: 16y where y represents the last position .

Example −

Hexadecimal Number: 19FDA16

Calculating Decimal Equivalent −

Step | Hexadecimal Number | Decimal Number |

Step 1 | 19FDA16 | ((1 × 164) + (9 × 163) + (F × 162) + (D × 161) + (A × 160))10 |

Step 2 | 19FDA16 | ((1 × 164) + (9 × 163) + (15 × 162) + (13 × 161) + (10 × 160))10 |

Step 3 | 19FDA16 | (65536 + 36864 + 3840 + 208 + 10)10 |

Step 4 | 19FDA16 | 10645810 |

Note − 19FDA16 is normally written as 19FDA in hexa decimal.

Conversions

There are many techniques which are used to convert numbers from one base to another. These are as follows −

- Decimal to any other Base System

- Any Base System to Decimal

- Any Base System to Non-Decimal

- Binary to Octal

- Octal to Binary

- Binary to Hexadecimal

- Hexadecimal to Binary

Decimal to Any Base System

It includes the following steps:

- Firstly, divide the decimal number which is to be converted by the value of its new base.

- Then, after getting the remainder from the above step make it the rightmost digit (least significant digit) i.e. LSD of new base number.

- Further divide the quotient by the new base.

- Then record the remainder from the above step as the next digit (towards the left) of the new base number.

- Repeat these steps and get remainders from right to left till the quotient becomes zero.

- The last remainder obtained will be the Most Significant Digit (MSD) of the new base number.

For example −

Decimal Number: 2710

Calculating Binary Equivalent −

Step | Operation | Result | Remainder |

Step 1 | 27 / 2 | 13 | 1 |

Step 2 | 13 / 2 | 6 | 1 |

Step 3 | 6 / 2 | 3 | 0 |

Step 4 | 3 / 2 | 1 | 1 |

Step 5 | 1 / 2 | 0 | 1 |

Hence, the remainders are arranged in the reverse order and we get:

Decimal Number − 2710 = Binary Number − 110112.

Any Base System to Decimal System

- Here, the column (positional) value of each digit (this depends on the position of the digit and the base of the number system) is multiplied with the obtained column values of the digits in the corresponding columns.

- The sum the products is then calculated which gives the total equivalent value in decimal.

For example :

Binary Number − 111102

Calculating Decimal Equivalent −

Step | Binary Number | Decimal Number |

Step 1 | 111102 | ((1 × 24) + (1 × 23) + (1 × 22) + (1 × 21) + (0 × 20))10 |

Step 2 | 111102 | (16 + 8 + 4 + 2 + 0)10 |

Step 3 | 111102 | 3010 |

Binary Number − 111102 = Decimal Number − 3010

Any Base System to Non-Decimal System

- The original number is converted to its equivalent decimal number (base 10).

- Then the decimal number so obtained is further converted to the new base number.

Example

Octal Number − 268

Calculating its Binary Equivalent −

Step 1 – Converting octal to Decimal

Step | Octal Number | Decimal Number |

Step 1 | 268 | ((2 × 81) + (6 × 80))10 |

Step 2 | 268 | (16 + 6 )10 |

Step 3 | 268 | 2210 |

Octal Number − 268 = Decimal Number − 2210

Step 2 − Converting Decimal to Binary

Step | Operation | Result | Remainder |

Step 1 | 22 / 2 | 11 | 0 |

Step 2 | 11 / 2 | 5 | 1 |

Step 3 | 5 / 2 | 2 | 1 |

Step 4 | 2 / 2 | 1 | 0 |

Step 5 | 1 / 2 | 0 | 1 |

Decimal Number − 2210 = Binary Number − 101102

Octal Number − 268 = Binary Number − 101102

Binary to Octal

- Dividing the binary digits into groups of three starting from right to left.

- Converting each group of three binary digits into one octal digit.

For example:

Binary Number − 101012

Its Octal Equivalent −

Step | Binary Number | Octal Number |

Step 1 | 101012 | 010 101 |

Step 2 | 101012 | 28 58 |

Step 3 | 101012 | 258 |

Binary Number − 101012 = Octal Number − 258

Octal to Binary

- Converting each octal digit to a 3 digit binary number and they can be treated as decimal number for this conversion.

- Then combining all the resulting binary groups into a single binary number.

For example:

Octal Number − 258

Its Binary Equivalent −

Step | Octal Number | Binary Number |

Step 1 | 258 | 210 510 |

Step 2 | 258 | 0102 1012 |

Step 3 | 258 | 0101012 |

Octal Number − 258 = Binary Number − 101012

Binary to Hexadecimal

- Dividing the binary digits into groups of four (starting from right to left).

- Then converting each group of four binary digits into one hexadecimal number.

For example:

Binary Number − 101012

Its hexadecimal Equivalent −

Step | Binary Number | Hexadecimal Number |

Step 1 | 101012 | 0001 0101 |

Step 2 | 101012 | 110 510 |

Step 3 | 101012 | 1516 |

Binary Number − 101012 = Hexadecimal Number − 1516

Hexadecimal to Binary

- Converting each hexadecimal digit to a 4 digit binary number and they can be treated as decimal number.

- Combining all the resulting binary groups into a single binary number.

For example:

Hexadecimal Number − 1516

Its Binary Equivalent −

Step | Hexadecimal Number | Binary Number |

Step 1 | 1516 | 110 510 |

Step 2 | 1516 | 00012 01012 |

Step 3 | 1516 | 000101012 |

Hexadecimal Number − 1516 = Binary Number − 101012

4. What is De Morgan’s theorem?

Answer:

- It is useful in finding the complement of Boolean function.

- It states that “The complement of logical OR of at least two Boolean variables is equal to the logical AND of each complemented variable”.

- It can be represented using 2 Boolean variables x and y as

(x + y)’ = x’.y’

- The dual of the above Boolean function is

(x.y)’ = x’ + y’

- Therefore, the complement of logical AND of the two Boolean variables is equivalent to the logical OR of each complemented variable.

- Similarly, DeMorgan’s theorem can be applied for more than 2 Boolean variables also.

Simplify Boolean Functions.

Answer:

Numerical

- Simplify the Boolean function,

f = p’qr + pq’r + pqr’ + pqr

Method 1

Given

f = p’qr + pq’r + pqr’ +pqr.

In first and second term r is common and in third and fourth terms pq is common.

So, taking out the common terms by using Distributive law we get,

⇒ f = (p’q + pq’)r + pq(r’ + r)

The terms present in first parenthesis can be simplified by using Ex-OR operation.

The terms present in second parenthesis is equal to ‘1’ using Boolean postulate we get

⇒ f = (p ⊕q)r + pq(1)

The first term can’t be simplified further.

But, the second term is equal to pq using Boolean postulate.

⇒ f = (p ⊕q)r + pq

Therefore, the simplified Boolean function is f = (p⊕q)r + pq

Method 2

Given f = p’qr + pq’r + pqr’ + pqr.

Using the Boolean postulate, x + x = x.

Hence we can write the last term pqr two more times.

⇒ f = p’qr + pq’r + pqr’ + pqr + pqr + pqr

Now using the Distributive law for 1st and 4th terms, 2nd and 5th terms, 3rdand 6th terms we get.

⇒ f = qr(p’ + p) + pr(q’ + q) + pq(r’ + r)

Using Boolean postulate, x + x’ = 1 and x.1 = x for further simplification .

⇒ f = qr(1) + pr(1) + pq(1)

⇒ f = qr + pr + pq

⇒ f = pq + qr + pr

Therefore, the simplified Boolean function is f = pq + qr + pr.

Hence we got two different Boolean functions after simplification of the given Boolean function. Functionally, these two functions are same. As per requirement, we can choose one of them.

Numerical

Find the complement of the Boolean function,

f = p’q + pq’.

Solution:

Using DeMorgan’s theorem, (x + y)’ = x’.y’ we get

⇒ f’ = (p’q)’.(pq’)’

Then by second law, (x.y)’ = x’ + y’ we get

⇒ f’ = {(p’)’ + q’}.{p’ + (q’)’}

Then by using, (x’)’=x we get

⇒ f’ = {p + q’}.{p’ + q}

⇒ f’ = pp’ + pq + p’q’ + qq’

Using x.x’=0 we get

⇒ f = 0 + pq + p’q’ + 0

⇒ f = pq + p’q’

Therefore, the complement of Boolean function, p’q + pq’ is pq + p’q’.

5. What are the basic logic gates? Explain each.

Answer:

The basic gates are namely AND gate, OR gate & NOT gate.

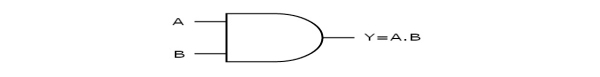

AND gate

It is a digital circuit that consists of two or more inputs and a single output which is the logical AND of all those inputs. It is represented with the symbol ‘.’.

The following is the truth table of 2-input AND gate.

A | B | Y = A.B |

0 | 0 | 0 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 1 |

Here A, B are the inputs and Y is the output of two input AND gate.

If both inputs are ‘1’, then only the output, Y is ‘1’. For remaining combinations of inputs, the output, Y is ‘0’.

The figure below shows the symbol of an AND gate, which is having two inputs A, B and one output, Y.

Fig. : AND gate (ref. 1)

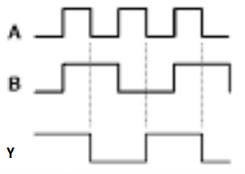

Timing Diagram:

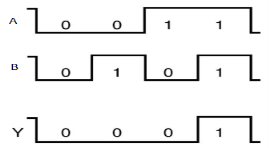

OR gate

It is a digital circuit which has two or more inputs and a single output which is the logical OR of all those inputs. It is represented with the symbol ‘+’.

The truth table of 2-input OR gate is:

A | B | Y = A + B |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 1 |

Here A, B are the inputs and Y is the output of two input OR gate.

When both inputs are ‘0’, then only the output, Y is ‘0’. For remaining combinations of inputs, the output, Y is ‘1’.

The figure below shows the symbol of an OR gate, which is having two inputs A, B and one output, Y.

Fig. : OR gate (ref. 1)

Timing Diagram:

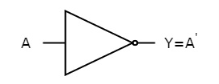

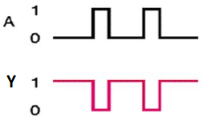

NOT gate

It is a digital circuit that has one input and one output. Here the output is the logical inversion of input. Hence, it is also called as an inverter.

The truth table of NOT gate is:

A | Y = A’ |

0 | 1 |

1 | 0 |

Here A and Y are the corresponding input and output of NOT gate. When A is ‘0’, then, Y is ‘1’. Similarly, when, A is ‘1’, then, Y is ‘0’.

The figure below shows the symbol of NOT gate, which has one input, A and one output, Y.

Fig. : NOT gate (ref. 1)

Timing Diagram:

6. What are universal gates? Explain each.

Answer:

Universal gates

NAND & NOR gates are known as universal gates.

We can implement any Boolean function by using NAND gates and NOR gates alone.

NAND gate

It is a digital circuit which has two or more inputs and single output and it is the inversion of logical AND gate.

The truth table of 2-input NAND gate is:

A | B | Y = (A.B)’ |

0 | 0 | 1 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

Here A, B are the inputs and Y is the output of two input NAND gate. When both inputs are ‘1’, then the output, Y is ‘0’. If at least one of the input is zero, then the output, Y is ‘1’. This is just the inverse of AND operation.

The image shows the symbol of NAND gate:

Fig.: NAND gate (ref. 1)

NAND gate works same as AND gate followed by an inverter.

Timing Diagram:

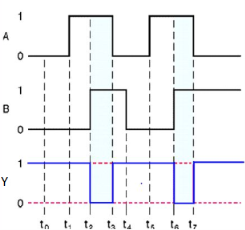

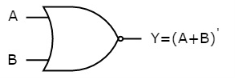

NOR gate

It is a digital circuit that has two or more inputs and a single output which is the inversion of logical OR of all inputs.

The truth table of 2-input NOR gate is:

A | B | Y = (A+B)’ |

0 | 0 | 1 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 0 |

Here A and B are the two inputs and Y is the output. If both inputs are ‘0’, then the output is ‘1’. If any one of the input is ‘1’, then the output is ‘0’. This is exactly opposite to two input OR gate operation.

The symbol of NOR gate is:

Fig.: NOR gate (ref. 1)

NOR gate works exactly same as that of OR gate followed by an inverter.

Timing Diagram:

7. Explain Ex-OR gate and Ex-NOR gate.

Answer:

Ex-OR gate

It stands for Exclusive-OR gate. Its function varies when the inputs have even number of ones.

The truth table of 2-input Ex-OR gate is:

A | B | Y = A⊕B |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 1 |

1 | 1 | 0 |

Here A, B are the inputs and Y is the output of two input Ex-OR gate. The output (Y) is zero instead of one when both the inputs are one.

Therefore, the output of Ex-OR gate is ‘1’, when only one of the two inputs is ‘1’. And it is zero, when both inputs are same.

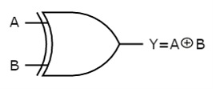

The symbol of Ex-OR gate is as follows:

Fig.: XOR gate (ref. 1)

It is similar to that of OR gate with an exception for few combination(s) of inputs. Hence, the output is also known as an odd function.

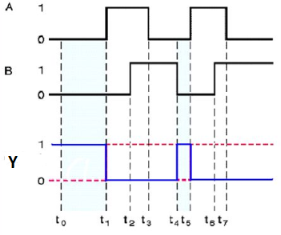

Timing Diagram:

Ex-NOR gate

It stands for Exclusive-NOR gate. Its function is same as that of NOR gate except when the inputs having even number of ones.

The truth table of 2-input Ex-NOR gate is:

A | B | Y = A⊙B |

0 | 0 | 1 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 1 |

Here A, B are the inputs and Y is the output. It is same as Ex-NOR gate with the only modification in the fourth row. The output is 1 instead of 0, when both the inputs are one.

Hence the output of Ex-NOR gate is ‘1’, when both inputs are same and 0, when both the inputs are different.

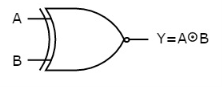

The symbol of Ex-NOR gate is:

Fig.: XNOR gate (ref. 1)

It is similar to NOR gate except for few combination(s) of inputs. Here the output is ‘1’, when even number of 1 is present at the inputs. Hence is also called as an even function.

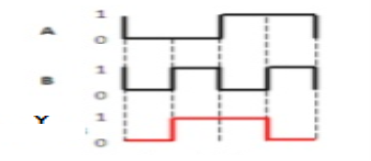

Timing Diagram:

8. What is a Half adder circuit?

Answer:

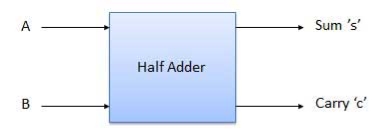

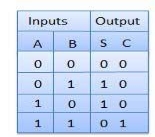

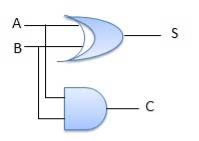

Half Adder

It is a combinational circuit which has two inputs and two outputs.

It is designed to add two single bit binary number A and B.

It has two outputs carry and sum.

Block diagram

Fig. : Half adder (ref. 2)

Truth Table

Circuit Diagram

Fig.: Half adder (ref. 2)

9. What is a full adder circuit?

Answer:

Full Adder

It is developed to overcome the drawback of Half Adder circuit.

It can add two one-bit numbers A and B and a carry C.

It is a three input and two output combinational circuit.

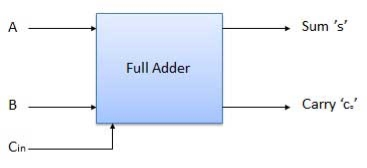

Block diagram

Fig. : Full adder (ref. 2)

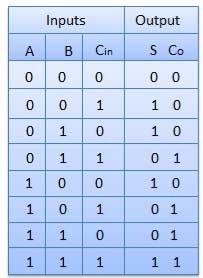

Circuit Diagram

Fig. : Full adder (ref. 2)

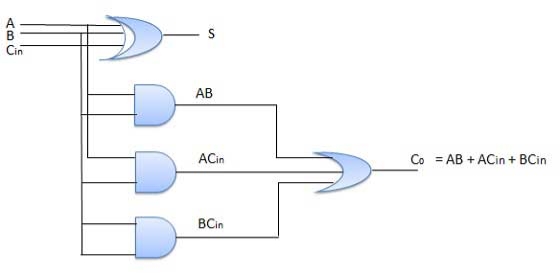

10. What is R-S flip flop?

Answer:

SR Flip Flop

What is J-K flip flop?

Answer:

JK Flip Flop

Race Around Condition In JK Flip-flop –

- For J-K flip-flop, if J=K=1, and if clk=1 for a long period of time, then output Q will toggle as long as CLK remains high which makes the output unstable or uncertain.

- This problem is known as race around condition in J-K flip-flop.

- This problem can be avoided by ensuring that the clock input is at logic “1” only for a very short time.

- Hence the concept of Master Slave JK flip flop was introduced.

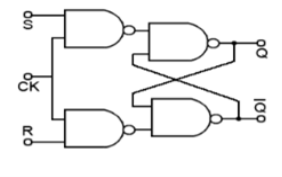

11. What is master slave JK flip flop? Explain working and also draw timing diagram.

Answer:

Master Slave JK flip flop –

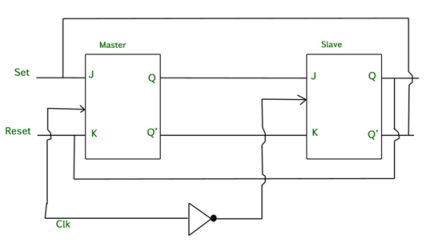

It is basically a combination of two JK flip-flops connected together in series.

The first is the “master” and the other is a “slave”.

The output from the master is connected to the two inputs of the slave whose output is fed back to inputs of the master.

In addition to these two flip-flops, the circuit comprises of an inverter.

The inverter is connected to clock pulse in such a way that an inverted clock pulse is given to the slave flip-flop.

In other words if CP=0 for a master flip-flop, then CP=1 for a slave flip-flop and vice versa.

Fig. Master Slave Flip flop

Working of a master slave flip flop –

- When the clock pulse goes high, the slave is isolated; J and K inputs can affect the state of the system. The slave flip-flop is isolated when the CP goes low. When the CP goes back to 0, information is transmitted from the master flip-flop to the slave flip-flop and output is obtained.

- The master flip flop is positive level triggered and the slave flip flop is negative level triggered, hence the master responds prior to the slave.

- If J=0 and K=1, Q’ = 1 then the master goes to the K input of the slave and the clock forces the slave to reset therefore the slave copies the master.

- If J=1 and K=0, Q = 1 then the master goes to the J input of the slave and the Negative transition of the clock sets the slave and thus copy the master.

- If J=1 and K=1, the master toggles on the positive transition and the slave toggles on the negative transition of the clock.

- If J=0 and K=0, the flip flop becomes disabled and Q remains unchanged.

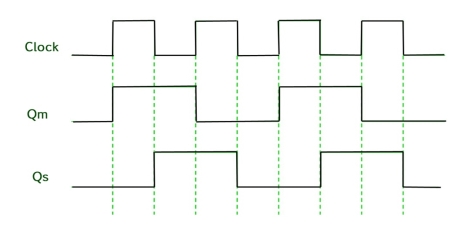

Timing Diagram of a Master flip flop –

- When the CP = 1 then the output of master is high and remains high till CP = 0 because the state is stored.

- Now the output of master becomes low when the clock CP = 1 and remains low until the clock becomes high again.

- Thus toggling takes place for a clock cycle.

- When the CP = 1 then the master is operational but not the slave.

- When the clock is low, the slave becomes operational and remains high until the clock again becomes low.

- Toggling takes place during the whole process since the output changes once in a cycle.

- This makes the Master-Slave J-K flip flop a Synchronous device which passes data with the clock signal.

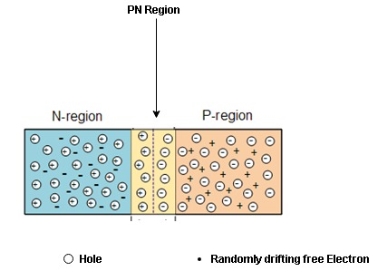

12. What is N type and P type Semiconductors? Explain.

Answer:

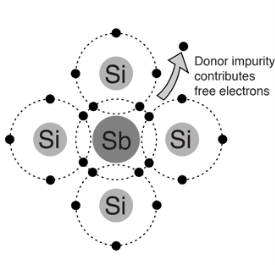

N type Semiconductor:-

To increase the number of conduction band electrons inintrisic silicon , pentavalent imparity atoms are added. These are atoms with five valence electrons such as

i) arsenic (as)

Ii) phosphors (p)

Iii) Bismuth (Bi)

Iii) Antimony ( sb)

- Pentavalent impurity atom in a silicon crystal. An antimony (sb) impurity atom shown above-

- Each pentavalent atom forms covalent bonds with four adjustment silicon atoms, leaving one extra electron .

- The pentavalentatom gives up on electron , it often called a donor atom.

- Majority and minority carriers:- A type here means negative charge of an electron .electron are called the majority carriers in n-type material.

- Hole in an n-type material are called minority carriers

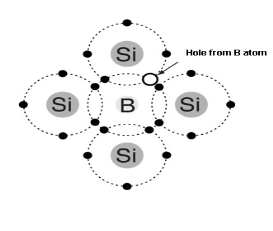

P Type Semiconductor :-

To increase the number of holes in intrinsic silicon trivalent impurity atoms are added these are atoms with there valence electrons such as

i) Baron(B)

Ii) Indium(IN)

iii)Gallium(GO)

- Trivalent impurity atom in a silicon crystal structure . A) boron (B) impurity atom is shown in the center.

- The number of holes can be carefully controlled by the number of trivalent impurity atoms added to the silicon .

- A Hole created by the doping process is not accompanied by a conduction (free) electron.

- Trivalent Atom can take an electron it is often referred to as on accepted atom

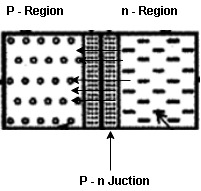

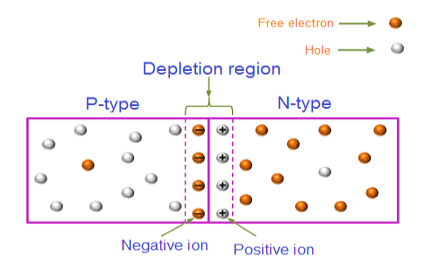

13. Explain Diodes and V-I characteristics.

Answer:

The Diode- Before doping the p-type & N-type consisting silicon material atom acting as a neutral.

IF a piece of intrinsic silicon is doped so that part is n-type and the other part is p-type , a junction forms at the bounded between the two regions and a diode is created.

Formation of the Depletion Region

At the instant of junction formation , free electrons in the N-region near the p-n junction being to diffuse across the junction and fall into holes near the junction in the P-region.

For every electron that defuse across the junction and combines with a hole , a positive charge is left in the region and a ve charge is created in the p-region firming a barriers potential. This action continues until the vtg of the barrier ripples further diffusion .

The Depletion region acts as a barriers to the farther movement of electrons across the junction

As positive ion & -ve ion across the junction produces a electric field across the junction -according to coulombs law.

The potential difference of the electric field across the depletion region is the amount of vtg required to move electronics through the electric field, this potential difference is called the barrier potential & is expressed in volt

The typical barrier potential is approximately 0.7 v for silicon & 0.3 v for germanium at 25c.

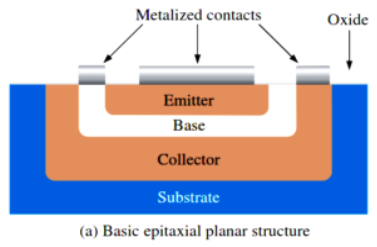

Explain Bipolar junction transistors (BJT) and their working.

Answer:

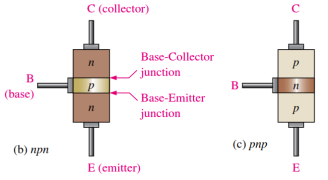

*BJT:- The BJT is constructed with the three draped semiconductors region’s separate by two Pn junctions as shown below

Basic epitaxial planner structures

-Three terminal with region’s are called emitter, base and collector.

The physical representation of the two types of BJT’s,

One type consists between two regions separated by a P region (npn) and other type consists of two p regions separated by an n region (pnp).

-The Pn junction joining the base region and the emitter region is called the base emitter junction.

-The Pn junction joining the base region and the collector region is called the base collector junction.

-The base region is lightly doped and very thin compared to the heavily doped emitter and the moderately doped collector regions.

14. What is base transistor operation?

Answer:

*Base Transistor Operation:-

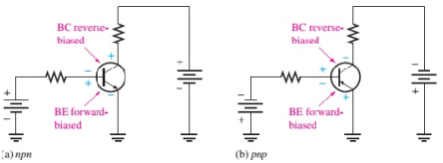

In order for the transistor to operate properly as an amplifier the two pn junction must be correctly biased with the external D.C vtg.

-The next figure shows the proper bias arrangement for both the npn and pnp transistors for active operation as an amplifier.

-In both the cases the base emitter

(BE) junction is forward biased & the base collector junction (BC) junction is reverse biased

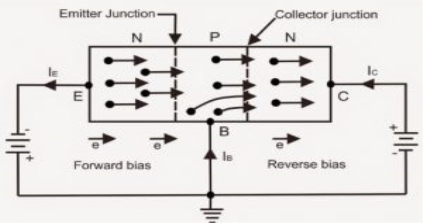

- As from above figure consider n-p-n transistor. The forward bias from base to emitter narrow’s the BE depletion region and the reverse bias from base to collector widens the BC depletion region shown in figure.

- The heavily doped N-TYPE emitter region is full with conduction band(frep) electron’s that easily diffuse through the forward biased BE junction into the p-type base region where they become minority carrier’s same as forward biased diode region

- The base region is lightly doped & very thin so that it has a very limited number of holes.

- Those only a small percentage of all the e-flowing the BE junction can combine with the available holes in the base.

- The relatively few recombined flow out of the base lead as valance electrons, forming as small base current.

- Most of the e flowing from the emitter into the thin lightly dooped base region do not recombine but diffuse into the BC depletion region.

- The BC depletion region diffuse e is being pulled across the reverse biased BC junction by the attraction of the collector supply vtg.

- The electrons now move through the collector region, out through the collector lead into the +ve terminal of the collector vtg source. This forms the collector electrons current.

- The collector current is much larger than the base current.

- This is the reason transistor exhibit current gain.

Explain CC, CB& CE transistor configurations.

Answer:

Transistor’s Configuration:-

1) Common Base configuration(C.B)

2) Common emitter Configuration(C.E)

3) Common Collector Configuration(C.C)

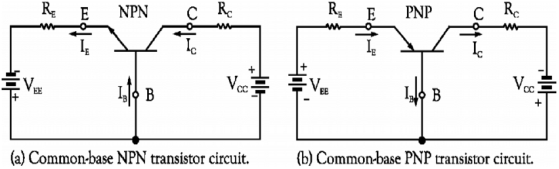

Common Base configuration(C.B):-

-The I/p is applied between the emitter and the base. The base acts as a common terminal between the I/p and o/p.

-The input vtg is therefore VEB and the input current is IE.

-The output is taken between the collector and the base therefore the output vtg is VCB and the output current is IC.

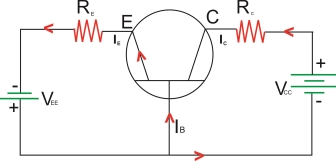

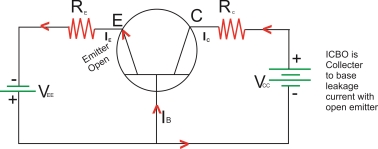

* Current relation’s in CB configuration:-

-The collector current is IC of the common base configuration is given by

Ic=Ic(INI)+ICBO

-Where the Ic(INI) called the injected collectors current and it is due to the number of electrons crossing the collectors base junction.

-ICBO :- This is the reverse saturation current flowing due to the minority carrier’s between the collector and base when the emitter is open

-ICBO flow’s due to the reverse biased collector’s base junction. As ICBO negligible as compared to Ic(INI) we can neglect it in practice.

.’. Ic=Ic(INI)………………………practically

Ic=ICBO………………with emitter open

Emitter is open

Emitter is open

ICBO

ICBO

Collector is to base control

-Since the ICBO flow’s due to terminally generated minority carrier’s it increases with increase the temperature.

-It doubles it’s value for every 100c rise in temperature.

15. What is Current amplification factor or current gain?

Answer:

Current amplification factor or current gain is the ratio of collector current due to the injection to the total emitter current

αd.c = Ic(INI)

-The value of the ddc for CB configuration will always be less than 1.This is because

Ic(INI)<IE.

-Typically the value of d.d.c ranges between 0.95 to 0.995 depending upon the thickness of the base region.

-Larger the thickness of the base region smaller the value of the d.d.c

Ic(INI)=d.d.c.IE

Hence the expression for IC is given by

IC=αd.c IE + ICBo--------------------I

But the ICBo is negligibly small

IC d.d.c IE

d.d.c IE

* Expression for IB:-

IE=IB+IC

IE=αd.cIE+ICBo+IB…………………from I

IB=(1-αd.c)IE-ICBo

Neglecting ICBo

IB=(1-αd.c)IE

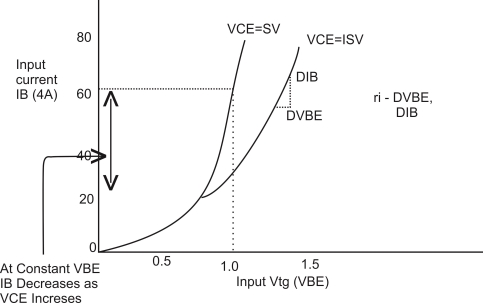

16. What are the Characteristics of transistors in a common base configuration?

Answer:

1. Input Characteristic:-

A. Input Characteristic: is always a graph of input current verses input vtg. For common base (CB) configuration input current is the emitter current (IE) & I/p vtg. Is the emitter to the base vtg (VEB)

The I/p Characteristic is plotted at a constant O/p vtg. VCB

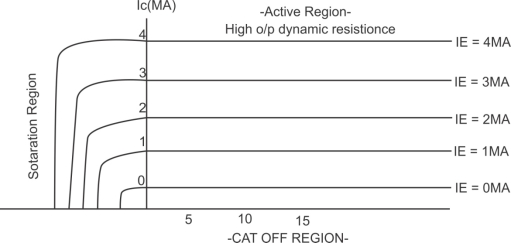

B. Output Characteristic:

Output Characteristic is always a graph of O/p current versus O/p Vtg.

For the CB configuration the O/p current is collector current (IC) of the output voltage is collector to base vtg. (VCB)

Output Characteristic is plotted for a constant value of I/p current (IE)

O/p Characteristic of a n-p-n transistor in CB Configuration

Dynamic O/p resistance (ro)

Ro =  / I

/ I  constant

constant

In the active region Ic does not depend on VCB. It depends only on the I/p current IE. That is why the transistor is called as a current controlled or current operated device.

Feature of CB configuration:

- Common terminal : base

- Input current : IE

- O/p current IC

- I/P Vtg. : VEB

- O/P Vtg. VCB

- Current gain :

( less than 1)

( less than 1) - Vtg. Gain : medium

- Input resistance : very low (20-)

- O/P resistance : very high (1 m-2)

- Application : as preamplifier