Unit - 2

Combinational Circuits

Q1) What is a Multiplexer? Explain 2:1 Mux in detail.

A1)

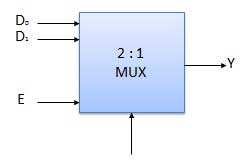

- It is a special type of combinational circuit.

- It has n-data inputs, one output and m inputs select lines with 2m = n.

- It selects one of the n data inputs and routes it to the output.

- The selection of one of the inputs is done by the select lines.

- Depending on the code applied at the inputs, one of the n data sources is selected and transmitted to the single output Y.

- E is the enable input which is useful for cascading purpose.

- It is an active low terminal hence performs the required operation when it is low.

Block diagram of multiplexer

Multiplexers come in multiple variations

- 2 : 1 multiplexer

- 4 : 1 multiplexer

- 16 : 1 multiplexer

- 32 : 1 multiplexer

Block Diagram of 2:1 MUX

Truth Table of 2:1 MUX

Where x is don’t care.

Q2) Draw and explain Full adder.

A2)

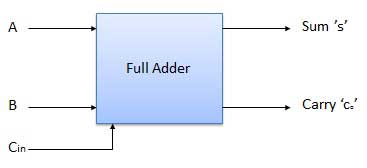

- It is developed to overcome the drawback of Half Adder circuit.

- It can add two one-bit numbers A and B and a carry C.

- It is a three input and two output combinational circuit.

Block diagram

Full adder

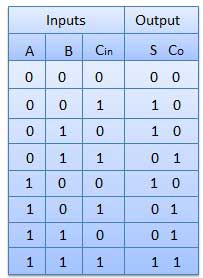

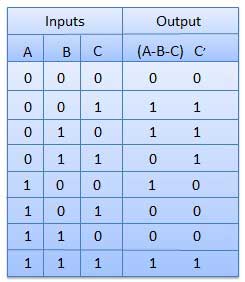

Truth Table

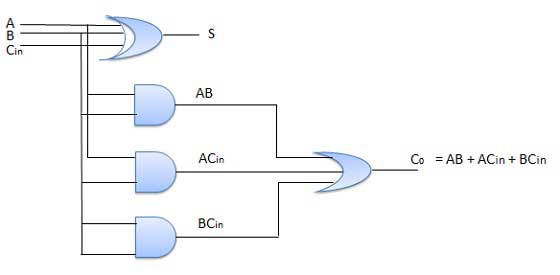

Circuit Diagram

Full adder

Q3) Draw and explain Full Subtractor.

A3)

It is a combinational circuit which has three inputs A,B,C and two output D and C'.

A is the 'minuend', B is 'subtrahend', C is the 'borrow' which is produced by the previous stage, difference output D and C' is the borrow output.

Truth Table

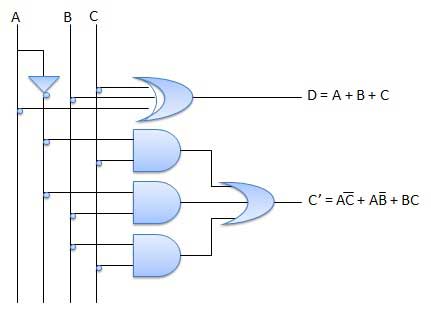

Circuit Diagram

Full subtractor

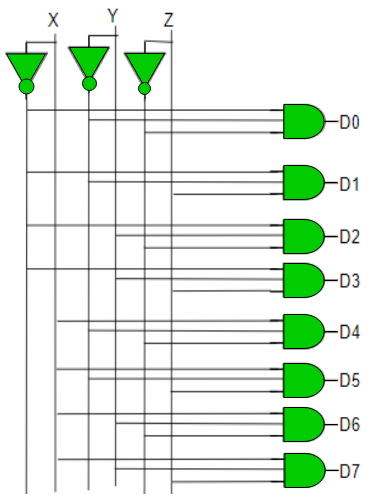

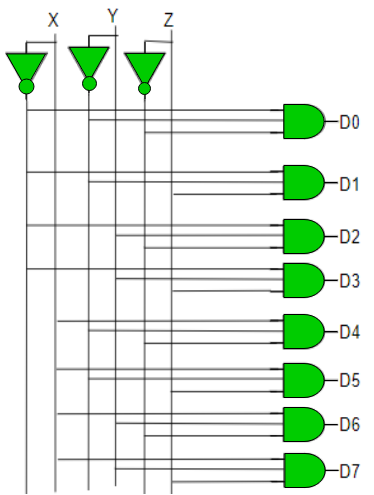

Q4) Explain decoder.

A4)

- It works as an inverse of an encoder.

- It is a combinational circuit which converts n input lines into 2n output lines.

- Taking an example of 3-to-8 line decoder.

Truth Table –

X | Y | Z | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Implementation

D0 is high when X = 0, Y = 0 and Z = 0. Hence,

D0 = X’ Y’ Z’

Similarly,

D1 = X’ Y’ Z

D2 = X’ Y Z’

D3 = X’ Y Z

D4 = X Y’ Z’

D5 = X Y’ Z

D6 = X Y Z’

D7 = X Y Z

Hence,

Q5) What is Priority Encoder? Draw its truth table.

A5)

- It is an encoder whose inputs are given priorities.

- When more than one input becomes active at the same time then the input with higher priority takes precedence w.r.to the output which is generated.

- Considering a 4:2 priority encoder.

- From the truth table given below we see that when all inputs are 0, V bit is zero and outputs are not used.

- The x in the table shows the don’t care condition, i.e. it can be 0 or 1.

- Here, D3 has highest priority, therefore, when D3 is high, output has to be 11.

- D0 has the lowest priority, hence the output would be 00 only when D0 is high and all the other input lines are low.

Truth Table –

D3 | D2 | D1 | D0 | X | Y | V |

0 | 0 | 0 | 0 | x | x | 0 |

0 | 0 | 0 | 1 | 0 | 0 | 1 |

0 | 0 | 1 | x | 0 | 1 | 1 |

0 | 1 | X | x | 1 | 0 | 1 |

1 | x | X | x | 1 | 1 | 1 |

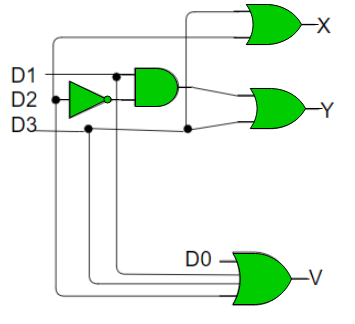

Implementation

The condition for valid bit to be 1 is when at least one of the inputs should be high. Hence,

V = D0 + D1 + D2 + D3

For X:

=>X=D2+D3

For Y:

=> Y = D1 D2’ + D3

Hence, the priority 4-to-2 encoder can be realized as follows:

Fig: Priority encoder

Q6) What does ALU do?

A6)

- An ALU performs mathematical and logical operations on binary numbers.

- They are located at the heart of every digital computer system and are one of the most important parts of a CPU (Central Processing Unit).

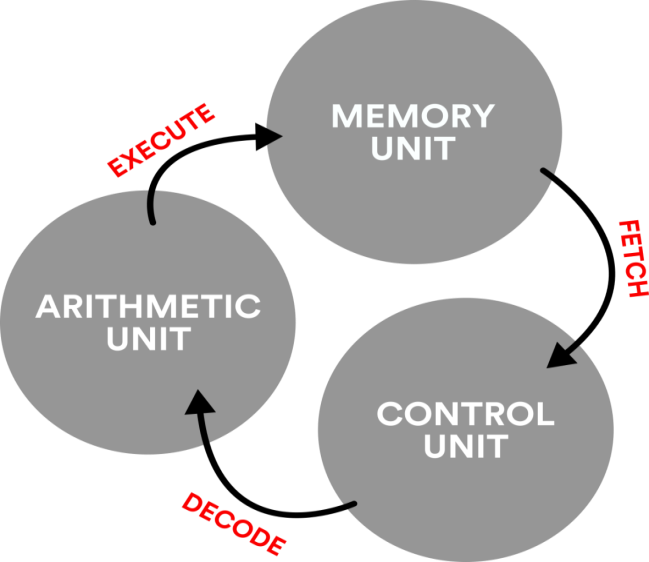

- Fetch-decode-execute refers to a computational process that continuously fetches the instructions from a memory, decodes them into operations and executes them to perform a calculation.

- These are simple steps which give rise to the complex behaviours that we expect from modern computing machines.

Fig. An illustration of the fetch-decode-execute cycle

This process can be further explained by linking each cycle step with three hardware subsystems called as a memory unit, a control unit, and an arithmetic unit.

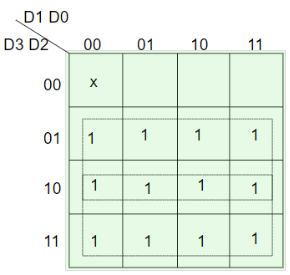

Q7) Convert Binary Code to Gray Code.

A7)

Binary To Gray Code

For this circuit, B3 B2 B1 B0 are inputs while G3 G2 G1 G0 are outputs.

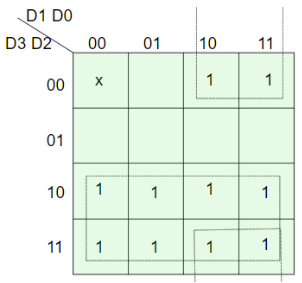

K-map for the outputs:

And G3 = B3

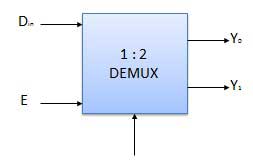

Q8) What is Demultiplexer?

A8)

- It performs the inverse operation of a multiplexer as it receives one input and distributes it across its outputs.

- It has only one input and n outputs with m select input.

- At a time only one output line is selected by the select lines and that input is transmitted through the output line.

- It is equivalent to a single pole multiple way switch.

Various Demultiplexers are used as:

- 1: 2 demultiplexer

- 1: 4 demultiplexer

- 1: 16 demultiplexer

- 1: 32 demultiplexer

Block diagram

Truth Table

Where x is don’t care.

Q9) Convert Gray code To Binary Code.

A9)

Then the K-maps:

And B3 = G3

The realization of Gray-to-Binary converter is

Q10) Implement 3:8 Decoder.

A10)

D0 is high when X = 0, Y = 0 and Z = 0. Hence,

D0 = X’ Y’ Z’

Similarly,

D1 = X’ Y’ Z

D2 = X’ Y Z’

D3 = X’ Y Z

D4 = X Y’ Z’

D5 = X Y’ Z

D6 = X Y Z’

D7 = X Y Z

Hence,

Decoder