Unit 3

Introduction to VHDL

Q1)What is VHDL?

A1)

Q2) Explain the elements of VHDL?

A2) There are the following three basic elements of VHDL:

1. Entity

The Entity is used to specify the input and output ports of the circuit.

An Entity usually has one or more ports that can be inputs (in), outputs (out), input-outputs (inout), or buffer.

An Entity may also include a set of generic values that are used to declare properties of the circuit.

Entity Declaration

You can declare an entity using the following syntax:

Simplified syntax

entity entity_name is

port (

port_1_name : mode data_type;

port_2_name : mode data_type;

.......

Port_n_name : mode data_type

);

end entity_name;

Example:

entiy orgate is

port (

a : in std_logic;

b : in std_logic;

c : out std_logic

);

end orgate;

Using generic

If an entity is generic, then it must be declared before the ports. Generic does not have a mode, so it can only pass information into the entity.

Syntax:

entity entity_name is

generic (

generic_1_name : data_type;

generic_2_name : data_type;

........

generic_n_name : data_type

);

port (

port_1_name : mode data_type;

port_2_name : mode data_type;

........

Port_n_name : mode data_type

);

end entity_name;

Example:

entity Logic_Gates is

generic (Delay : Time := 10ns);

port (

Input1 : in std_logic;

Input2 : in std_logic;

Output : out std_logic

);

end Logic_Gates;

Rules for writing Port name:

- Port name consist of letters, digits, and underscores.

- It always begins with a letter.

- Port name is case insensitive.

Modes of Port

in Input port

out Output port

inout Bidirectional port

buffer Buffered output port

2. Architecture

Architecture is the actual description of the design, which is used to describe how the circuit operates. It can contain both concurrent and sequential statements.

Architecture Declaration

An architecture can be declared using the following syntax:

architecture architecture_name of entity_name is

begin

(concurrent statements )

end architecture_name;

Example:

architecture synthesis of andgate is

begin

c <= a AND b;

end synthesis;

3. Configuration

A configuration defines how the design hierarchy is linked together. It is also used to associate architecture with an entity.

Configuration Declaration

configuration configuration_name of entity_name is

--configuration declarations

for architecture_name

for instance_label : component_name

use entity library_name.entity_name(architecture_name);

end for;

--

end for;

end [configuration] [configuration_name];

Example:

configuration demo_config of even_detector_testbench is

for tb_archi

for uut : even_detector

use entity work.even_detector (sop_archi);

end for;

end for;

end demo_config;

Q3) What are the modelling styles?

A3) Three type of Modeling Style in VHDL -

• Data Flow Modeling Style.

• Structural Modeling Style.

• Behavior Modeling Style.

Q4) Explain the sequential VHDL code?

A4) Sequential VHDL code is executed line by line.

“when/else” statement, the “if” statement incorporates priority-encoded logic. This means that the expressions of an “if” statement are evaluated successively, with higher priority given to the earlier expressions.

The “if” statement is more general than the “when/else” statement.

When using a process to describe a combinational circuit, we need to include all of the inputs in the sensitivity list.

The “case” statement as the sequential equivalent of the “with/select” statement; however, the “case” statement is more general.

The options of a “case” statement must be mutually exclusive, and all possible values of the control_expression must be included in the set of options.

Q5) Explain behavioural code?

A5) A behavioral describes the systems behaviour or function in algorithmic fashion. The behavioural style is the most abstract style. It consists of one or more process statements. Each process statements are a single concurrent statement that itself contains one or more sequential statements. The sequential statements are executed sequentially by the simulator.

Example

entity half_adder is

port(a,b: in std_logic);

end half_adder;

architecture behaviour of half_adder is

begin

ha: process(a,b)

begin

ha: process(a,b)

begin

if ‘a’ = 1 then

sum <= not b;

carry_out <= b;

else

sum <=b;

carry_out <=0;

end if;

end process ha;

end behaviour;

The entity declaration is same as dataflow architecture. The architecture consists of single process statement.

The process statement starts with the label ha followed by the keyword process.

Following the keyword process is a list of signal parentheses called sensitivity list. Between the second begin and keyword and the keyword end process is a sequential if statement. This if statement is executed whenever the process executes.

Q6) Explain the structural code?

A6) In structural style of modelling an entity is described as set of interconnected components. The top-level design entity’s architecture describes the interconnections of lower- level design entities. Each lower- level design entity can in turn be described as an interconnection of design entities at the next lower level.

This approach allows each design entity to be independently designed and verified before being used in higher level description.

entity half_adder is

Port ( a, b: in std _logic);

Sum, carry_out : out std_logic);

end half_adder;

Architecture structure of half_adder is

component xor gate

port(i1,i2:in std_logic);

end component;

component and_gate

port (i1,i2:in std_logic)

o1:out std_logic);

end component;

begin

u1; xor_gate port map(i1 =>a, i2 =>b,o1 => sum);

u2: and_gate port map(i1 =>a, i2 => b, o1 => carry_out);

= > u1: xor_gate port map(a,b,sum);

= > u1: and_gate port map(a,b,carry_out);

end structure

Q7) Explain data flow modelling?

A7) Dataflow style describes the system in terms of how data flows through the system. Data dependencies in the description match those in typical hardware implementation.

A dataflow description directly implies corresponding gate level implementation.

Dataflow descriptions consists of one or more concurrent signal assignments.

entity half_adder is

port(a,b: in std_logic);

sum, carry_out: out std_logic);

end half_adder;

architecture dataflow of half_adder is

begin

sum <= a xor b;

carry_out < =a and b ;

end dataflow;

The first assignment statement describes how input data flows from inputs a and b through an XOR function to create sum.

The second assignment statement describes hoe input data flows through an AND function to produce carry_out.

The concurrent signal assignment statements in this descriptions directly imply a hard ware implementation

Q8) Explain sequential and concurrent statements?

A8) Concurrent statements:

Architecture body

Simplified syntax

architecture arch_name of entity_name is declarations;

begin

concurrent statement;

concurrent statement;

concurrent statement;

………..

end arch_name;

syntax:

signal_name<= projected_waveform;

Example

y <= a+b+1 after 10ns;

- status <= ‘1’

- even <=(p1 and p2) or (p3 and p4);

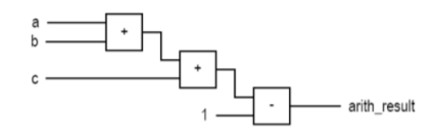

- arith_out < = a + b+c -1 ;

Conditional assignment statement

Syntax

signal_name < = value_expr-1 when boolean_expr_1 else

value-expr_2 when boolean_expr_2 else

value_expr_3 when Boolean_expr_3 else

…….

value_expr_n

Example 4:1 mux

library ieee;

use ieee.std_logic_1164.all;

entity mux4 is

port(

a,b,c,d: in std_logic_vector(7 downto 0);

a: in std_logic_vector(1 downto 0);

x: out std_logic_vector(7 downto 0)

);

end mux 4;

architecture cond-arch of mux4 is

begin

x<=a when (a=”00”) else

b when (a=”01”) else

c when(a=”10”) else

d;

end cond_arch;

Sequential statements

Syntax

Signal_name <= value_expression;

Syntax is identical to the simple concurrent signal assignment.

Eg

process(a,b,c,d)

begin y<= a or c;

y<= a and b;

y<= c and d;

end process;

It is same as

process(a,b,c,d)

begin

y<= c and d;

end process;

IF statement

Syntax

if boolean_expr-1 then

sequential statements;

elsif Boolean_expr_2 then

sequential statements ;

elsif Boolean_expr_3 then

sequential statements ;

…………

else

sequential_statements;

end if;

Example 4-to-1 mux

architecture if_arch of mux4 is

begin

process (a,b,c,d,s)

begin

if(s=”00”) then

x<=a;

elsif (s=”01”) then

x<=b;

elsif (s=”10”) then

x<=c;

else

x<=d;

end if;

end process;

end if-arch;

Q9) Explain the design flow?

A9) STEP 1 - Design Entry

The first step in the design process is to input your design into a machine-readable format. To do this use a Computer Aided Design (CAD) tool. In CMPE 480 Xilinx Foundation is used. A typical CAD tool supports many design entry methods, such as a schematic capture, HDL entry (VHDL/Verilog) or a component netlist

STEP 2 – Functional Simulation

Once a design has been captured, the next step is to simulate it. This is done to ensure that the design will meet the requirements of its specification. The first type of simulation that is performed is a Functional Simulation. This is also referred to as a Behavioral simulation in Xilinx Foundation.

A behavioral simulation is used to verify the logical behaviour of the circuit. It is important to realize that some statements in VHDL are not synthesizable and therefore included for simulation purposes only.

Consider the following example: Z <= A and B after 2ns; The after statement is an arbitrary delay that cannot be realized in hardware, thus it is not synthesizable. It is included to model expected delays in a behavioral simulation.

STEP 3 - Synthesis

During synthesis, the CAD tool will interpret your VHDL design information and infer standard building blocks to implement your design (registers, multiplexers, lookup tables, adders, etc.). Subtle differences in your VHDL description can result in different hardware being inferred at this stage. Different hardware inferences will result in variances in system performance.

STEP 4 – Implementation

The Xilinx implementation process takes your design through to TRANSLATE, MAP, and PLACE AND ROUTE sub-processes. The TRANSLATE process convert the netlist generated from the synthesis process, into a form specific to the target device. The MAP process translates the standard building blocks into the specific resources available in the target hardware. The PLACE & ROUTE process picks up where the MAP process leaves off by allocating specific resources (placing) and interconnecting (routing) the placed design. At the end of this process you can perform a post-place and route simulation. This is the most accurate simulation available through the Xilinx toolset. It will give you an indication of what to expect of your design once it is actually implemented.

STEP 5 – Device Configuration

After the design has been verified, a binary hardware configuration file is generated (bitstream). This file is then downloaded into the FPGA via the JTAG interface.

Q10) Explain data types and objects?

A10) Data Objects:

A data objects hold the value of specified type, which is created by means of an object declaration.

In the following example signal is one of the type of data object.

e.g. signal sl: std- logic

Type of data objects:

(i) Constant

(ii) File

(iii) Variable

(iv) Signals

Constant

A constant is an object whose value may never be changed during the simulation process. The constant declaration contains one or more identifiers. The Syntax of constant is,

constant constant_name : type := value;

Example :

constant width: integer:= 8;

constant x: std_logic:= 16;

constant delay: time:= 10ns;

File

A sequence of value called file. The value can be read or write to file using read procedures and write procedures respectively. The Syntax of file is :

file identifier : subtype_indication [ file_open_information ];

Example :

type IntegerFile is file of INTEGER;

file F1: IntegerFile;

Variables:

A variable is an object with single current value. A signal value of given type having different values assigned to different times called as variable. The Syntax of variable is,:

variable variable_name : type;

variable variable_name : type := initial_value;

Example :

variable A,B: bit;

variable sum : std_logic_vector(7 downto 0);

Signal

Signal is an object with a past history of values. The term signal refers to objects declared by signal declarations and port declarations. The Syntax of signal is :

signal signal_name : type;

signal signal_name : type := initial_value;

Example 1 :

signal A,B: std_logic;

signal DELAY: time:=10ns;

Example 2 :

entity testing is

port (A,B: in Std_Logic;

C: out Std_logic);

end entity VK;

architecture Ex_testing of testing is

signal Temp : Std_Logic;

begin

Temp<= A xor B;

C<= not Temp;

end architecture Ex_testing;

Data Types:

VHDL has a set of standard data types (predefined / built-in).

Some of the predefined data types in VHDL are: BIT, BOOLEAN and INTEGER.

The STD_LOGIC and STD_LOGIC_VECTOR data types are not built-in VHDL data types but are defined in the standard logic 1164 package of the IEEE library. We therefore need to include this library in our VHDL code and specify that the STD_LOGIC_1164 package must be used in order to use the STD_LOGIC data type:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

BIT

The BIT data type that has value 0 or 1. When assigning a value of 0 or 1 to a BIT in VHDL code, the 0 or 1 must be enclosed in single quotes: '0' or '1'.

BIT_VECTOR

The BIT_VECTOR data type is the vector version of the BIT type consisting of two or more bits. Each bit in a BIT_VECTOR can only have the value 0 or 1.

When assigning a value to a BIT_VECTOR, the value must be enclosed in double quotes, e.g. "1011" and the number of bits in the value must match the size of the BIT_VECTOR.

STD_LOGIC

The STD_LOGIC data type can have the value X, 0, 1 or Z. There are other values that this data type can have, but the other values are not synthesizable – i.e. they can not be used in VHDL code that will be implemented on a CPLD or FPGA.

These values have the following meanings:

When assigning a value to a STD_LOGIC data type, the value must be enclosed in single quotes: 'X', '0', '1' or 'Z'.

STD_LOGIC_VECTOR

The vector version of the STD_LOGIC data type. Each bit in the set of bits that make up the vector can have the value X, 0, 1 or Z.

When assigning a value to a STD_LOGIC_VECTOR type, the value must be enclosed in double quotes, e.g. "1010", "ZZZZ" or "ZZ001". The number of bits in the value must match the size of the STD_LOGIC_VECTOR.