|

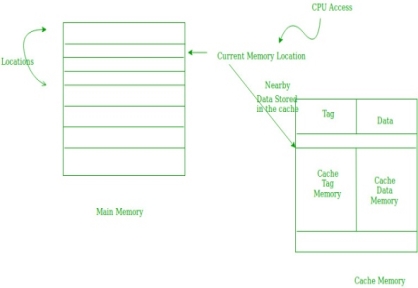

memory locations indexing from 0 to where l is the address buses. We can describe the memory in terms of the bytes using the following formula:Where,

memory locations indexing from 0 to where l is the address buses. We can describe the memory in terms of the bytes using the following formula:Where,l is the total address busesN is the memory in bytesFor example, some storage can be described below in terms of bytes using the above formula:

1kB= 210 Bytes 64 kB = 26 x 210 Bytes = 216 Bytes 4 GB = 22 x 210(kB) x 210(MB) x 210 (GB) = 232 Bytes |

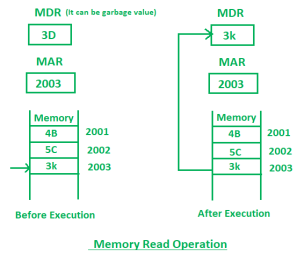

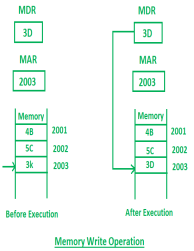

Memory Data Register (MDR) is the data register which is used to store the data on which the operation is being performed.

|

|

|

|

|

|

|

|

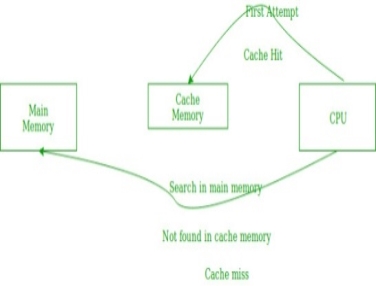

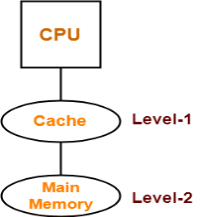

Hit + Miss = Total CPU Reference Hit Ratio(h) = Hit / (Hit+Miss) |

Tavg = Average time to access memory Tavg = h * Tc + (1-h)*(Tm + Tc) |

|

|

|

Important Note In any memory organization,

|

Average cost per byte of the memory = { C1 x S1 + C2 x S2 } / { S1 + S2 } |

|

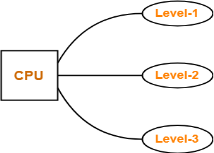

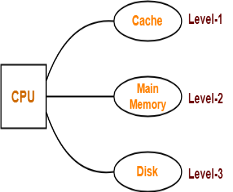

Let-

|

Average time required to access memory per operation = H1 x T1 + (1 – H1) x H2 x T2 + (1 – H1) x (1 – H2) x H3 x T3 = H1 x T1 + (1 – H1) x H2 x T2 + (1 – H1) x (1 – H2) x 1 x T3 = H1 x T1 + (1 – H1) x H2 x T2 + (1 – H1) x (1 – H2) x T3 |

Average cost per byte of the memory = { C1 x S1 + C2 x S2 + C3 x S3 } / { S1 + S2 + S3 } |

|

Average time required to access memory per operation = H1 x T1 + (1 – H1) x H2 x (T1 + T2) = H1 x T1 + (1 – H1) x 1 x (T1 + T2) = H1 x T1 + (1 – H1) x (T1 + T2) |

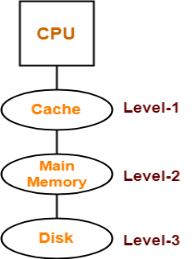

|

Average time required to access memory per operation = H1 x T1 + (1 – H1) x H2 x (T1 + T2) + (1 – H1) x (1 – H2) x H3 x (T1 + T2 + T3) = H1 x T1 + (1 – H1) x H2 x (T1 + T2) + (1 – H1) x (1 – H2) x 1 x (T1 + T2 + T3) = H1 x T1 + (1 – H1) x H2 x (T1 + T2) + (1 – H1) x (1 – H2) x (T1 + T2 + T3) |

Average cost per byte of the memory = { C1 x S1 + C2 x S2 + C3 x S3 } / { S1 + S2 + S3 } |

|

Average memory access time = H1 x T1 + (1 – H1) x H2 x T2 = 0.8 x 5 ns + (1 – 0.8) x 1 x 100 ns = 4 ns + 0.2 x 100 ns = 4 ns + 20 ns = 24 ns |

|

Average memory access time = H1 x T1 + (1 – H1) x H2 x (T1 + T2) = 0.8 x 5 ns + (1 – 0.8) x 1 x (5 ns + 100 ns) = 4 ns + 0.2 x 105 ns = 4 ns + 21 ns = 25 ns |

|

Effective memory access time = H1 x T1 + (1 – H1) x H2 x T2 + (1 – H1) x (1 – H2) x H3 x T3 = 0.9 x 10 ns + (1 – 0.9) x 0.8 x 100 ns + (1 – 0.9) x (1 – 0.8) x 1 x 10000 ns = 9 ns + 8 ns + 200 ns = 217 ns |

|

Effective memory access time = H1 x T1 + (1 – H1) x H2 x (T1 + T2) + (1 – H1) x (1 – H2) x H3 x (T1 + T2 + T3) = 0.9 x 10 ns + (1 – 0.9) x 0.8 x (10 ns + 100 ns) + (1 – 0.9) x (1 – 0.8) x 1 x (10 ns + 100 ns + 10000 ns) = 9 ns + 8.8 ns + 202.2 ns = 220 ns |

|

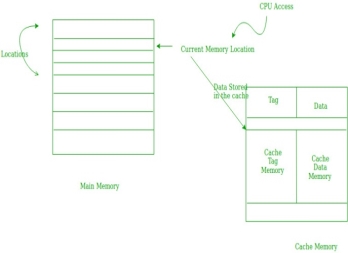

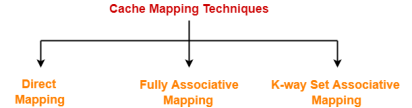

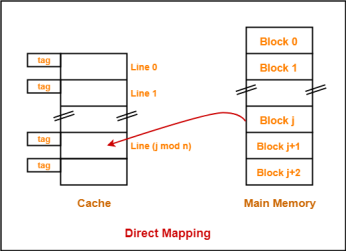

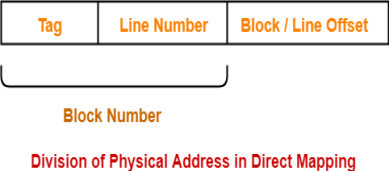

Cache line number = (Main Memory Block Address) Modulo (Number of lines in Cache) |

|

|

|

|

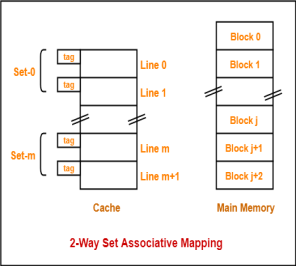

Cache set number = (Main Memory Block Address) Modulo (Number of sets in Cache) |

|

|

1-way Set Associative Mapping ≡ Direct Mapping |